LT3045

LT3045

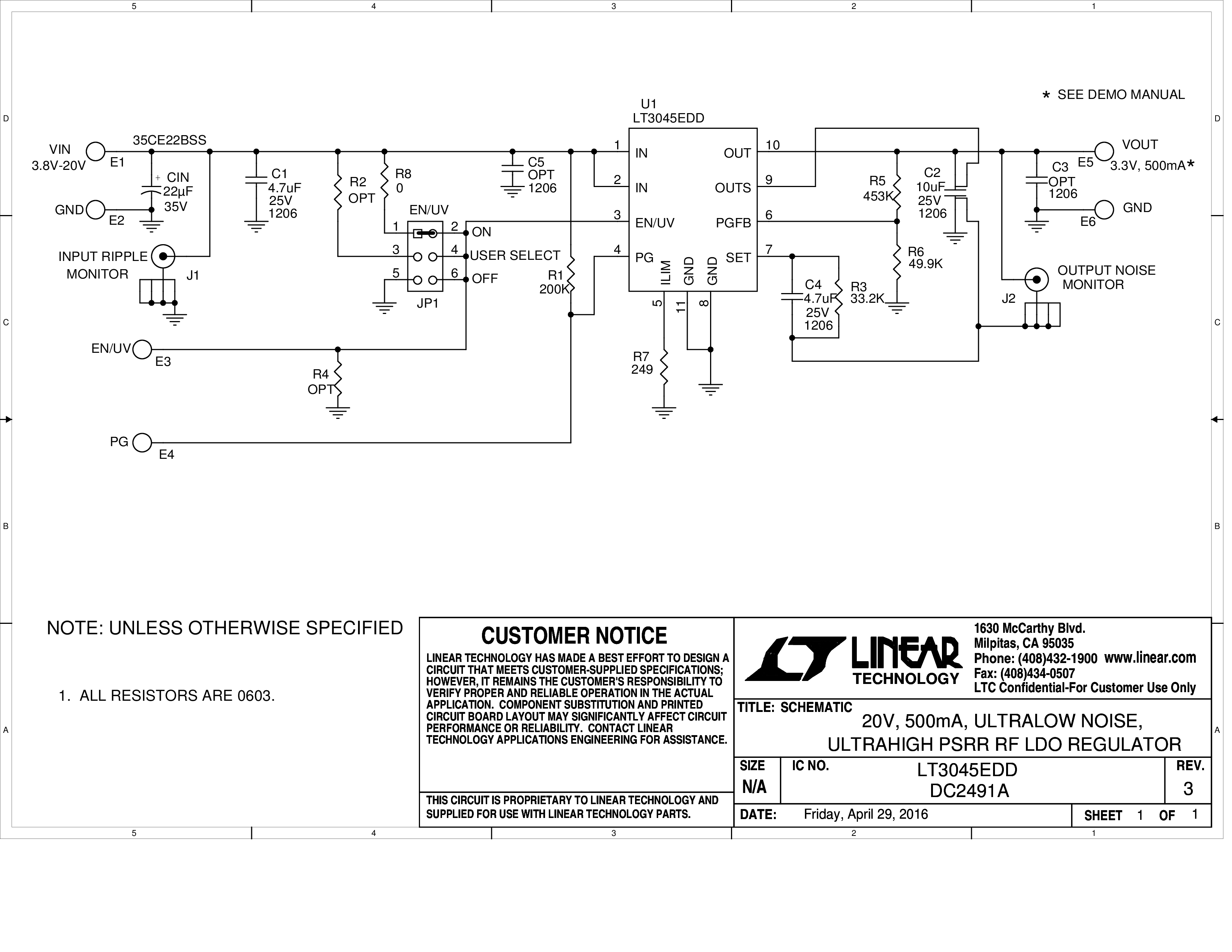

新規設計に推奨20V、500mA、超低ノイズ、超高PSRRのリニア・レギュレータ

- 製品モデル

- 21

- 1Ku当たりの価格

- 最低価格:$3.37

Viewing:

製品の詳細

- 超低RMSノイズ:0.8µVRMS(10Hz ~100kHz)

- 超低スポット・ノイズ:2nV/√Hz(10kHz時)

- 超高PSRR:76dB(1MHz)

- 出力電流:500mA

- 広い入力電圧範囲:1.8V~20V

- 1個のコンデンサでノイズとPSRRを改善

- 100µAのSETピン電流:初期精度±1%

- 1本の抵抗で出力電圧を設定

- 広い帯域幅:1MHz

- 設定可能な電流制限

- 低ドロップアウト電圧:260mV

- 出力電圧範囲:0V~15V

- 設定可能なパワーグッド

- 高速起動機能

- 高精度のイネーブル/UVLO

- 低ノイズ化および大電流化のため並列接続可能

- フォールドバック特性の内部電流制限

- 出力コンデンサの最小値:10µF(セラミック)

- バッテリ逆接続保護および逆方向電流保護

- 12ピンMSOPおよび10ピン3mm × 3mm DFNパッケージ

- オートモーティブ・アプリケーション用にAEC-Q100に適合

-

LT3045-EPは防衛&航空宇宙用途に対応(AQEC規格)

- LT3045-EPデータ・シート (pdf)がダウンロード可能

- ミリタリ温度範囲(−55°C~150°C)

- 管理された製造ベースライン

- 1つの組み立て/テスト・サイト

- 1つのファブ・サイト

- 製品変更通知

- 要求に応じて利用可能な認証データ

- V62/21614データシート

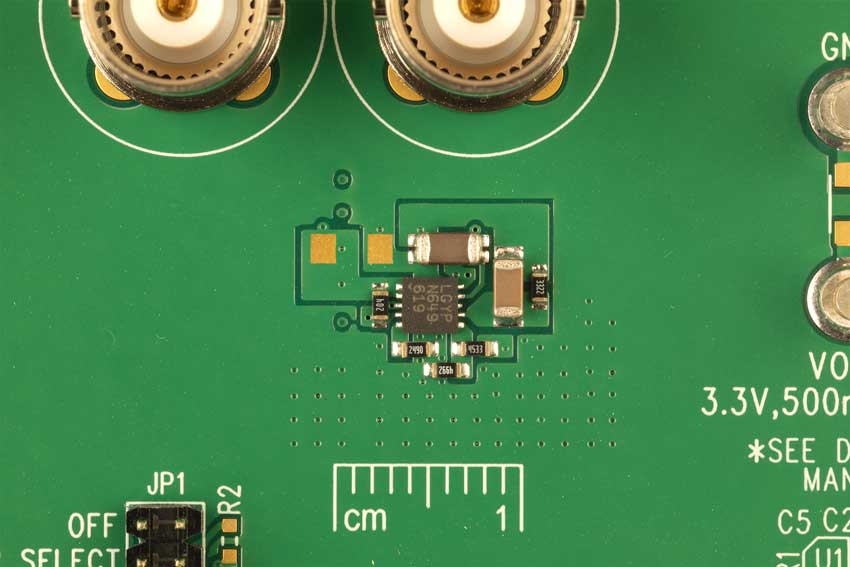

LT3045は高性能の低ドロップアウト・リニア・レギュレータで、超低ノイズおよび超高PSRRアーキテクチャを特長としており、ノイズの影響を受けやすいアプリケーションの電力供給に対応します。後段に高性能の電圧バッファがある高精度の電流リファレンスとして設計されているので、LT3045は並列接続が容易であり、ノイズの低減、出力電流の増大、PCB上での熱放散を更に向上することができます。

このデバイスは、標準で260mVのドロップアウト電圧のとき500mAを供給します。動作中の静止電流は公称2.2mAで、シャットダウン時は1μAよりはるかに小さくなります。LT3045は出力電圧範囲が広い(0V~15V)上にユニティ・ゲイン動作を維持するので、設定出力電圧に関係なく、出力ノイズ、PSRR、帯域幅、負荷レギュレーションがほぼ一定になります。更に、このレギュレータは、設定可能な電流制限、高速起動機能、および設定可能なパワーグッドによる出力電圧レギュレーションの表示といった特長も備えています。

LT3045は最小10μFのセラミック出力コンデンサで安定します。内蔵の保護回路には、逆バッテリ保護回路、逆方向電流保護回路、フォールドバック特性の内部電流制限回路、およびヒステリシスのある熱制限回路があります。LT3045は、放熱特性が優れた12ピンMSOPパッケージおよび10ピン3mm×3mm DFNパッケージで供給されます。

LT3045-EPは防衛&航空宇宙用途に対応しています(AQEC規格)

| VIOC Function | |

| LT3045-1 | Yes |

| LT3045 | No |

アプリケーション

- RF電源:PLL、VCO、ミキサ、LNA、PA

- 超低ノイズの計測装置

- 高速/高精度データ・コンバータ

- 医療用アプリケーション:撮像、診断

- 高精度電源

- スイッチング電源のポスト・レギュレータ

ドキュメント

データシート 5

信頼性データ 1

ユーザ・ガイド 2

アプリケーション・ノート 1

デザイン・ノート 3

技術記事 5

サードパーティ・ソリューション 2

ソリューション・カタログ 3

製品セレクタ・カード 1

プレス・リリース 1

Book & eBook 1

Analog Dialogue 2

珍問/難問集 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| LT3045EDD#PBF | 10-Lead DFN (3mm x 3mm w/ EP) | ||

| LT3045EDD#TRPBF | 10-Lead DFN (3mm x 3mm w/ EP) | ||

| LT3045EMSE#PBF | 12-Lead MSOP w/ EP | ||

| LT3045EMSE#TRPBF | 12-Lead MSOP w/ EP | ||

| LT3045EMSE#WPBF | 12-Lead MSOP w/ EP | ||

| LT3045EMSE#WTRPBF | 12-Lead MSOP w/ EP | ||

| LT3045HDD#PBF | 10-Lead DFN (3mm x 3mm w/ EP) | ||

| LT3045HDD#TRPBF | 10-Lead DFN (3mm x 3mm w/ EP) | ||

| LT3045HMSE#PBF | 12-Lead MSOP w/ EP | ||

| LT3045HMSE#TRPBF | 12-Lead MSOP w/ EP | ||

| LT3045HMSE#WPBF | 12-Lead MSOP w/ EP | ||

| LT3045HMSE#WTRPBF | 12-Lead MSOP w/ EP | ||

| LT3045HMSE#Z-EP | 12-Lead MSOP w/ EP | ||

| LT3045IDD#PBF | 10-Lead DFN (3mm x 3mm w/ EP) | ||

| LT3045IDD#TRPBF | 10-Lead DFN (3mm x 3mm w/ EP) | ||

| LT3045IMSE#PBF | 12-Lead MSOP w/ EP | ||

| LT3045IMSE#TRPBF | 12-Lead MSOP w/ EP | ||

| LT3045IMSE#WPBF | 12-Lead MSOP w/ EP | ||

| LT3045IMSE#WTRPBF | 12-Lead MSOP w/ EP | ||

| LT3045MPDD#PBF | 10-Lead DFN (3mm x 3mm w/ EP) | ||

| LT3045MPDD#TRPBF | 10-Lead DFN (3mm x 3mm w/ EP) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

2 4, 2020 - 20_0129 Laser Mark Conversion for 12-Lead MSOP Packages Assembled in ADPG and UTAC |

||

| LT3045EMSE#PBF | 製造中 | |

| LT3045EMSE#TRPBF | 製造中 | |

| LT3045HMSE#PBF | 製造中 | |

| LT3045HMSE#TRPBF | 製造中 | |

| LT3045IMSE#PBF | 製造中 | |

| LT3045IMSE#TRPBF | 製造中 | |

|

6 21, 2022 - 22_0050 UTAC Thai Limited (UTL) as Alternate Assembly Site for MSOP Packages / Devices |

||

| LT3045HMSE#WPBF | 製造中 | |

| LT3045HMSE#WTRPBF | 製造中 | |

| LT3045IMSE#WPBF | 製造中 | |

| LT3045IMSE#WTRPBF | 製造中 | |

|

11 29, 2021 - 20_0066 Discontinuation of Sn/Pb Plated Lead Finish Parts for MSOP Package |

||

| LT3045HMSE#Z-EP | 製造中 | |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

必要なソフトウェア/ドライバが見つかりませんか?

ドライバ/ソフトウェアをリクエストハードウェア・エコシステム

ツールおよびシミュレーション

LTspice 1

下記製品はLTspiceで使用することが出来ます。:

- LT3045

- LT3045-1

LTspice®は、無料で提供される強力で高速な回路シミュレータと回路図入力、波形ビューワに改善を加え、アナログ回路のシミュレーションを容易にするためのモデルを搭載しています。