資料ライブラリ

アプリケーション・ノート使用上の注意

本アプリケーションノートの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、リビジョンが古い場合があります。最新の内容については、必ず最新の英語版をご参照ください。

なお、日本語版のアプリケーションノートは基本的に「Rev.0」(リビジョン0)で作成されています。

AN-581: 単電源アプリケーションでのオペアンプのバイアスとデカップリング

単電源または両電源のいずれが適切か?

車載装置や船舶装置などのバッテリ駆動オペアンプ・アプリケーションでは、電源として単電源のみが使用可能です。コンピュータなどのその他のアプリケーションでは、AC 電源ラインで動作することができますが、5 V や12 V のような単極DC 電源のみの場合もあります。したがって、単極電源でオペアンプ回路を動作させることが必要な場合もあります。単電源動作には各ステージに追加受動部品が必要となる欠点があるため、正しく実施されない場合、重大な安定性問題が発生することがあります。

抵抗バイアスでの一般的な問題

単電源アプリケーションには、通常両電源オペアンプ回路にはない固有な問題があります。基本的な問題は、オペアンプは両電源デバイスであるため、外付け部品を使ったある種のバイアスが必要であり、オペアンプ出力電圧の中心を電源中心に設定する必要があることです。これにより、与えられた電源電圧に対して入力と出力の電圧振幅を最大にすることができます。

低ゲイン・アプリケーションによっては、入力信号が非常に小さい場合、オペアンプ出力を2 V または3 V しかグラウンドより持ち上げることができませんが、大部分の場合、すべてのクリッピングを回避するために、出力をほぼ電源中心にする必要があります。

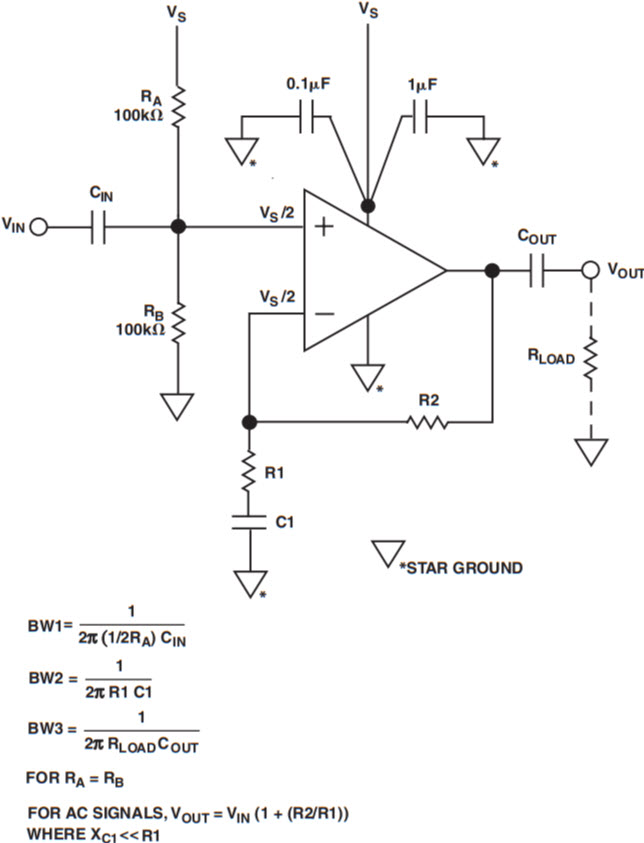

図1 の回路にシンプルな単電源バイアス方法を示します。この非反転AC 結合アンプ回路では2 本のバイアス抵抗RA とRB による抵抗分圧器を使って、非反転での電圧をVS/2 に設定しています。図示のように、入力信号VIN は非反転入力端子に容量結合されています。

図1.不安定になる恐れのある単電源オペアンプ回路

このシンプルな回路には深刻な制約があります。1 つ目はオペアンプの電源除去比が悪いため、電源電圧が変化すると、抵抗分圧器により設定されたVS/2 のバイアス電圧が直接変化することです。電源除去比(PSR)はよく見落されますが、非常に重要なオペアンプ特性です。

電源ラインが1V 変化すると、分圧器出力で1/2V 変化するため、回路のPSR は6 dB と低い値です。このため、新しいオペアンプが提供する高い電源除去比では、AC 信号(さらに電源ハム)が電源ラインを経由してオペアンプに混入することはなくなりました。

さらに悪いことには、不安定性は負荷に大きな出力電流を供給するオペアンプを持つ回路で多く発生します。電源が安定化されていないと(またバイパスも行われていないと)、電源ラインに大きな信号電圧が現れます。電源ラインを直接リファレンスにしているオペアンプの非反転入力では、これらの信号が直接オペアンプに戻されて、他の不安定性の原因になります。

注意深いレイアウト、多くのコンデンサによる電源バイパス、星型グラウンド、プリント回路ボードの“パワー・プレーン”により、回路は安定になりますが、デザインの電源除去比を適切にすることの方が遥かに容易です。

バイアス回路の電源デカップリング

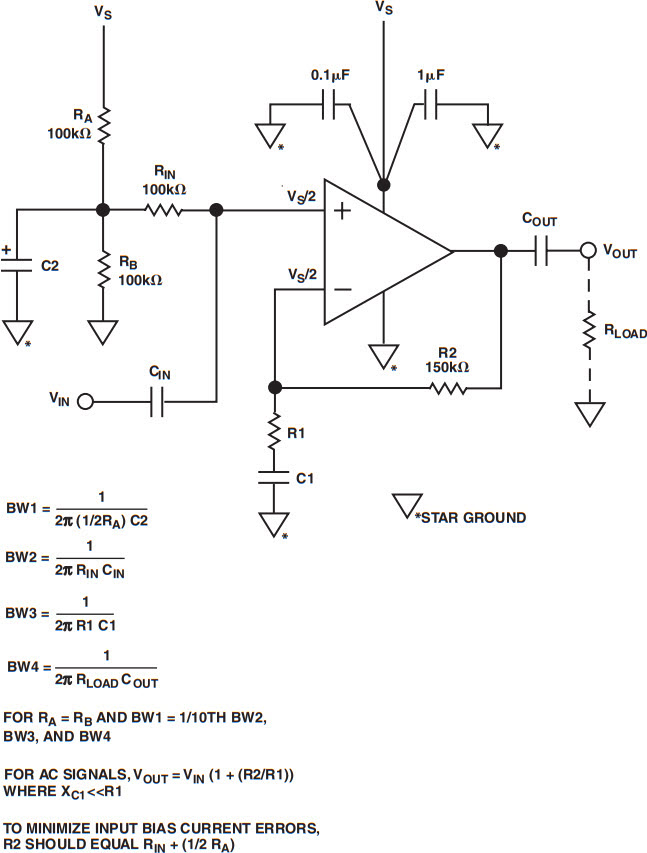

図 2 に示すように回路を変更することが解決策になります。分圧器のタップ・ポイントはコンデンサC2 によりAC 信号がバイパスされるようになるため、AC のPSR が回復されます。抵抗RINはVS/2 リファレンス電圧のDC リターン・パスを提供し、回路のAC 入力インピーダンスも設定します。

図2.単電源オペアンプ・バイアス回路のデカップリング

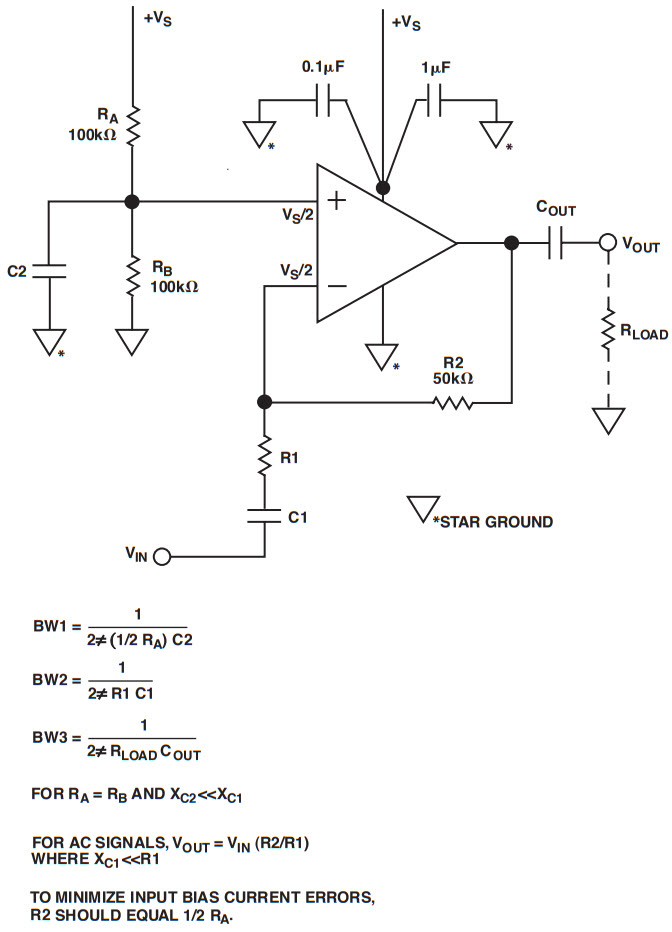

多くの公開されたアプリケーション回路では、RA とRB の分圧器に100 kΩ/100 kΩ を、C2 には0.1 μF または同等の容量値を、それぞれ使用していますが、この回路の–3 dB 帯域幅はRAおよびRBとコンデンサC2 との並列組み合わせにより設定され、次のようになります。

30 Hz 以下の周波数に対してこの回路は電源除去比を持っていないため、その他の不安定性もまだ発生します。したがって、電源ライン上に30 Hz 以下の信号があると、オペアンプの+入力に容易に混入します。

この問題に対する実用的なソリューションは、コンデンサC2 の値を大きくすることです。回路の通過帯域内のすべての周波数で分圧器を効果的にバイパスするために十分大きな値にする必要があります。経験則としては、この極を–3 dB 入力帯域幅の1/10に設定することです(RIN/CINとR1/C1 により設定)。

DC 回路ゲインは1 であることに注意してください。この場合でも、オペアンプの入力バイアス電流を考慮する必要があります。RA/RB 分圧器によりオペアンプの正入力端子に直列に大きな抵抗が追加され、この値は2 本の抵抗の並列組み合わせになります。オペアンプ出力を電源中心付近に維持するためには、-入力端子の抵抗を同じ値だけ大きくして、この抵抗を“バランス”させることが必要です。電流帰還オペアンプでは入力バイアス電流が等しくないことがあり、これによりデザインが複雑になることがあります。

このため、入力バイアス電流誤差、電源除去比、ゲイン、入力、出力回路帯域幅などを考慮した単電源オペアンプ回路のデザインでは、多くのことが関係します。ただし、“クックブック”手法を使うことによりデザインを大幅に簡略化することができます。15 V または12 V の単電源で動作する一般的な電圧帰還オペアンプでは、2 本の100 kΩ 抵抗を使う抵抗分圧器が、消費電流と入力バイアス電流誤差との間の合理的な妥協点となります。5 V 電源の場合、抵抗を42 kΩ のような小さい値に減らすことができます。最後に、幾つかのアプリケーションは、新しい3.3 V 標準で動作する必要があります。3.3 V アプリケーションの場合、オペアンプが“レールto レール”デバイスであり、かつ電源中心の非常に近くにバイアスされている必要があります。バイアス抵抗値は、さらに約27 kΩ にまで小さくすることができます。

電流帰還オペアンプは一般に高周波用途にデザインされ、R2 と浮遊容量で形成されるローパス・フィルタにより回路の3 dB 帯域幅が大幅に減少させられることに注意してください。このため、電流帰還オペアンプは通常、R2 に対して非常に小さい抵抗値を使います。ビデオ速度のアプリケーション向けにデザインされたAD811 のようなオペアンプは、R2 に1kΩ の抵抗を使う最適性能を持っています。したがって、これらのタイプのアプリケーションでは、RA/RB 分圧器にさらに小さい抵抗値を使って入力バイアス電流誤差を小さくする必要があります。

バイポーラ・デバイスの代わりに新しいFET 入力オペアンプを使うと、非常に広い温度範囲で回路動作が必要とされない限り、入力バイアス電流誤差を大幅に減らすことができます。この場合にも、オペアンプ入力端子での抵抗のバランシングが必要です。

表I に、様々なゲインと3 dB 帯域幅に対して、図2 の回路部品値(typ)を示します。

| Gain | Input BW (Hz) | Output BW (Hz) | CIN* (μF) | R1 (kΩ) | C1* (μF) | C2 (μF) | COUT (μF) | RLOAD (kΩ) |

| 10 | 10 | 10 | 0.3 | 16.5 | 1.5 | 3 | 0.2 | 100 |

| 20 | 10 | 10 | 0.3 | 7.87 | 3 | 3 | 0.2 | 100 |

| 10 | 50 | 50 | 0.1 | 16.5 | 0.3 | 0.6 | 0.05 | 100 |

| 101 | 20 | 20 | 0.2 | 1.5 | 6.8 | 2 | 0.1 | 100 |

| *容量値は、最寄りの一般的な値に切り上げ処理しています。CIN/RIN極とC1/R1極は同じ周波数で、両方とも入力BWに影響を与えるため、各コンデンサは単極RC結合入力の場合の値より√2大きくなっています。C2は、コーナー周波数が入力BWの1/10になるように選択しています。 | ||||||||

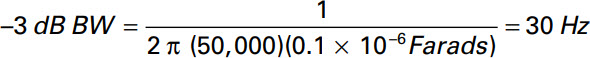

表II に、様々なゲインと3 dB 帯域幅に対して、回路部品値(typ)を示します。

| Gain | Input BW (Hz) | Output BW (Hz) | R1 (kΩ) | C1* (μF) | C2* (μF) | COUT (μF) | RLOAD (kΩ) |

| 10 | 10 | 10 | 2 | 8.2 | 0.5 | 0.2 | 100 |

| 20 | 10 | 10 | 1 | 20 | 0.5 | 0.2 | 100 |

| 10 | 50 | 50 | 2 | 2 | 0.1 | 0.05 | 100 |

| 100 | 20 | 20 | 1 | 8.2 | 0.3 | 0.1 | 100 |

| *容量値は、最寄りの一般的な値に切り上げ処理しています。C1/R1極とC2/RA/RB極は同じ周波数で、両方とも入力BWに影響を与えるため、各コンデンサは単極RC結合入力の場合の値より√2大きくなっています。 | |||||||

図3 に、反転アンプについて図2 と同じ回路を示します。

図3.単電源反転アンプ回路のデカップリング

ツェナー・ダイオードによるバイアス

抵抗分圧器によるバイアス技術は低価格で、常にオペアンプ出力電圧をVS/2 に維持しますが、オペアンプの同相モード除去比がRA/RBとコンデンサC2 で構成されるRC 時定数に完全に依存します。入力RC 結合回路(R1/C1 とRIN/CIN)のRC 時定数の少なくとも10 倍を実現するC2 値を使うと、適切な同相モード除去比の実現に役立ちます。RA とRBを100 kΩ にすると、回路帯域幅が狭くなり過ぎないかぎり、C2 の実際の値をかなり小さくすることができますが、単電源動作に対して必要なVS/2 バイアスを提供するもう1 つの方法は、ツェナー・ダイオード・レギュレータを使う方法です。図4 にこの方式を示します。ここでは、電流が抵抗RZ を介してツェナーへ流れます。コンデンサCNは、ツェナーから発生するノイズがオペアンプへ混入するのを防止するのに役立っています。低ノイズ回路では、指定の10 μF より大きいCNの値を使う必要がある場合があります。

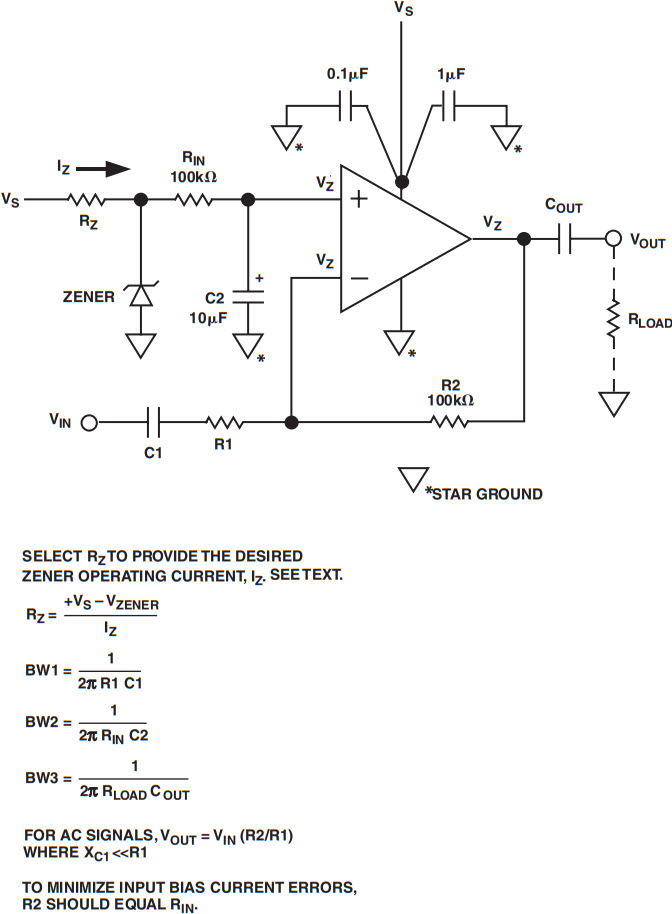

図4. ツェナー・ダイオード・バイアスを使った非反転単電源アンプ

VS/2 に近い動作電圧を持つツェナーを選択する必要があります。抵抗RZ は、ツェナーが安定な定格電圧で動作し、ツェナー出力ノイズを小さく維持するために十分なツェナー電流を提供するように選択する必要があります。また、消費電力(発熱)を小さくして、ツェナー寿命を長くすることも重要です。オペアンプ入力電流は実質的にゼロであるため、低消費電力のツェナーを選択することができます。250 mW のデバイスが最適ですが、さらに一般的な500 mW タイプも使用できます。理論的なツェナー電流は各メーカ毎に変わりますが、5 mA (250 mW ツェナー)~5 μA (500mW ツェナー)の実際のIZ レベルがこのアプリケーションでは許容範囲になります。

ツェナーの動作限界内で、図4 の回路はオペアンプの電源除去比を取り戻します。しかし、この場合、オペアンプ出力はVS/2 ではなくツェナー電圧になってしまいます。電源電圧が低下すると、大きな信号で非対称なクリッピングが発生します。さらに、回路の消費電力が大きくなります。最後に、入力バイアス電流も依然考慮する必要があります。入力バイアス電流から大きなオフセット電圧誤差が発生しないようにするため、抵抗RINとR2 を同じ値に近づける必要があります。

図5 に、同じツェナー・バイアス方法を使った反転アンプ回路を示します。

図5. ツェナー・ダイオード・バイアスを使った反転単電源アンプ

表III は、回路4 と回路5 で一般的なツェナー・ダイオードと組み合わせて使用するRZ 抵抗値を求めるために使うことができます。回路ノイズを最小にするためには、ツェナー製品のデータ・シートを参照して、最適ツェナー電流を選択する必要があることに注意してください。

| Supply Voltage (V) | Zener Voltage (V) | Zener Type | Zener Current IZ | RZ Value (Ω) |

| +15 | 7.5 | 1N4100 | 500 µA | 15 k |

| +15 | 7.5 | 1N4693 | 5 mA | 1.5 k |

| +12 | 6.2 | 1N4627 | 500 µA | 11.5 k |

| +12 | 6.2 | 1N4691 | 5 mA | 1.15 k |

| +9 | 4.3 | 1N4623 | 500 µA | 9.31 k |

| +9 | 4.3 | 1N4687 | 5 mA | 931 |

| +5 | 2.4 | 1N4617 | 500 µA | 5.23 k |

| +5 | 2.7 | 1N4682 | 5 mA | 464 |

表IV と表V に、様々な回路ゲインと帯域幅に対する図4 と図5の実用的部品値を示します。

| Gain | Input BW (Hz) | Output BW (Hz) | CIN* (μF) | R1 (kΩ) | C1* (μF) | COUT (μF) | RLOAD (kΩ) |

| 10 | 10 | 10 | 0.3 | 11.0 | 2 | 0.2 | 100 |

| 20 | 10 | 10 | 0.3 | 5.23 | 4.7 | 0.2 | 100 |

| 10 | 50 | 50 | 0.1 | 11.0 | 0.47 | 0.05 | 100 |

| 101 | 20 | 20 | 0.2 | 1.0 | 15 | 0.1 | 100 |

| *容量値は、最寄りの一般的な値に切り上げ処理しています。CIN/RIN極とC1/R1極は同じ周波数で、両方とも入力BWに影響を与えるため、各コンデンサは単極RC結合入力の場合の値より√2大きくなっています。 | |||||||

| Gain | Input BW (Hz) | Output BW (Hz) | R1 (kΩ) | C1* (μF) | C2* (μF) | COUT (μF) | RLOAD (kΩ) |

| 10 | 10 | 10 | 10 | 2.7 | 0.2 | 0.2 | 100 |

| 20 | 10 | 10 | 5 | 4.7 | 0.2 | 0.2 | 100 |

| 10 | 50 | 50 | 10 | 0.5 | 0.05 | 0.05 | 100 |

| 100 | 20 | 20 | 1 | 12 | 0.1 | 0.1 | 100 |

| *容量値は、最寄りの一般的な値に切り上げ処理しています。C2/RIN極とC1/R1極は同じ周波数で、両方とも入力BWに影響を与えるため、各コンデンサは単極RC結合入力の場合の値より√2大きくなっています。 | |||||||

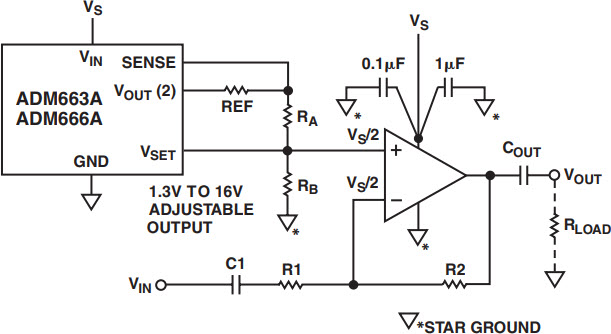

リニア電圧レギュレータを使ったオペアンプ・バイアス

新しい 3.3 V 標準で動作するオペアンプ回路の場合、1.65 V のバイアス電圧が必要です。一般に、低い電圧のツェナー・ダイオードは2.4 V までしか提供されていません。このバイアス電圧を提供する最も容易な方法は、ADM663A デバイスまたはADM666Aデバイスのようなリニア電圧レギュレータを使う方法です。この場合を図6 に示します。

図6.リニア電圧レギュレータを使ったオペアンプ単電源バイアス回路

ツェナー・ダイオードは最も安価な電圧レギュレータですが、リニア電圧レギュレータはツェナーより小さい温度ドリフトを提供し、さらにノイズも小さくなっています。

抵抗RAとRBは、VS/2 のリファレンス電圧を提供するように選択されます。AD663A データシートを参照してください。

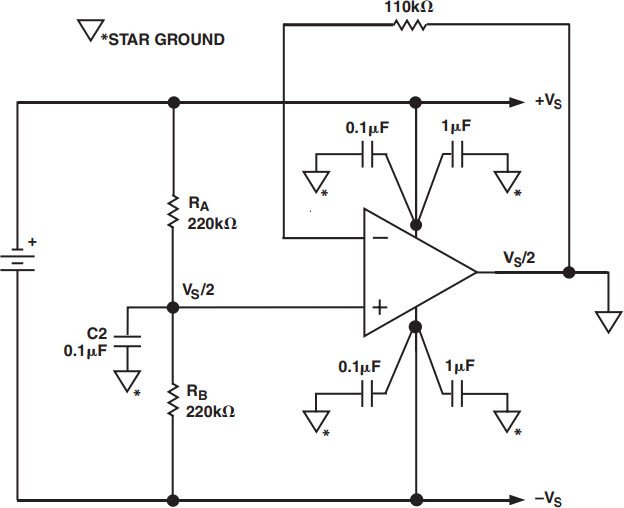

DC結合のバッテリー駆動回路

ここまでは、AC 結合のオペアンプ回路のみを説明しました。入力と出力に大きな結合コンデンサを使用しますが、AC 結合回路は非常に低い1 Hz 以下の周波数まで動作することができ、アプリケーションによっては真のDC 応答を必要とする場合もあります。

バッテリ駆動アプリケーションでは図7 に示す“仮想グラウンド”回路の使用が可能です。この回路は1 個のバッテリで、グラウンドを基準とした正と負の両電源電圧を提供します。オペアンプを使って、VS/2 分圧器出力をバッファします。3.3 V のような低電圧バッテリを使用する場合、オペアンプは“レールto レール”デバイスである必要があり、この電源電圧で動作できる必要があります。また、オペアンプは負荷回路に対して十分大きな出力電流を供給できる必要があります。コンデンサC2 は分圧器出力を十分にバイパスして、抵抗ノイズがオペアンプに混入しないようにする必要があります。負荷電流が直接グラウンドに流れ、さらに信号電流がバッテリの両側から等しく流れるため、このコンデンサは電源除去比を提供する必要はありません。

図7.バッテリ駆動のDC 結合アプリケーションに対して“仮想グラウンド”を提供するために使用するオペアンプ

抵抗RAとRBは、VS/2 のリファレンス電圧を提供するように選択されます。AD663A データシートを参照してください。

ノイズ問題

オペアンプ・アプリケーションによっては、低ノイズ・アンプを必要とする場合があり、さらに低ノイズ・アンプ回路では信号パスに低抵抗値が必要になります。ジョンソン(抵抗)ノイズは、4nV と抵抗値( kΩ)の平方根との積になります。1 kΩ 抵抗のジョンソン・ノイズは4 nV/√Hz と小さいのですが、20 kΩ 抵抗では18nV/√Hz に、100 kΩ 抵抗では40 nV/√Hz に、それぞれ増加します。RA/RB 抵抗分圧器はコンデンサ(C2)でグラウンドへバイパスされていますが、これらの抵抗がオペアンプの帰還抵抗に使用できる最小値を決定し、この値が大きいほど、ジョンソン・ノイズが大きくなります。したがって、低ノイズ・アプリケーションでは、ここで指定する100 kΩ より遥かに小さいオペアンプ・バイアス抵抗値を使う必要があります。ただし、分圧器の抵抗値が小さいほど、電源電流が大きくなり、さらにバッテリ寿命が短くなります。

幸運にも、ツェナー・ダイオード・バイアス方法を使うと、大きな抵抗を使わずにVS/2 を供給することができます。ツェナーをバイパスしてノイズを回路から除去するかぎり、ノイズと電源電流を小さくすることができます。リニア電圧レギュレータの使用は、ノイズと出力インピーダンスを非常に小さくすることができるため、さらに優れています。

回路のターンオン時間の問題

考慮が必要な最後の問題は、回路ターンオン時間です。ターンオン概略時間は、使用する最小BW フィルタのRC時定数に一致します。

ここに示すすべての回路では、RA/RB、C2 分圧器回路が入力回路または出力回路の時定数より10 倍の時定数を持っています。これは回路デザインを簡素化するためです(最大3 個のRC極が入力BW を設定しているため)。また、この大きい時定数は、オペアンプの入力回路と出力回路の前にバイアス回路が“ターンオン”することなく、オペアンプ出力が正電源ラインに到達しないで0V からVS/2 へ穏やかに変化するようにすることに役立っています。ここでの表に記載する値は、R1/C1 時定数とRLOAD/COUT 時定数の1/10 に等しい3 dB コーナー周波数に対するものです。例えば、図2 のBW = 10 Hz、ゲイン= 10 の回路の場合、表I では3 dB帯域幅= 1 Hz を提供するC2 = 3 μF の使用を推奨しています。

50 KΩ ( RAとRBの並列組み合わせ)と3 μF との積は、0.15 sec のRC時定数になります。したがって、オペアンプ出力がVS/2 に安定するためには約0.15 sec を要します。入力と出力のRC回路は10 倍高速に充電されます。

回路の–3 dB 低周波帯域幅が非常に狭いアプリケーションでは、回路のターンオン時間が長くなり過ぎます。その場合は、ツェナー・バイアス方法が適しています。

| Type | Single | Dual | Quad |

| High Speed | AD8031 AD8061 AD8051 AD8063 |

AD8032 AD8062 AD8052 AD823 |

AD8054 |

| High Output | AD8591 AD8531 |

AD8592 AD8532 |

AD8594 AD8534 |

| JFET Input | AD820 | AD822 | AD824 |

| Auto Zero | AD8551 | AD8552 | AD8554 |

| Digital Trim | AD8601 | AD8602 | AD8604 |

| Low Noise | OP184 OP162 AD8605 AD8628 |

OP284 OP262 AD8606 |

OP484 OP462 AD8608 |

| Low Power | OP196 AD8541 |

OP296 AD8542 |

OP496 AD8544 |

| Precision | OP777 | OP727 | OP747 |

入力“ヘッドルーム”についての注意

低電圧動作用に特別なオペアンプがデザインされています。これらのアンプを5 V や3.3 V のような低電圧単電源で動作させる場合、入力ヘッドルームが制限されることがあります。これは、アンプの入力ステージが非対称に制限されるときに発生します。

例えば、AD8061 オペアンプは入力同相モード電圧範囲が“グラウンド” (または負電源ライン)まで伸びるようにデザインされていますが、DC 誤差の発生なし、またはデバイス帯域幅の制限なしでは、正電源電圧の内側1.8 V までしか入力を変化させることはできません。このため、このアンプを5V 単電源で動作させ、かつアンプの正入力をVS/2 (2.5 V)にバイアスした場合、入力電圧は負方向へフルに2.5 V (0 V まで)変化できますが、正方向には、1 V までしか変化できず、それより大きく変化するとクリッピングが生じます。

アンプがゲイン2.5 以上で動作する場合、これは問題にならないことに注意してください。これは入力ステージの限界に到着する前に、最大出力振幅(± 2.5 V)に到達するためです。ただし、アンプがこれより低いゲインで動作する場合は、正入力をVS/2 より低い電位にバイアスして、入力ステージの制限を対称にする必要があります。AD8061 の場合、正入力を1.5 V にバイアスすると、クリッピングなしに3 V p-p の入力振幅が可能になります。最適な単電源バイアス電圧については、個々の製品のデータ・シートを参照してください。