LTC3618

新規設計に推奨DDR終端向け、デュアル4MHz、±3A同期整流式降圧コンバータ

- 製品モデル

- 10

- 1Ku当たりの価格

- 最低価格:$4.90

製品の詳細

- DDRの電源、終端およびリファレンス

- 高効率:最大94%

- ±3Aの出力電流を供給できるデュアル出力

- 入力電圧範囲:2.25V~5.5V

- 出力電圧精度:±1%

- VTT出力電圧:最小0.5V

- シャットダウン電流:1μA以下

- VTTR = VDDQIN/2、VFB2 = VTTR

- 調整可能なスイッチング周波数:最大4MHz

- 内部補償または外部補償

- チャネル間の位相偏移を選択可能:0°/90°/180°

- VDDQの内部または外部ソフトスタート、VTTの内部ソフトスタート

- パワーグッド状態出力

- 高さの低い4mm × 4mm QFN-24およびTSSOP-24パッケージ

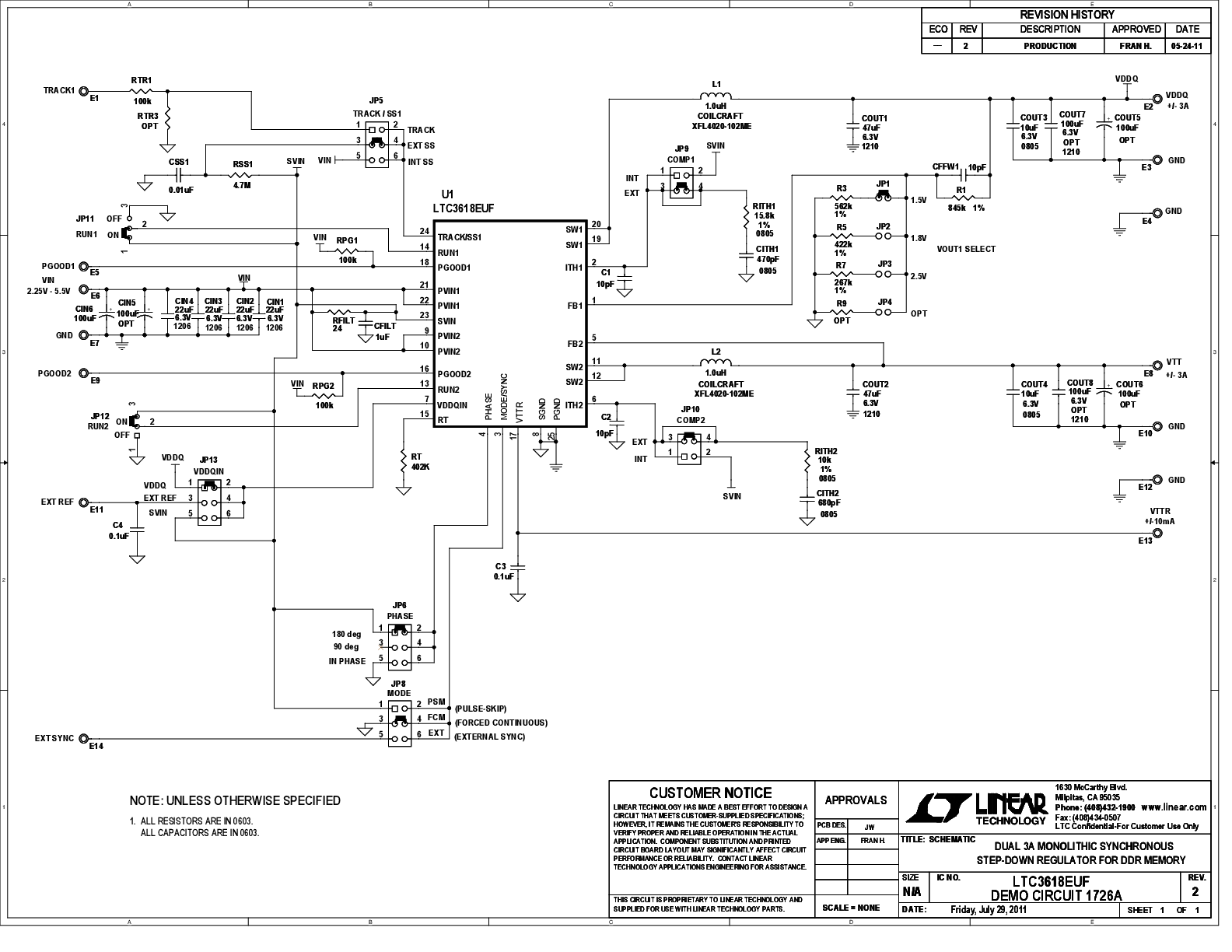

LTC3618は、電流モードの固定周波数アーキテクチャを採用したデュアル同期整流式降圧レギュレータです。入力電圧範囲が2.25V~5.5Vの完全なDDRソリューションを実現します。

第1の降圧レギュレータの出力は、高精度のVDDQ電源を供給します。バッファ付きリファレンスは、VDDQINピンの電圧の50%でVTTRピンの電圧を生成し、最大±10mAの負荷を駆動します。第2のレギュレータは、VTTRピンの電圧に等しいDDR終端電圧(VTT)を生成します。2つのレギュレータは両方とも、1MHzのスイッチング周波数で±3Aの負荷電流を供給できます。

動作周波数は最大4MHzまで外部設定可能なので、小型の表面実装インダクタを使用できます。2つのチャネル間の位相偏移を 0°、90°、180°から選択できるので、入力電流リップルを最小限に抑えます。スイッチング・ノイズの影響を受けやすいアプリケーションに対応するため、LTC3618は最大4MHzまでの外部クロックに同期可能です。

LTC3618は、4mm × 4mmの24ピン・リードレスQFNパッケージおよび熱特性が改善された24ピンTSSOPパッケージで供給されます。

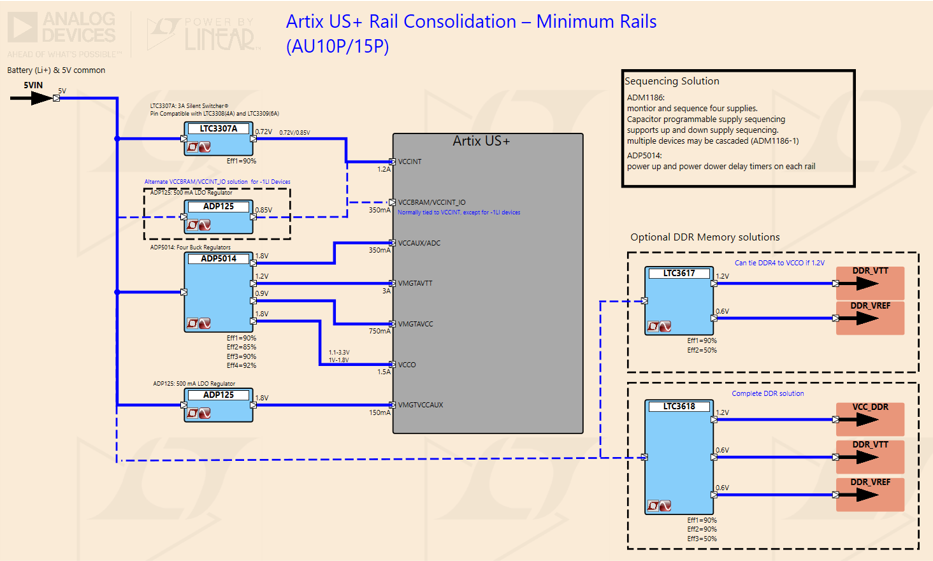

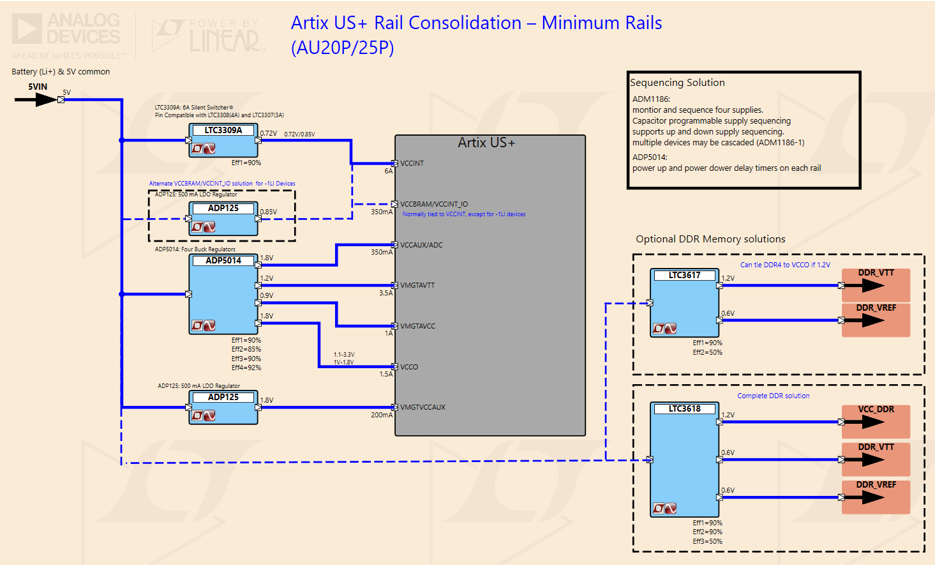

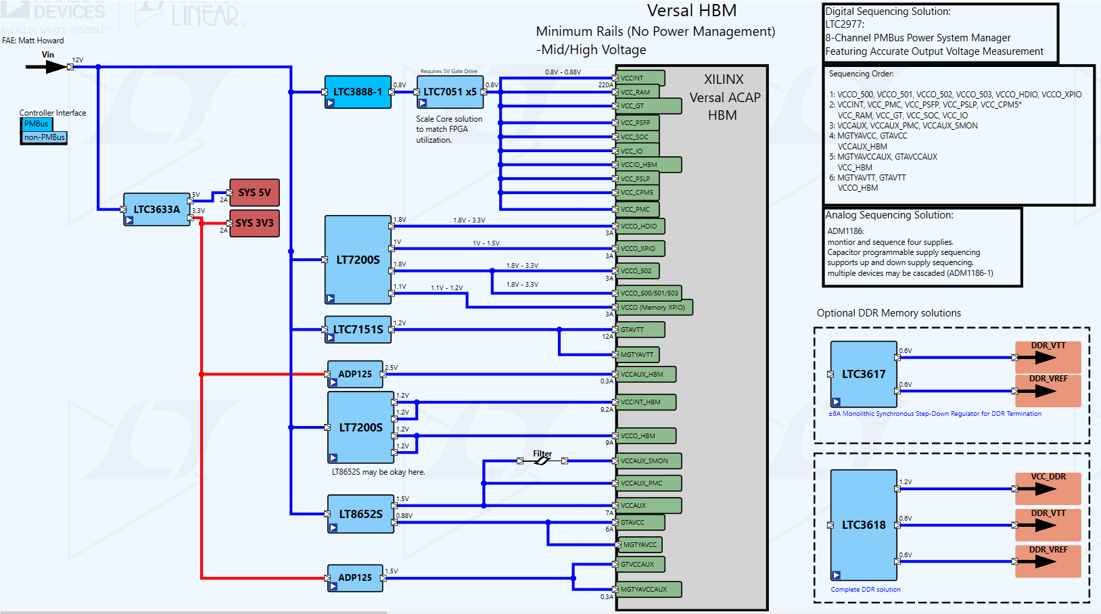

アプリケーション

- DDRメモリ

- DDR、DDR2、DDR3の各規格に対応

- トラッキング電源

ドキュメント

データシート 2

信頼性データ 1

ユーザ・ガイド 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| LTC3618EFE#PBF | 24-Lead TSSOP w/ EP | ||

| LTC3618EFE#TRPBF | 24-Lead TSSOP w/ EP | ||

| LTC3618EUF#PBF | 24-Lead QFN (4mm x 4mm x 0.75mm w/ EP) | ||

| LTC3618EUF#TRPBF | 24-Lead QFN (4mm x 4mm x 0.75mm w/ EP) | ||

| LTC3618IFE#PBF | 24-Lead TSSOP w/ EP | ||

| LTC3618IFE#TRPBF | 24-Lead TSSOP w/ EP | ||

| LTC3618IUF#PBF | 24-Lead QFN (4mm x 4mm x 0.75mm w/ EP) | ||

| LTC3618IUF#TRPBF | 24-Lead QFN (4mm x 4mm x 0.75mm w/ EP) | ||

| LTC3618IUF#WPBF | 24-Lead QFN (4mm x 4mm x 0.75mm w/ EP) | ||

| LTC3618IUF#WTRPBF | 24-Lead QFN (4mm x 4mm x 0.75mm w/ EP) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

2 14, 2025 - 25_0017 Bond Wire Change from Gold to Copper |

||

| LTC3618EFE#PBF | 製造中 | |

| LTC3618EFE#TRPBF | 製造中 | |

|

4 6, 2022 - 22_0068 Laser Top Mark for ETSSOP and TSSOP Packages Assembled in ADPG [PNG] and UTL |

||

| LTC3618EFE#PBF | 製造中 | |

| LTC3618EFE#TRPBF | 製造中 | |

| LTC3618IFE#PBF | 製造中 | |

| LTC3618IFE#TRPBF | 製造中 | |

|

4 14, 2025 - 25_0017 Bond Wire Change from Gold to Copper |

||

| LTC3618EUF#PBF | 製造中 | |

| LTC3618EUF#TRPBF | 製造中 | |

| LTC3618IFE#PBF | 製造中 | |

| LTC3618IFE#TRPBF | 製造中 | |

| LTC3618IUF#WPBF | 製造中 | |

| LTC3618IUF#WTRPBF | 製造中 | |

|

4 17, 2025 - 25_0043 Change of Gold to Copper Wire and BOM (Automotive) |

||

| LTC3618IUF#WPBF | 製造中 | |

| LTC3618IUF#WTRPBF | 製造中 | |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

必要なソフトウェア/ドライバが見つかりませんか?

ドライバ/ソフトウェアをリクエストハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| DDR/QDRメモリ/バス終端 1 | ||

| LTM4632 | 新規設計に推奨 | DDR-QDR4メモリ向けの超薄型トリプル出力降圧µModuleレギュレータ |

| シリコン発振器 1 | ||

| LTC6908 | スペクトル拡散変調付き抵抗設定SOT-23発振器 | |

| デジタル・パワー・システム・マネージメント(PSM) 1 | ||

| LTC2974 | 新規設計に推奨 | 正確な出力電流測定を特長とする4チャンネルPMBusパワーシステム・マネージャ |

| デジタル温度センサー 1 | ||

| LTC2991 | 新規設計に推奨 | I2C インタフェース搭載のオクタル電圧、電流、温度モニタ |

| 複数出力降圧レギュレータ 1 | ||

| LTC3880 | 新規設計に推奨 | デジタル・パワー・システム・マネージメントを搭載したデュアル出力PolyPhase降圧DC/DCコントローラ |

ツールおよびシミュレーション

LTspice 1

下記製品はLTspiceで使用することが出来ます。:

- LTC3618

LTspice®は、無料で提供される強力で高速な回路シミュレータと回路図入力、波形ビューワに改善を加え、アナログ回路のシミュレーションを容易にするためのモデルを搭載しています。