LTC3617

新規設計に推奨DDR終端向け±6Aモノリシック同期整流式降圧レギュレータ

- 製品モデル

- 4

- 1Ku当たりの価格

- 最低価格:$4.55

製品の詳細

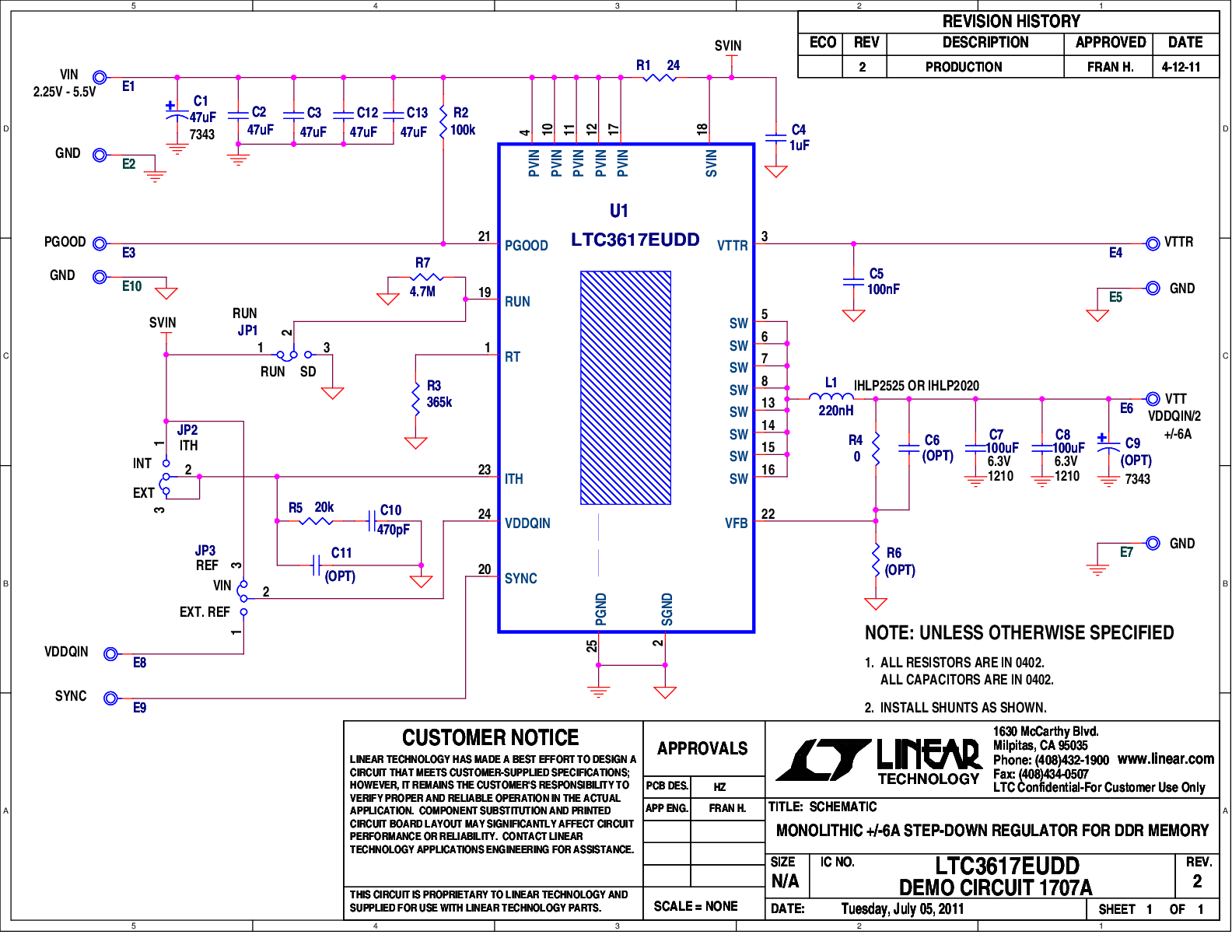

- 出力電流:±6A

- 入力電圧範囲:2.25V~5.5V

- 出力電圧精度:±10mV

- 最小0.5Vの低出力電圧向けに最適化

- 高効率

- 内蔵バッファによるVTTR = VDDQIN • 0.5

- シャットダウン電流:<1µA

- 調整可能なスイッチング周波数:最大4MHz

- オプションの内部補償

- 内部ソフトスタート

- パワーグッド状態出力

- 入力過電圧保護

- 熱特性が改善された24ピン3mm × 5mm QFN パッケージ

LTC3617は、固定周波数電流モード・アーキテクチャを採用した高効率モノリシック同期整流式降圧レギュレータです。 2.25V~5.5Vの入力電圧範囲で動作し、0.5 • VDDQINの安定化出力電圧を供給し、最大6A の負荷電流をソースおよびシンクします。内部アンプが0.5 • VDDQINのVTTR出力電圧を供給し、±10mAの出力電流が可能です。

4MHzまでの動作周波数を外部設定可能なので、小型の表面実装インダクタを使用できます。スイッチング・ノイズに敏感なアプリケーションでは、最大4MHzの外部クロックに同期させることができます。

LTC3617は強制連続モード動作によってノイズとRF干渉を低減します。 外部補償を調整できるので、広範な負荷と出力コンデンサに対して過渡応答を最適化することができます。

内部同期スイッチにより、効率が向上し、外付けキャッチ・ダイオードが不要なので、外付け部品数とボードスペースを最小限に抑えます。LTC3617は熱特性が改善されたリードレス24ピン3mm × 5mm QFN パッケージで供給されます。

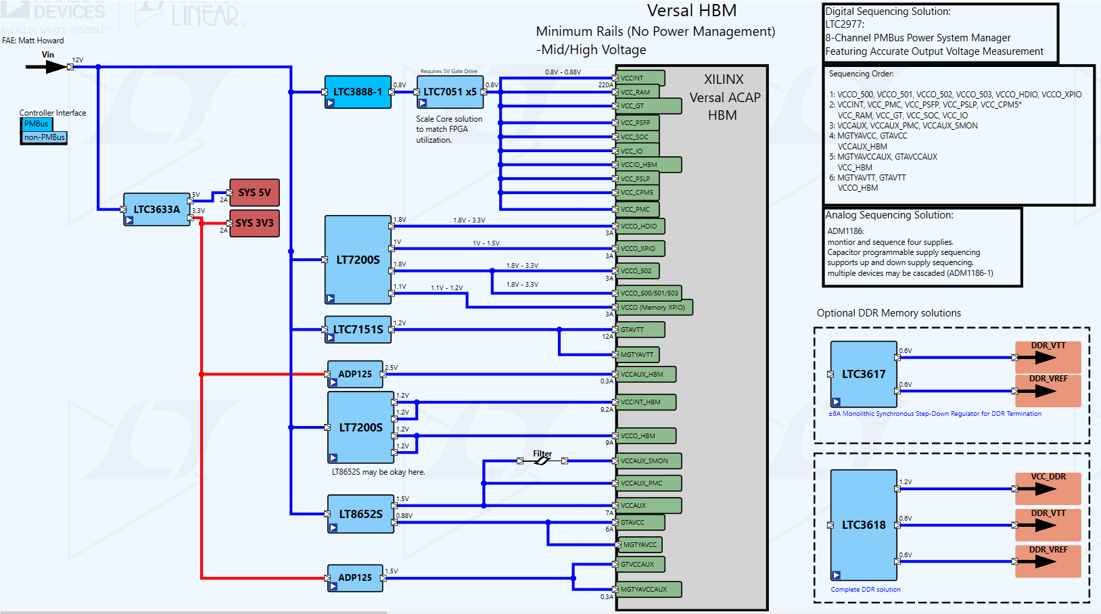

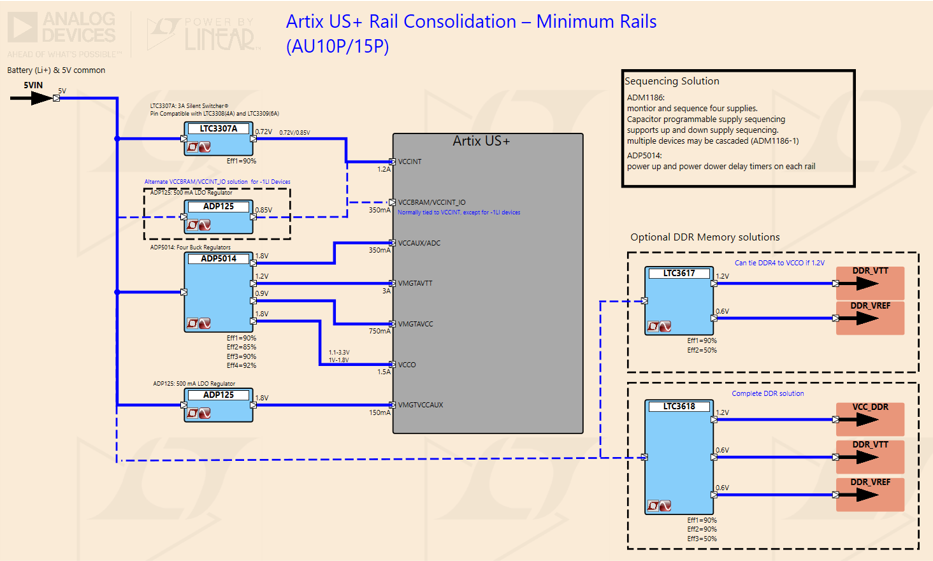

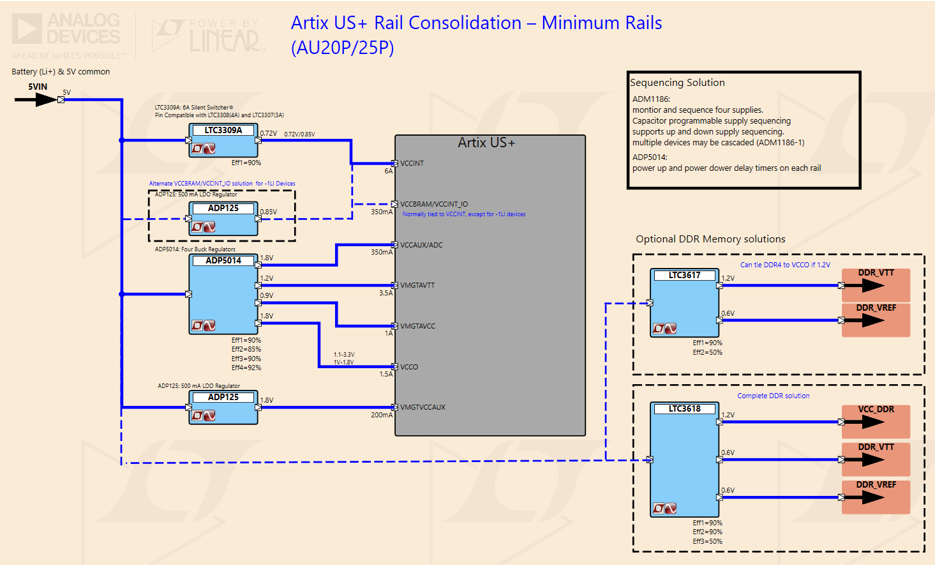

アプリケーション

- DDRの終端

- DDR、DDR2、DDR3の各規格に対応

- トラッキング電源

ドキュメント

データシート 2

信頼性データ 1

ユーザ・ガイド 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| LTC3617EUDD#PBF | 24-Lead QFN (3mm x 5mm x 0.75mm w/ EP) | ||

| LTC3617EUDD#TRPBF | 24-Lead QFN (3mm x 5mm x 0.75mm w/ EP) | ||

| LTC3617IUDD#PBF | 24-Lead QFN (3mm x 5mm x 0.75mm w/ EP) | ||

| LTC3617IUDD#TRPBF | 24-Lead QFN (3mm x 5mm x 0.75mm w/ EP) |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

必要なソフトウェア/ドライバが見つかりませんか?

ドライバ/ソフトウェアをリクエストハードウェア・エコシステム

ツールおよびシミュレーション

LTspice 1

下記製品はLTspiceで使用することが出来ます。:

- LTC3617

LTspice®は、無料で提供される強力で高速な回路シミュレータと回路図入力、波形ビューワに改善を加え、アナログ回路のシミュレーションを容易にするためのモデルを搭載しています。