電源監視、制御、保護

- PoE(Power-over-Ethernet)インターフェース・コントローラ

- PowerPath、理想ダイオード(Ideal Diodes)、負荷スイッチ

- USBパワー・スイッチ

- エネルギー・モニタ

- ケーブル・ドロップ補償

- サージ・ストッパ、過電圧および過電流保護

- シーケンサ、トラッカ、マージニング・コントローラ

- デジタルPSM(パワー・システム・マネージメント)

- ハイサイド・スイッチ & MOSFET ドライバ

- パワー・コントローラ

- パワープレーン/CardBusスイッチ

- プッシュボタン・コントローラ

- ホットスワップコントローラ

- 監視回路

- 絶縁型ゲート・ドライバ

- 電源モニタ

- 電流制限スイッチ

- 熱電クーラー(TEC)コントローラ

- 不揮発性RAMコントローラ

- 理想ダイオード・ブリッジ

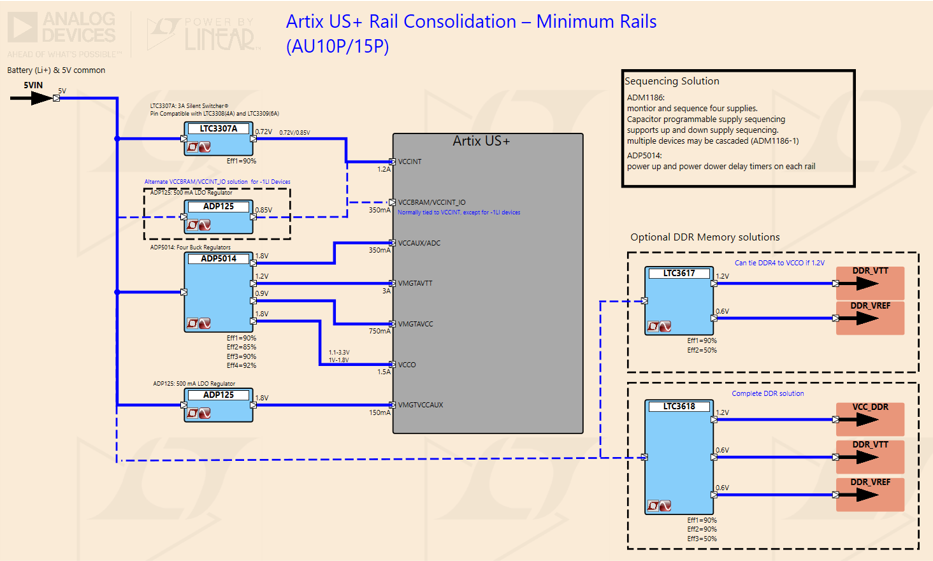

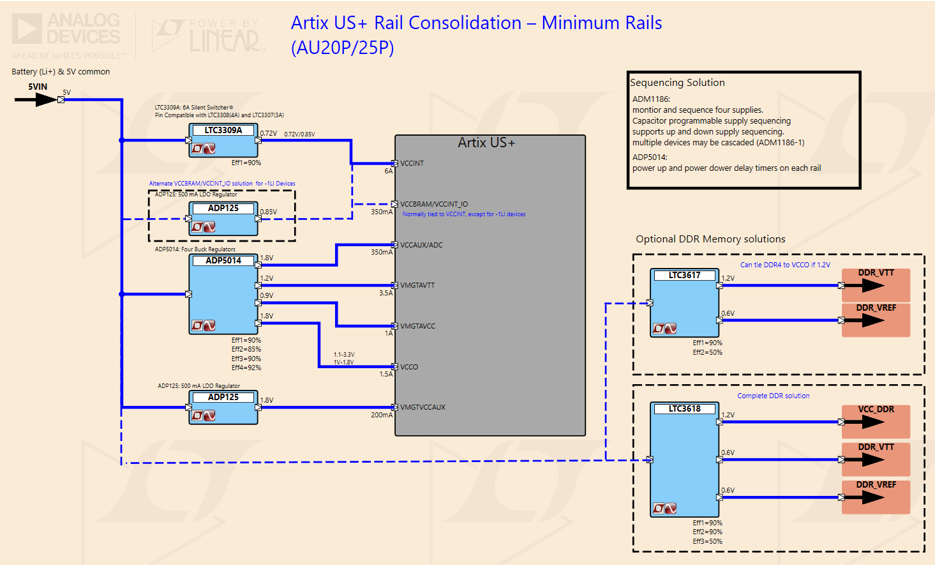

ADM1186