AD9084

発売前Apollo MxFE、16ビット28GSPSクワッドRF DACおよび12ビット20GSPSクワッドRF ADC

製品の詳細

- 柔軟性が高く再構成可能な共通プラットフォーム設計

- 4つのDACおよび4つのADC(4D4A)

- 使用可能RFアナログ帯域幅:最大18GHz

- 最大DAC/ADCサンプル・レート:最大28GSPS/20GSPS

- DAC対ADCサンプル・レート比は1または2から選択可能

- クロッキング

- オンチップPLL(7GHz~14GHz)

- 外部RFCLK入力:最大20GHz

- サブクラス1を使用したマルチチップ同期

- シングルエンド(SE)または差動(DIFF)ADC入力

- 2つの別々のバージョン。どちらも50Ωの入力インピーダンス

- シングルエンド・バージョンは広帯域幅のバランを内蔵

- 差動ADCのAC性能(20GSPS時)

- フルスケール入力電圧:500mV p-p/−2dBm

- ノイズ密度:−150dBFS/Hz(−20dBFS、2GHz時)

- HD2/HD3:−65dBFS/−70dBFS(−7dBFS、2GHz時)

- IMD3:−75dBFS(−13dBFS/トーン、2GHz時)

- DACのAC性能(28GSPS時)

- フルスケール出力電力:−2.1dBm(2GHz時)

- IMD3:−75dBc(−13dBFS/トーン、2GHz~10GHz時)

- NSD(シャッフリングを無効):−164dBFS/Hz(0dBFS、2GHz時)

- 汎用デジタル機能

- 実数または複素数のデジタル・データ(8、12、または16ビット)に対応

- 設定可能なDDCとDUC

- 8つの微調整複素DUCと4つの粗調整複素DUC

- 8つの微調整複素DDCと4つの粗調整複素DDC

- オプションで微調整および粗調整DUC/DDCをバイパス可能

- DUC/DDCのエイリアス除去

- インターポレーション・フィルタの場合85dB

- デシメーション・フィルタの場合100dB

- フラクショナル・サンプル・レート・コンバータ(FSRC)

- 送受信用プログラマブルFIRフィルタ

- 複数のループバック(ADCからDAC)に対応

- DSP経路のない場合約45ns

- SPI/HSCI/GPIOを用いた動的な設定

- スペクトラム・スニファ/モニタ

- インターフェイス

- SPI

- ハイスピード制御インターフェイス(HSCI)

- JESD204B/JESD204C:20Gbps/32.5Gbps

- Rx用に24レーン、Tx用に24レーン

- 受信AGCに対応

- 高速AGC制御用の低遅延・高速検出

- 低速AGC制御用の信号モニタ

- 補助機能

- パワー・アンプ後段の保護回路

- 温度モニタリング・ユニット内蔵

- TDD省電力オプション

- 総消費電力の範囲はデバイス設定に依存:20W~30W

- 24mm × 26mm、0.8mmピッチ899ボールBGA

- 動作ジャンクション温度(TJ):−40°C~+110°C

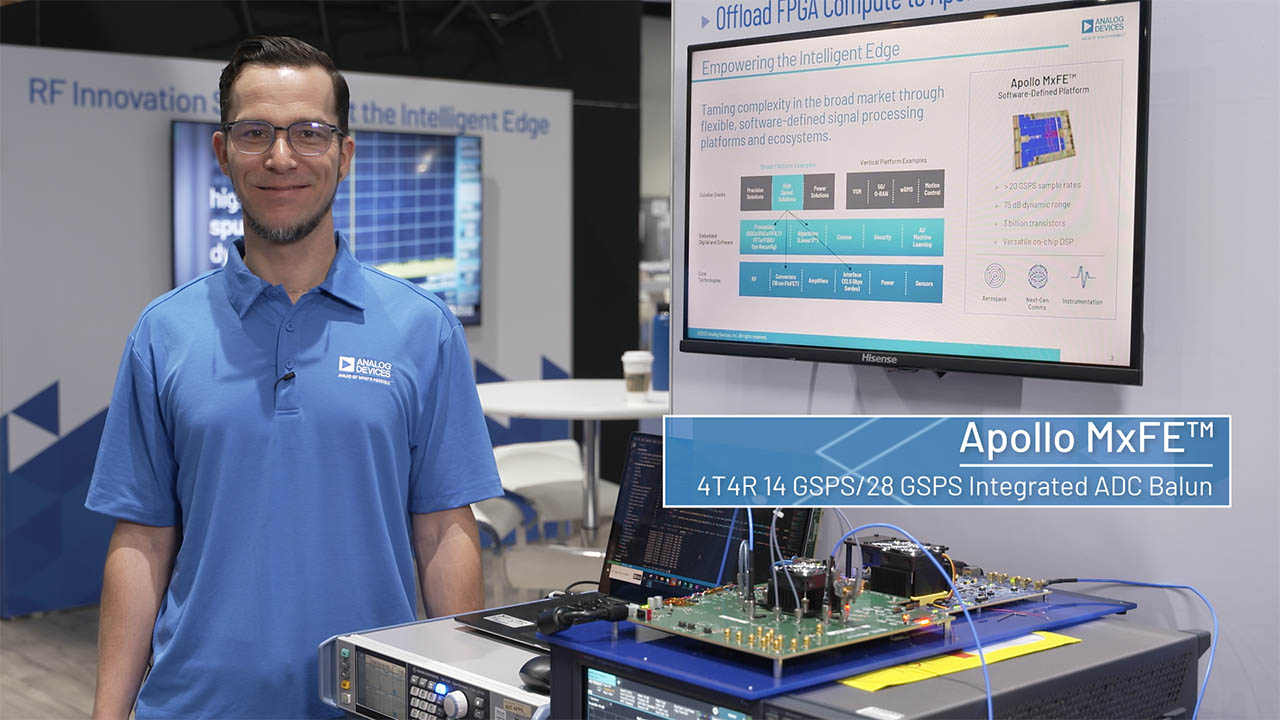

Apolloミックスド・シグナル・フロント・エンド(MxFE®)は、16ビットで最大サンプリング・レートが28GSPSのRF D/Aコンバータ(DAC)コア、および12ビットで最大サンプリング・レートが20GSPSのRF A/Dコンバータ(ADC)コアを内蔵した高集積デバイスです。AD9084は、4つの送信チャンネルと4つの受信チャンネルをサポートしており、瞬時帯域幅の広い信号を処理するために広帯域のADCとDACが必要なアプリケーションに最適です。このデバイスは、48レーンの32.5Gbps JESD204Cまたは20Gbps JESD204Bデータ・トランシーバー・ポート、オンチップ・クロック逓倍器、およびデジタル・シグナル・プロセッサ(DSP)機能を備え、広帯域またはマルチバンドのDC~RFアプリケーションを対象としています。また、DSPデータパスをバイパスしてADCコアやDACコアの全帯域幅能力を使用できるバイパス・モードも備えています。更に、フェーズド・アレイ・レーダー・システムや電子戦アプリケーションを対象とした低遅延ループバック・モードおよび周波数ホッピング・モードも備えています。

AD9084は24mm × 26mmの899ボールBGAに収められ、−40°C~+110°Cのジャンクション温度範囲で動作します。その他の情報については、ApolloSupport@analog.comにお問い合わせください。

アプリケーション

- レーダーおよび通信

- L/S/C/X/Ku帯レーダーおよび電子戦

- フェーズ・アレイ・システム

- ブロードバンド通信システム

- 電子試験装置および計測装置

- 衛星通信

- マイクロ波のポイントtoポイント、Xバンド、および5Gミリ波

Apollo MxFE™および最新のAD9084/AD9088製品リリースに関心をお寄せいただきありがとうございます。 登録するとApolloの最新情報を入手できます。

ドキュメント

データシート 1

技術記事 7

ビデオ 10

これは最新改訂バージョンのデータシートです。

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| µModule 降圧レギュレータ 2 | ||

| LTM4702 | 新規設計に推奨 | 16VIN、8A超低ノイズ、Silent Switcher®(サイレント・スイッチャ)μModuleレギュレータ |

| LTM8074 | 新規設計に推奨 | 40 VIN、1.2 A Silent Switcher ®(サイレント・スイッチャ) µモジュール・レギュレータ |

| VCO内蔵PLL 1 | ||

| ADF4382A | 新規設計に推奨 | 高性能コンバータのクロック供給アプリケーション向け、2.87GHz~21GHzフラクショナルN PLL/VCO |

| クロック同期 1 | ||

| ADF4030 | 新規設計に推奨 | 10チャンネル高精度シンクロナイザ |

| デジタル・パワー・システム・マネージメント(PSM) 1 | ||

| LTC2977 | 新規設計に推奨 | 正確な出力電圧測定を特長とする8チャネルPMBusパワーシステム・マネージャ |

| デジタル制御VGA 2 | ||

| ADL6331 | 新規設計に推奨 | 0.38GHz~12GHz TxVGA |

| ADL6332 | 新規設計に推奨 | 0.38GHz~12GHz RxVGA |

| フラクショナル N PLL 1 | ||

| ADF4382 | 新規設計に推奨 | VCO内蔵マイクロ波広帯域シンセサイザ |

| 正電圧のリニア電圧レギュレータ(LDO) 1 | ||

| LTM4709 | 新規設計に推奨 | 設定可能な出力アレイを備えた、トリプル3A、超低ノイズ、高PSRR、超高速のμModuleリニア・レギュレータ |

| 超低ノイズ・レギュレータ 1 | ||

| LT8627SP | 新規設計に推奨 | 18V/16A超低ノイズリファレンス内蔵降圧Silent Switcher®(サイレント・スイッチャ)3 |

| 負電圧のリニア電圧レギュレータ(LDO) 1 | ||

| LT3094 | 新規設計に推奨 | −20 V、500 mA、超低ノイズ、超高 PSRR、負電圧のリニア電圧レギュレータ |

ツールおよびシミュレーション

Clock & Timing Tools

Analog Devices provides design tools that work with our product portfolio to help engineers build critical clock and timing IC solutions for wired and wireless networks.

ツールを開くデータ変換計算ツール

有効ビット数、S/N比、信号/ノイズ + 歪み(SINAD)、THDを計算します。

ツールを開く周波数折り返しツール

このツールは、ADCのデジタル化における入力信号とその高調波のエイリアシング効果を可視化します。シングル・トーン信号か変調搬送波入力信号を選び、最大10のナイキスト領域におけるエイリアシングを確認することができます。

ツールを開くSNR/THD/SINAD 計算ツール

SNR、THD、SINADからENOBとノイズを計算によって変換します。また、SNR、THD、またはSINADの1つを他の2つから計算します。