質問:

ゲイン段を追加することなく、大きな差動オフセット電圧に対処する方法はありませんか?

回答:

マイクロパワー、レールtoレール、間接電流モードの計装アンプを使用することで対応できます。その種のアンプを使用すれば、1段構成でACカップリングと増幅を実現できます。以下では、この設計について詳細に解説します。その長所を明らかにしつつ、段階的に設計を進める方法を示すことにします。

はじめに

電磁流量や生体電位を測定するアプリケーションでは、非常に大きな差動オフセットに小さな差動信号が重畳しているという状況に対応する必要があります。通常、そうしたオフセットは、フロント・エンド回路がとり得るゲインに制約を加えます。結果として、システム全体としてのダイナミック・レンジに影響が及ぶことになります。バッテリ駆動の機器など、低い電源電圧で動作するシグナル・チェーンでは、ゲインに対する制限がより厳しくなります。このような差動オフセットの問題に対する1つの解決策は、信号の測定用にACカップリング型のシグナル・チェーンを採用することです。このような条件に対応できるシグナル・チェーンの代表的な例としては、ゲインの小さい計装アンプの後段にハイパス・フィルタとゲイン段を追加するというものが挙げられます(「Amplifying AC Signals with Large DC Offsets for Low Power Designs(低消費電力が求められる設計において、DCオフセットが大きいAC信号を増幅する方法)」を参照)。ほとんどのアプリケーションでは、シグナル・チェーンの初段でできるだけ高いゲインが得られるようにすべきです。そうすれば、後続のゲイン段における入力換算ノイズを改善できるからです。

本稿では、間接電流モードの計装アンプ(in-amp)を取り上げます。そのアーキテクチャがもたらす主要なメリットは、1段構成の回路によって高いゲインとACカップリングを同時に実現できることです。本稿では、その具体的な例としてゼロドリフトの計装アンプ「AD8237」を取り上げます。この製品は、消費電力が極めて少なく、広いコモンモード/差動入力範囲に対応しています。間接電流モードのアーキテクチャを採用した他の製品としては「AD8420」などがあります。この種の計装アンプは、主に以下のような長所を備えています。

- 低消費電力のアーキテクチャを採用しています。

- 2 つまたは 3 つのオペアンプで構成した計装アンプなど、他の一般的なアーキテクチャのように、ダイヤモンド・プロットに大きな制限が加わることがありません。

- マッチングのとれた外付け抵抗を使用することにより、優れたゲイン・ドリフト性能を達成することができます。

- 抵抗のマッチングがとれているかどうかに関わらず、高いCMRR 性能を達成できます。

- 高インピーダンスのリファレンス・ピンを備えています。

図1に示したのは、本稿で例にとるシグナル・コンディショニング回路です。ご覧のように、間接電流モードに対応する計装アンプとしてAD8237を使用して構成しています。先述したように、同アンプを使用すれば、高いゲインとACカップリングを1段で実現することが可能です。但し、そのためには、AD8237の帰還ループに積分回路を配置する必要があります。それでも、このソリューションを採用すれば、2つまたは3つのオペアンプで構成された計装アンプを使う場合と比べて高いゲインを得ることができます。2つまたは3つのオペアンプで構成した計装アンプでは、ゲインを適用した後にオフセットをキャンセルすることになります。それに対し、間接電流モードに対応する計装アンプのアーキテクチャでは、ゲイン段で信号を増幅する前にオフセットの補正を行うことが可能です。このアーキテクチャと従来の計装アンプのアーキテクチャについては、稿末の付録で補足説明を行います。

図1の回路では、オペアンプ「ADA4505」を使用して帰還ループに配置する積分回路を構成しています。ADA4505の非反転入力は、VMIDに設定されています。この積分回路によってAD8237の出力が検出され、AD8237の出力がVMIDになるようAD8237のリファレンス・ピン(REFピン)が駆動されます。一般に、積分回路はローパス・フィルタとして働きます。ただ、この回路では帰還ループに積分回路が配置されており、回路全体としてはハイパス・フィルタの伝達関数を備えていることになります。この動作により、最終的にゲイン段の前でDCオフセットが阻止されます。そのため、他のソリューションと比べてゲインを高く設定することができます。電源電圧が低くオフセットが大きい場合には、通常の動作に使用できるヘッドルームが限られます。そのため、この回路は非常に有効に機能します。この積分回路を使えば、リファレンス・ピンを介して、AD8237の出力を、設定した電圧に強制的に駆動することも可能です。この積分回路は、AD8237のFBピンに入力差動電圧と値が等しく逆極性の電圧が設定されるようにリファレンス・ピンを駆動します。

設計仕様の例

通常、低消費電力のアプリケーションでは、1.8V~3.6Vの範囲の単一電源が使用されます。図1に示した回路の場合、入力信号の振幅/周波数とオフセットの振幅に応じて、設計上の選択を行うことになります。表1に、図1の回路の設計仕様の例を示しました。

この回路では、設計上の選択として、AD8237の狭帯域幅モードを使用することにします。それにより、ゲインの柔軟性とより高い安定性を確保することにしました。

表1. 図1の回路の主な設計仕様

| センサーのVOFFSETの最大振幅 | センサーのVSIGNALの最大振幅 | センサーのVSIGNALの最低/最高周波数 | センサーのコモンモード電圧VCM | 電源電圧VDD/VSS | 最大電源電流 | 出力コモンモード電圧VMID |

| ±1V | ±6mV | 20Hz/220Hz | 1.65V | +3.3 V/0V | 200μA | 1.65V |

設計に関する説明

図1の回路は、マイクロパワー、レールtoレールの計装アンプであるAD8237と、ゼロ・クロスオーバー歪みのオペアンプであるADA4505で構成されています。どちらも最小3.3Vの電源電圧VDDで動作します。

図1の回路は、DCオフセット電圧VOFFSETを除去しながら、入力に現れるAC信号VSIGNALを増幅して電圧VOUTを出力します。それに向けて、ADA4505の非反転入力とAD8237のゲイン段の出力のコモンモード電圧を電源の中央値に設定します。電源の中央値である電圧VMIDを生成するためには、抵抗分圧器を使用します。抵抗R1、R2によって分圧器を構成し、もう1つのADA4505でバッファしています。AD8237のパッケージはMSOP、ADA4505のパッケージは小型のWLCSPです。

設計時に考慮すべき事柄

以下に、設計時に考慮すべき事柄を列挙します。

1. VREF(AD8237のリファレンス・ピン)の値は、ADA4505-2(1/2)の非反転入力に印加されるVMIDによって設定されます。その結果として、出力VOUTもその値に設定されます。ほとんどの計装アンプにおいて、2つの電源レールの間で最大の出力振幅を確保するためには、電源の中央値(VDD/2)がVMIDの最適値となります。これについては、コモンモード入力電圧と出力電圧範囲の関係、つまりはダイヤモンド・プロットの観点から見て明らかにそのようになります。この検討には「計装アンプ・ダイヤモンド・プロット・ツール」が役立ちます。このツールについては、後ほど「設計についてのシミュレーション」のセクションで説明することにします。

2. この回路のトータルの電源電流を抑えるためには、R1、R2の値の選択も重要です。抵抗の選択は、ノイズと消費電力のトレードオフになります。この回路の場合、電源電流の増加を最小限に抑えるために、大きい値を選択するとよいでしょう。この抵抗分圧器による電源電流の増加分は、以下の式で表されます。

- 抵抗分圧器(R1、R2)には、コンデンサ C1 を追加することができます。そうすると、ノイズの帯域制限や、50Hz/60Hzの成分の低減といった形で VDD への干渉を抑えることが可能になります。コンデンサの値を大きくするほど、ノイズのフィルタリング効果は向上します。但し、回路を起動する際、VMIDがセトリングするまでの時間が長くなります。1% 以内のレベルにセトリングするまでにかかる時間は、次式によって推定できます。

3. 受動部品(抵抗やコンデンサ)の値を選択する際には、許容誤差について考慮しなければなりません。その誤差が原因で、抵抗分圧器(R1、R2)で目標とするVMIDの値がずれる可能性があるからです。そうすると、AD8237とADA4505の出力に影響が及ぶことになります。

図1の回路の場合、伝達関数のカットオフ周波数は2つ存在します。1つは、ADA4505で構成した帰還ループ内の積分回路に起因するハイパス・フィルタのカットオフ周波数です。もう1つは、AD8237の帯域幅によって決まるローパス・フィルタ応答のカットオフ周波数です。積分回路のカットオフ周波数とAD8237の帯域幅が組み合わさることにより、ある程度のゲイン誤差が生じる可能性があります。したがって、ハイパス・フィルタのカットオフ周波数とローパス・フィルタのカットオフ周波数を適切な範囲内に収めることが重要です。カットオフ周波数が互いにどの程度近い値であるかによって、ゲインの誤差率が変動する可能性があります。

4. アプリケーションにおいて、高インピーダンスのセンサーを使用したいケースもあるでしょう。その場合、ADA4505などのバッファをAD8237の入力の前に適用します。それにより、高い入力インピーダンスが得られ、入力バイアス電流の量を抑えられます。バッファによって、高インピーダンスの入力が低インピーダンスの出力に変換されるからです。なお、AD8237の入力バイアス電流は、全温度範囲にわたって最大1nAです。

設計手順

続いて、より具体的な設計手順を説明していきます。

【ステップ1】VMIDを設定するための分圧器を設計する

「設計時に考慮すべき事柄」の(2)で説明したように、図1の回路においてR1、R2の値を1MΩに設定すると、電源電流の増加分を1µAに近いレベルに抑えることができます(以下参照)。

R1、R2で構成される抵抗分圧器の出力は、次式によって決まります。

R1とR2の許容誤差が5%であると仮定し、ADA4505のオフセットを考慮すると、次式が得られます。

AC電源の干渉と抵抗からのノイズの影響を抑えるために、C1の値を設定します。その値は、カットオフ周波数が少なくともVSIGNALの最小周波数である20Hzを下回るようにします。なお、ノイズの帯域制限を強化する必要がある場合には、コンデンサの値をもっと大きくしても構いません。C1の値は以下のようにして決定します。

上式に基づき、C1の値を22nFに設定したとします。その場合、カットオフ周波数は次式のようになります。

【ステップ2】VSIGNALに基づき、計装アンプ(AD8237)のゲインを定める

ここでは、電磁流量センサーに対応するシグナル・コンディショニング回路を設計しているものとします。通常、その種のセンサーの出力範囲(ピークtoピークの信号振幅)は±75µV~±6mV程度です。図1の回路では、30Hzの周波数においてVSIGNALが6mV(ピーク)になるとして、ピークtoピークの信号振幅範囲を想定します。

次に、電源レールに対するAD8237の出力振幅範囲の制限について考えます。これらの値は、データシートの「Output Swing」の欄に記載されています。控えめな想定に基づき、25°C、RL = 10kΩの場合の振幅について考えます(以下参照)。

電源電圧が3.3Vの場合、次式のようになります。

出力は完全差動型なので、その値はVMIDを基準としてスイングします。最も厳しい条件では、次式のようになります。

正の入力信号(VMIDMAX = 1.732V)の場合

負の入力信号(VMIDMAX = 1.568V)の場合

ここで、ゲインを設定するために、トータルの差動入力信号を想定し、正と負の振幅範囲の低い方を使って最大振幅範囲を設定します(以下参照)。

出力電圧範囲の制限について考慮すると、AD8237のゲインは253未満に設定する必要があります。DC誤差などに対してある程度のマージンを確保するために、図1の回路のゲインは最大値よりも小さく設定する必要があります。また、ゲインとセトリング時間の間にもトレードオフが存在します。ゲインを高くするほど、フィルタの時定数は大きくなります。これらのことから、AD8237のゲインを101に設定することにしました。

振幅の最大化に関しては、「設計時に考慮すべき事柄」の(1)に記載した内容に注意してください。

データシートから、ゲインに関連する式は次のようになることがわかります。

AD8237のデータシートには、ゲインを設定するために推奨される抵抗値が記載されています。それに従えば、101というゲインを得たい場合、RF1を100kΩ、RG1を1kΩに設定するのが妥当だと考えられます。

【ステップ3】 計装アンプ(AD8237)の帯域幅について検討する

データシートを参照すると、カットオフ周波数の値は次式で与えられることがわかります。

設計仕様の面から、最高信号周波数に対しては、ある最小減衰量が必要であるかもしれません。それについては、所定のフィルタのカットオフ周波数に対して、次式のようにして簡単に確認することができます。

【ステップ4】 ハイパス・フィルタのカットオフ周波数を設定する

「設計時に考慮すべき事柄」の(3)で説明したように、積分回路によって決まるハイパス・フィルタのカットオフ周波数が高いと、AD8237の帯域幅によって決まるローパス・フィルタのカットオフ周波数と値が近くなりすぎる可能性があります。その場合、既に設定したゲインにいくらかのゲイン誤差が生じます。

ここでは、抵抗R3とコンデンサC3の許容誤差が±5%だと仮定します。最も小さい時定数は、VSIGNALの最小周波数に対応する値よりも小さくなるはずなので、次式が成り立ちます。

R3の値は、それを介してオペアンプに流入する電流を最小限に抑えるために、1MΩに設定することにします。すると、以下の式が成り立ちます。

カットオフ周波数を約20Hzに設定するために、コンデンサの標準品の中で最も近い値のものを選択します。ここでは、C3の値を1.5µFに設定することにしましょう。それを踏まえると、実際のカットオフ周波数は次式のようになります。

設計仕様の面から、最低信号周波数に対しても、ある最小減衰量が必要であるかもしれません。これについても、所定のフィルタのカットオフ周波数に対して、次式のようにして簡単に確認することができます。

【ステップ5】オフセット電圧の確認

VOFFSETにもVCMにも制限があります。

この回路において、DCオフセットはほとんどのアプリケーションで見られる値よりも大きくなる可能性があります。これについては、V OFFSET≦±VMIDという条件を満たさなければなりません。この制限よりもDCオフセットの値が大きい場合、VREFの電圧値はADA4505の電源電圧の範囲外を外れてしまいます。リファレンス・ピンに関連する式は、VREF = VMID - VOFFSETとなります。この例では、VOFFSETは1Vになります。

コモンモード電圧VCMについては、次式の範囲内に収まっている必要があります。

ご覧のように、VOFFSETが直接的に影響を及ぼします。

これらの制限値については必ず検証しなければなりません。それを怠ると、AD8237に対する入力値が電源電圧の範囲を外れてしまうことになります。ここではVCMを1.65Vに設定することにします。

設計についてのシミュレーション

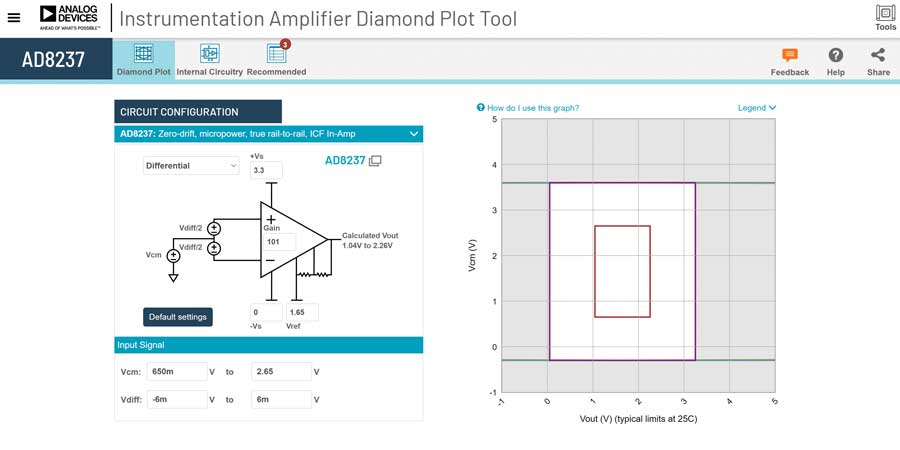

計装アンプのコモンモード入力電圧範囲と出力電圧の関係は、ダイヤモンド・プロットと呼ばれます。これについて確認するには、電源電圧VDD、リファレンス電圧、ゲイン、コモンモード電圧の振幅、差動入力の振幅を指定する必要があります。入力振幅がデバイスの動作範囲内にあるか否かを確認する際には、先ほど触れた計装アンプ・ダイヤモンド・プロット・ツールが役に立ちます。このツールでは、出力振幅について最も厳しい負荷の条件(最小の抵抗性負荷)が適用されます。そのため、同ツールの制限値に合わせて設計を行えば、抵抗性の負荷に対してより大きなマージンが得られます。ここで、図2に示した同ツールの利用画面をご覧ください。紫色の外枠は、所定の電源電圧、出力振幅、入力コモンモード電圧範囲、リファレンス電圧に対してAD8237を使用できる範囲を示すものです。一方、赤色の枠は、この範囲のうちどの程度を所定のコモンモード電圧と差動入力モードの振幅に対応するために使用しているのかを表しています。設計時の目標は、赤色の枠を紫色の外枠の範囲内に収めることです。これに反する条件が存在すると、このツールはエラーという結果が提示します。それだけでなく、推奨される対応策を示してくれます。但し、このインターフェースでは、帰還ループに積分回路を配置するのは不可能であることに注意してください。とはいえ、代替策は存在します。それは、図1の回路のVOFFSETとVCMの電圧が追加されているかのように、ダイヤモンド・プロットの入力信号を設定するというものです。0.65V~2.65Vという範囲を使用すれば、DCオフセットは除去されますが、ゲインは得られません。また、出力がスイングする余地がいくらか残っているので、コモンモード電圧が更に高くなり得ることもわかります。計装アンプの内部で起こっていることについて理解するためには、「内部ブロック図」のタブをクリックします。すると、内部ノードの電圧が表示されます。

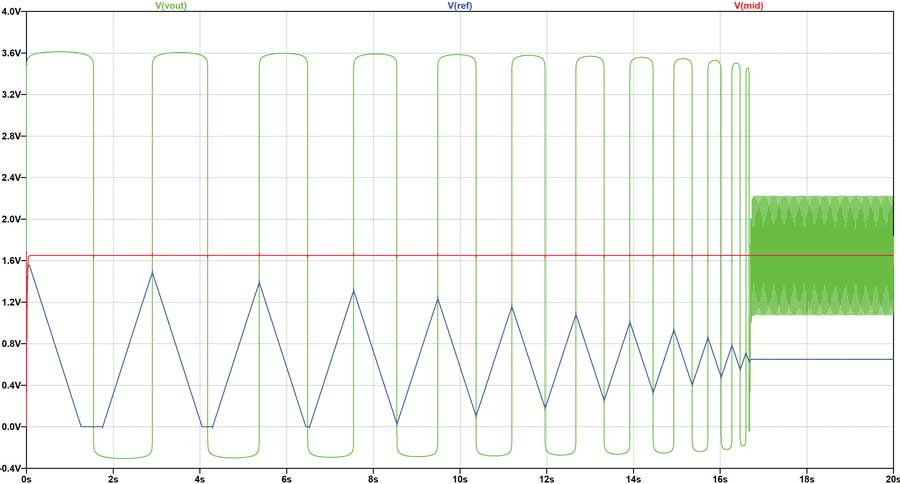

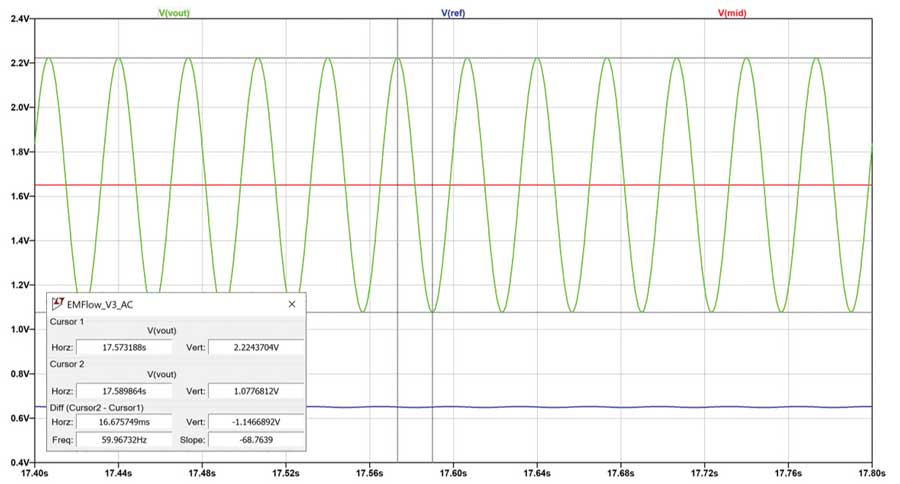

もう1つ、検証に利用可能な優れたツールが存在します。それは、回路シミュレータであるLTspice®です。これを使用すれば、上に示した設計手順で行った計算について検証を実施することができます。その際には、対象とする信号帯域におけるノイズ性能など、設計仕様として示したもの以外の事柄について確認することも可能です。図3は、LTspiceでシミュレーションを実施するための回路図です。図4、図5に示したのがシミュレーションの結果の例です。このシミュレーションでは、DCオフセットが1V、入力信号が30Hzにおいて±6mVという条件でトランジェント解析を行いました。図4は、回路の各段における信号を示したものです。一方、図5は図4の拡大図です。これを見ると、回路がセトリングし、積分回路のコンデンサが最終的な値まで充電された後の状態を確認できます。青色の線は積分回路の出力、つまりはAD8237のリファレンス・ピンの電圧です。赤色の線は、VDD/2になるように設計されたVMIDの値を表しています。緑色の線は、増幅後に得られた最終的な30Hzの出力信号VOUTを表しています。

ここで表2をご覧ください。これは、設計上の目標値とトランジェント解析の結果を比較したものです。まず、目標値(予測値)について説明します。VOUTの最大値と最小値は、VOUT = VMID±VSIGNAL×101という式から得られます。この場合、それぞれ2.256Vと1.044Vという予測値が得られます。VREFの予測値はVMID - VOFFSETに等しく、0.65Vとなります。VMIDについては、電源電圧の中央値(この場合は1.65V)になります。

続いて、トランジェント解析によって得られた結果を見てみましょう。予測値と比較すると、出力電圧については非常に近い値が得られています。しかし、シミュレーション結果をよく見ると、セトリングが完了して出力が最終値に到達するまでに17秒かかっています。その原因は、積分回路で使用しているコンデンサの値が大きいことと、設定したDCオフセットの値が大きいことです。このセトリング時間は、シミュレーションが0秒に開始し、コンデンサが充電されて最終的な値に達するまでに要する時間に対応しています。

表2. 設計上の目標値とシミュレーション結果(トランジェント解析)の比較

| パラメータ | 目標値 | シミュレーション結果 |

| VOUTMAX | 2.256 V | 2.224 V |

| VOUTMIN | 1.044 V | 1.077 V |

| VMID | 1.65 V | 1.65 V |

| VREF | 0.65 V | ≈ 0.65 V |

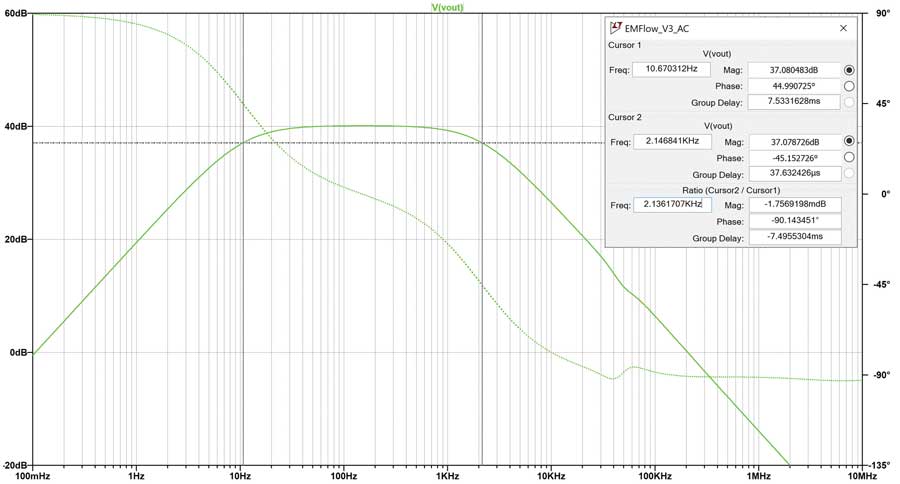

図6に、もう1つのシミュレーション結果を示しました。これは、図3の回路の周波数特性を表しています。DCオフセットは1V、入力信号は30Hzにおいて±6mVです。図6のカーソル1と同2は、それぞれハイパス・フィルタとローパス・フィルタの振幅が-3dBになるポイントに配置されています。表3に、設計上の目標値とシミュレーション結果についてまとめました。

表3. 設計上の目標値とシミュレーション結果(AC解析)の比較

| パラメータ | 目標値 | シミュレーション結果 |

| ハイパス・フィルタのf3dBADA4505 | 10.71Hz | 10.70Hz |

| ローパス・フィルタのf3dBAD8237 | 1980Hz | 2138Hz |

| 20log(Gain) | 40.08dB | 40.08dB |

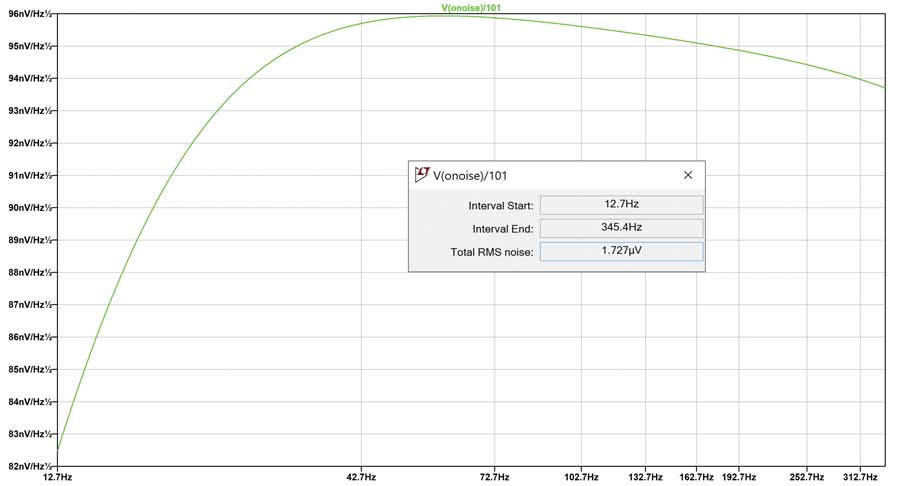

続いて、図7のシミュレーション結果をご覧ください。これは、図3の回路の周波数に対する電圧ノイズ密度(入力換算)を示したものです。出力ノイズをトータルのゲイン(101)で割ることによって取得しました。バンドパス・フィルタについては、トータルのノイズを計算する際、積分の対象とする周波数範囲を選択する必要があります。

上限周波数については、上で設定したセンサーの最高周波数の値(220Hz)を使用します。下限周波数としては、上で設定したセンサーの最低周波数の値(20Hz)を使用しています。この例の結果は、20Hzから220Hzまでの積分によって得られたノイズの値になります。

ノイズの実測値は、バンドパス・フィルタのカットオフ周波数の影響で、もっと高い値になります。LTspiceのシミュレーションでは、後処理用のフィルタの利用を想定しています。すなわち、20Hzと220Hzに急峻なロールオフ特性を備えるブリック・ウォール・フィルタが適用されています。

次に、LTspiceのコマンド・ラインを「.noise V(VOUT) V1 dec 100 20 220」と設定します。そして、<ctrl>キーを押しながら波形の名前(V(ONOISE)/101)を左クリックします。次式を使用すると、rmsノイズを簡単にピークtoピーク・ノイズに変換することができます。

AD8237のノイズとADA4505のノイズを簡単に確認すると、AD8237が支配的なノイズ源であることがわかりました。

実測結果

設計の善し悪しを評価するためには、実際に回路を構成して各種のパラメータを測定してみることが必須です。AD8237とADA4505については、評価用ボードが提供されています。そのため、実際に回路を構成し、容易にテストを実施することができます。各部品のハンダ付けは、評価用ボードの回路図を確認しながら行うとよいでしょう。両評価用ボードを同時に使用する場合、AD8237のボードのパターンをカットして、抵抗RGに電圧VMIDを接続する必要があるかもしれません。

理解しやすくするために、各部品の値は、シミュレーションと同様に、設計手順のセクションで示した値に設定しました。電磁流量計や生体電位の測定用のセンサーを想定した評価を行うために、電圧校正器や任意波形発生器など、様々な測定器を使用しました。

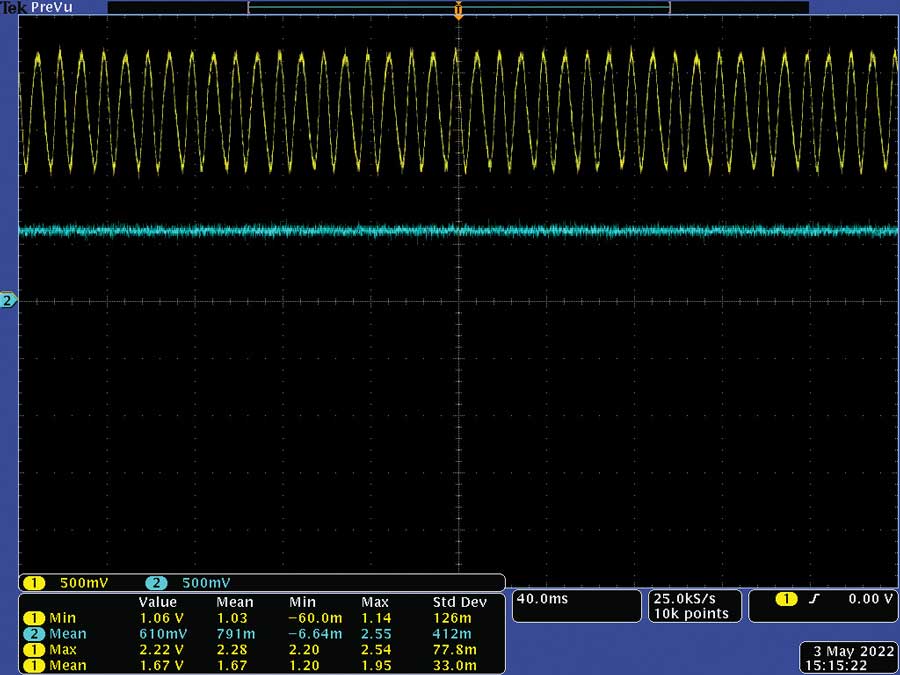

この評価では、入力信号として、DCオフセットVOFFSETを1V、コモンモード電圧を1.65V、入力信号VSIGNALを±6mV(30Hzにおける値)に設定しました。

図8に示した実測結果を見ると、出力電圧VOUT(黄色の線)は、少しずれてはいるものの目標値に近い値になっています。

表4に、設計上の目標値と測定結果についてまとめました。

表4. 設計上の目標値と実測値の比較

| パラメータ | 目標値 | 実測値 |

| VOFFSET | 1V | 1.01V |

| VSIGNAL | 6mV(ピーク) | 5.2mV(ピーク) |

| VOUTMIN | 1.044V | 1.13V |

| VOUTMAX | 2.256V | 2.19V |

| VREF | 0.65V | 0.64V |

設計上の目標値と実測結果の差は、様々な原因で発生している可能性があります。

- 例えば、使用した抵抗では5%の許容誤差が生じているかもしれません。その影響により、VMIDの値がずれた可能性があります。

- また、測定環境の整備には限界があります。そのようなことが原因となって、VOFFSETとVSIGNALに見られるような小さなずれが生じることがあり得ます。

使用したオペアンプの仕様

表5に、計装アンプであるAD8237の主な仕様を示しました。表6は通常のオペアンプであるADA4505の仕様についてまとめたものです。

表5. AD8237(計装アンプ)の主な仕様

| 品番 | パッケージ (MSOP)の寸法 |

IBIASの最大値〔nA〕 | Vosの最大値〔µV〕 | ゲインの最小値/最大値(代表値)〔kHz〕 | 0.1Hz~10Hzのノイズ(代表値)〔µV p-p〕 | VNOISE(代表値)〔nV/√Hz〕 | アンプ1個あたりのIQ(代表値)〔µA〕 | +Vsの最小値/最大値〔V〕 |

| AD8237 | 3.20mm × 5.15mm |

1 | 75 | 1/1000 | 1.5 | 68 | 115 | 1.8/5.5 |

表6. ADA4505(オペアンプ)の主な仕様

| 品番 | パッケージ(WLCSP)の寸法 | IBIASの最大値〔pA〕 | Vosの最大値〔mV〕 | GB積(代表値)〔kHz〕 | 0.1Hz~10Hzのノイズ(代表値)〔µV p-p〕 | VNOISE(代表値)〔nV/√Hz) | アンプ1個 あたりのIQ(代表値)〔µA〕 | +Vsの範囲の最小値/最大値〔V〕 |

| ADA4505 | 1.42mm × 1.42mm |

2 | 3 | 50 | 2.95 | 65 | 7 | 1.8/5 |

まとめ

現場に配備されているトランスミッタの電磁流量をセンサーで測定する際や、生体電位を測定するために電極からの信号を取得する際には、1つの問題に直面します。それは、対象とする信号が、それよりもはるかに大きなDCオフセットに重畳しているということです。そうしたセンサーから情報を容易に抽出できるようにするための解決策は、ACカップリング型の測定用シグナル・チェーンを構築することです。その目的は、AC信号を増幅すると同時にDCオフセットを除去することにあります。計装アンプであるAD8237を使用すれば、帰還ループに積分回路を配置することで、1段構成の回路によってゲインを得つつ、AC信号をカップリングすることができます。入力段でDCオフセットを除去できるので、最大のゲインが適用された信号をシグナル・チェーンのまさに入力部で測定することが可能になります。それにより、測定用のソリューション全体として入力換算ノイズを最小限に抑えることができます。

参考資料

LTspiceは、回路図のキャプチャ機能や波形ビューワを備えるSPICE III対応の回路シミュレータです。スイッチング・レギュレータやリニア・レギュレータ、シグナル・チェーンといった回路のシミュレーションを容易に行えるようにするための機能拡張やモデルも備えています。

このツールは、ウェブ・アプリケーションとして提供されています。アナログ・デバイセズの計装アンプ製品を対象としています。各製品の各種構成について、出力電圧範囲と入力コモンモード電圧の関係を表すグラフ(ダイヤモンド・プロット)を生成することができます。

付録

図9、図10は、それぞれ間接電流モードの計装アンプと、3つのオペアンプで構成した計装アンプの概念図です。間接電流モードの計装アンプでは、3つ(または2つ)のオペアンプで構成される計装アンプよりも高いゲインを得ることができます。3つのオペアンプで構成される計装アンプでは、ゲインを適用した後にオフセットをキャンセルすることになります。それに対し、間接電流モードのアーキテクチャでは、オフセットの補正がゲイン段の前で行われます。そのため、ゲインを高くすることができるのです。ここでは、各アーキテクチャの特徴について概観してみます。

図9に示したように、間接電流モードの計装アンプでは1段構成が基本になります。測定の対象となる入力電圧は、GM1のセルに印加されることになります。一方、GM2のセルは帰還ループ内に配置されています。この計装アンプが内蔵する積分器アンプAは、VIN1のコピーを強制的にVIN2に設定する役割を担います。この積分器を使うことで、ゲイン段の前のリファレンス・ピンを駆動します。ゲインは、外付け抵抗RFBとRGによって設定され、次式で表される値になります。

一方、図10に示した計装アンプは、3つのオペアンプを使用して構成されています。このタイプのアーキテクチャは、2段構成をベースとしています。まず、2つのオペアンプU1とU2、抵抗RGAIN、抵抗R1、抵抗R2により、非反転型のアンプ回路を構成しています。この回路は入力段に相当します。この段のコモンモード・ゲインは1です。差動ゲインは抵抗RGAINによって設定され、次式によって決まります。

また、オペアンプU3と抵抗R3により、差動アンプが構成されています。この差動アンプは、計装アンプ全体の出力段に相当します。コモンモード・ゲインと同相ノイズ除去は1です。このアーキテクチャにおいて、リファレンスの入力ポイントは、1つ目のゲイン段の後段の2段目に存在します。

謝辞

本稿の執筆に協力してくれたDavid Plourde(SCI[Scientific Instruments]グループ IC設計エンジニア)、Aine McCarthy(車載グループ 主任システム・アプリケーション・エンジニア)、Tim Green(SCIグループ シニア・アナログ・アプリケーション・エンジニア)に感謝します。