RF and Microwave

- Attenuators

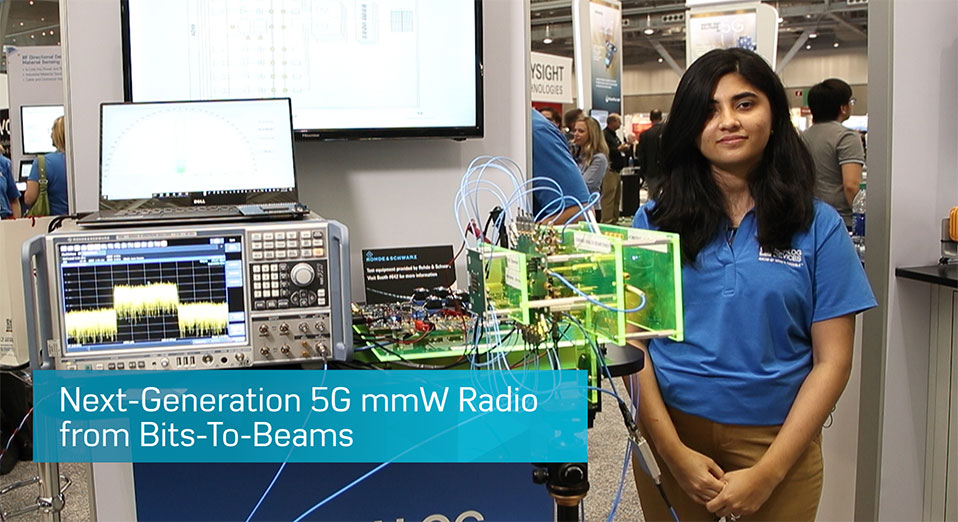

- Beamformers, Phase Shifters, and Vector Modulators

- Communications Analog Front Ends

- Frequency Dividers, Multipliers, and Detectors

- I/Q Modulators and Demodulators

- Phase Locked Loop (PLL) Synthesizer & Translation Loop

- Quadrature Digital Up Converters (QDUC)

- RF Connectorized Modules, System In Package, and Instrumentation

- RF Integrated Transmitters, Receivers, and Transceivers

- RF Mixers

- RF Power Detectors

- RF Predistortion Ics

- RF Switches

- Timing IC and Clock IC

- Tunable Filters

- Voltage Controlled Oscillators (VCO)

- Wireless Sensor Networks

AD9082