AD9986

推荐用于新设计4T2R直接RF发射器和观测接收机

- 产品模型

- 2

产品详情

- 灵活的可重新配置无线电通用平台设计

- 高达 1.2 GHz/2.4 GHz 的发射/接收通道带宽 (4T2R)

- RFDAC/RFADC 射频频率范围高达 7.5 GHz

- 具有多芯片同步功能的片内 PLL

- 外部 RFCLK 输入选项

- 多种数字特性

- 可配置数字升频/降频转换 (DDC 和 DUC)

- 8 个细调复数 DUC 和 4 个粗调复数 DUC

- 8 个细调复数 DDC 和 4 个粗调复数 DDC,2 个独立

- 每个 DUC/DDC 48 位 NCO

- 可编程 192 抽头 PFIR 滤波器,用于接收均衡

- 支持通过 GPIO 加载的 4 种不同的配置文件设置

- 接收 AGC 支持

- 用于快速 AGC 控制,具有低延迟的快速检测

- 用于缓慢 AGC 控制的信号监控器

- 专用 AGC 支持引脚

- 发射 DPD 支持

- 每个发送数据路径的可编程延迟和增益

- DPD 观察路径的粗调 DDC 延迟调整

- 可配置数字升频/降频转换 (DDC 和 DUC)

- 辅助特性

- 功率放大器下游保护电路

- 片内温度监控单元

- 支持不同用户配置的可编程 GPIO 引脚

- 具有可选分频比的 ADC 时钟驱动器

- TDD 省电选项和共享 ADC

- SERDES JESD204B/JESD204C 接口,16 个通道,速率高达 24.75 Gbps

- 每个 DAC 和 ADC 8 个通道

- 与最大 15.5 Gbps 的通道速率兼容的 JESD204B

- 与最大 24.75 Gbps 的通道速率兼容的 JESD204C

- 支持实数或复数数字数据(8、12、16 或 24 位)

- 15毫米××15毫米、324 球 BGA,间距 0.8 毫米

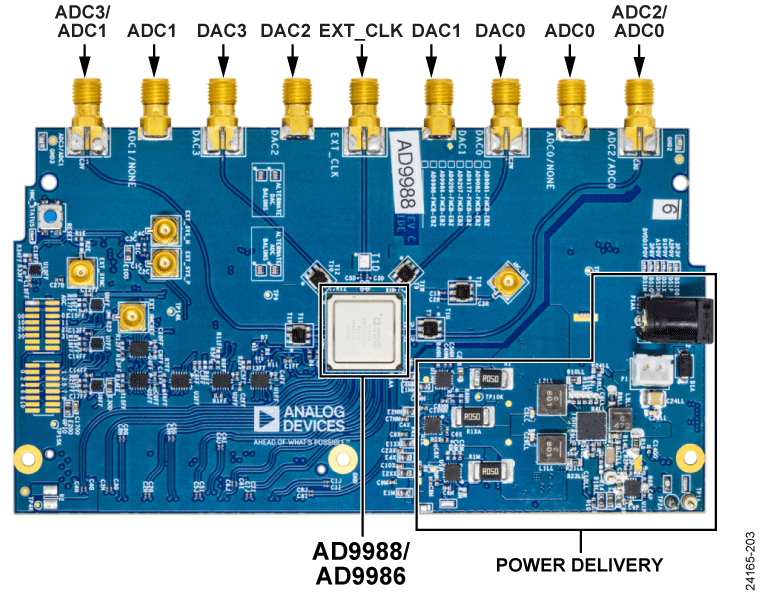

AD9986是一款高度集成的器件,搭载16位、12 GSPS最大采样速率的RF数模转换器(DAC)内核,以及12位、6 GSPS采样速率的RF模数转换器(ADC)内核。AD9986支持四个发射器通道和两个接收器通道,采用四个发射器、两个接收器(4T2R)配置。AD9986非常适合数字预失真观测接收器路径需要宽带宽的2天线和4天线发射器应用。AD9986在单通道模式下支持高达6 GSPS的复数发送和接收数据速率。发送和接收路径支持的最大无线电信道带宽分别为1.2 GHz和2.4 GHz (4T2R)。AD9986具有16通道24.75 Gbps JESD204C或15.5 Gbps JESD204B串行数据端口、片内时钟倍频器和数字信号处理功能,适合多频段直接至RF射频应用。

应用

- 无线通信基础设施

- W-CDMA、LTE、LTE-A、大规模MIMO

- 微波点对点、E频段和5G毫米波

- 宽带通信系统

- DOCSIS 3.1和4.0 CMTS

- 通信测试与测量系统

参考资料

数据手册 1

用户手册 2

应用笔记 1

技术文章 2

FPGA 互操作性报告 5

产品选型指南 1

3rd Party Solutions 1

器件驱动器 1

ADI 始终高度重视提供符合最高质量和可靠性水平的产品。我们通过将质量和可靠性检查纳入产品和工艺设计的各个范围以及制造过程来实现这一目标。出货产品的“零缺陷”始终是我们的目标。查看我们的质量和可靠性计划和认证以了解更多信息。

| 产品型号 | 引脚/封装图-中文版 | 文档 | CAD 符号,脚注和 3D模型 |

|---|---|---|---|

| AD9986BBPZ-4D2AC | 324-Ball BGA_ED (15mm x 15mm x 1.58mm) | ||

| AD9986BBPZRL-4D2AC | 324-Ball BGA_ED (15mm x 15mm x 1.58mm) |

这是最新版本的数据手册

软件资源

API Device Drivers 1

Device Application Programming Interface (API) C code drivers provided as reference code that allows the user to quickly configure the product using high-level function calls. The library acts as an abstraction layer between the application and the hardware. The API is developed in C99 to ensure agnostic processor and operating system integration. Customers can port this application layer code to their embedded systems by integrating their platform-specific code base to the API HAL layer.

To request this software package, go to the Software Request Form signed in with your MyAnalog account and under “Target Hardware” select “High Speed Data Converters” and choose the desired API product package. In addition, there are two SW packages available specifically for Apollo MxFE™. There is a PyApp/ACE evaluation package and there are FPGA bin files supporting various use cases. You will receive an email notification once the software is provided to you.

器件驱动器 2

Evaluation Software 1

JESD204x Frame Mapping Table Generator

The JESD204x Frame Mapping Table Generator tool consists of two Windows executables that will allow the user to input any valid combination of JESD204x parameters (L, M, F, S, NP) in order to output a .csv file that illustrates the frame mapping of the JESD204x mode in table format. There is an executable that allows the user to input a single JESD204x mode and another, that allows the user to input the parameters for multiple JESD204x modes in a specified .csv format in order to output a .csv file that illustrates the frame mapping of each of the JESD204x modes that were input into separate tables.

找不到您所需的软件或驱动?

硬件生态系统

| 部分模型 | 产品周期 | 描述 |

|---|---|---|

| µModule降压稳压器 1 | ||

| LTM8053 | 推荐用于新设计 | 40VIN、3.5A/6A 降压型超低噪声开关稳压器 μModule 稳压器 |

| 超低噪声稳压器 1 | ||

| LTM8063 | 推荐用于新设计 | 40VIN、2A Silent Switcher µModule 稳压器 |

| 多个输出降压调节器 3 | ||

| LTM4633 | 推荐用于新设计 | 三输出 10A 降压型 DC/DC μModule 稳压器 |

|

LTM4644 LTM4644-1 |

具有可配置4A输出阵列的四通道DC/DC μModule(电源模块)稳压器 | |

| LTM4616 | 推荐用于新设计 | 每通道 8A 输出的双通道、低 VIN DC/DC µModule 稳压器 |

| 集成VCO的锁相环 1 | ||

| ADF4377 | 推荐用于新设计 | 带集成 VCO 的微波宽带频率合成器 |

| 全差分放大器 2 | ||

| ADL5569 | 推荐用于新设计 | 6.0 GHz、超高动态范围、差分放大器 |

| ADL5580 | 推荐用于新设计 | 具有 10 dB 增益的全差分 10 GHz ADC 驱动器 |

| 时钟产生器件 2 | ||

| LTC6952 | 最后购买期限 | 具有 11 个输出并支持 JESD204B / JESD204C 协议的超低抖动、4.5GHz PLL |

| HMC7044 | 推荐用于新设计 | 带JESD204B接口的高性能、3.2 GHz、14路输出抖动衰减器 |

| 时钟分配器件 3 | ||

| HMC7043 | 推荐用于新设计 |

高性能、3.2 GHz、14输出扇出缓冲器 |

| LTC6953 | 最后购买期限 | 具有 11 个输出并支持 JESD204B/JESD204C 协议的超低抖动、4.5GHz 时钟分配器 |

| LTC6955 | 最后购买期限 | 超低抖动 7.5GHz 11 输出扇出缓冲器系列 |

| 数字控制VGA 2 | ||

| ADL6316 | 推荐用于新设计 | 适用于 RF DAC 和收发器的 500 MHz 至 1000 MHz 发射 VGA |

| ADL6317 | 推荐用于新设计 | 用于 RF DAC 和收发器的发射 VGA |

| 正线性稳压器(LDO) 4 | ||

| ADP1765 | 推荐用于新设计 | 5 A、低VIN、低噪声、CMOS线性稳压器 |

| ADP7158 | 推荐用于新设计 |

2 A、超低噪声、高PSRR、固定输出、RF线性稳压器 |

| ADM7172 | 推荐用于新设计 |

6.5 V、2 A、超低噪声、高 PSRR、快速瞬态响应 CMOS LDO |

| ADM7150 | 推荐用于新设计 | 800 mA、超低噪声/高 PSRR LDO |

工具及仿真模型

ADC Companion Transport Layer RTL Code Generator Tool

This command line executable tool generates a Verilog module which implements the JESD204 receive transport layer. The user specifies in a configuration file one or more modes to be supported by the transport layer module. These modes are defined as a set of JESD204 parameter values: L, M, F, S, N', and CF. The transport layer converts JESD204 lane data output from a JESD204 link layer IP to a data bus with a fixed width, containing interleaved virtual converter samples. Both JESD204B and JESD204C link layers are supported.

打开工具ADIsimPLL™

ADIsimPLL可以对ADI公司最新的高性能PLL产品进行快速、可靠的评估。它是目前最全面的PLL频率合成器设计和仿真工具,可实现所有对PLL性能有显著影响的重要非线性效应仿真。ADIsimPLL可以免去设计过程中的至少一项重复劳动,从而加快上市速度。

打开工具DAC Companion Transport Layer RTL Code Generator

These command line executable tool generates a Verilog module which implements the JESD204 transmitter transport layer. The user specifies in a configuration file one or more modes to be supported by the transport layer module. These modes are defined as a set of JESD204 parameter values: L, M, F, S, N', and CF. The transport layer converts JESD204 lane data output from a JESD204 link layer IP to a data bus with a fixed width, containing interleaved virtual converter samples. Both JESD204B and JESD204C link layers are supported.

打开工具MxFE JESD204 Mode Selector Tool

The JESD204B/C Mode Selector Tool is a simple command line-based Windows executable that can be used to narrow down the number of JESD204x modes to only include those modes that support the user’s specific application use case. The tool guides the user through a use case description flow chart and gives the user a small list of applicable transmit and/or receive modes to choose from. This tool is applicable to the AD9081, AD9082, AD9177, AD9207, AD9209, AD9986, and AD9988.

打开工具