LTC6950

製造中止クロック分配回路を内蔵した1.4GHz低位相ノイズ、低ジッタPLL

- 製品モデル

- 1

- 1Ku当たりの価格

- 価格は未定

製品の詳細

- 低位相ノイズおよび低ジッタ

- 付加ジッタ:18fsRMS(12kHz~20MHz)

- 付加ジッタ:85fsRMS(10Hz~ナイキスト周波数)

- EZSync™マルチチップ・クロック・エッジ同期

- ロック表示機能を備えた完全なPLLコア

- 正規化された帯域内位相ノイズフロア:–226dBc/Hz

- 正規化された1/f位相ノイズ:–274dBc/Hz

- VCO入力周波数:最大1.4GHz

- 独立した4つの低ノイズ1.4GHz LVPECL出力

- 構成可能な1つのLVDS/CMOS出力

- 1から63までのすべての整数を対象範囲とする個別にプログラム可能な5つのドライバ

- 0から63までのすべての整数を対象範囲とする個別にプログラム可能な5つのVCOクロック・サイクル遅延回路

- 接合部温度範囲:-40°C~105°C

- ClockWizardソフトウェア設計ツールによるサポート

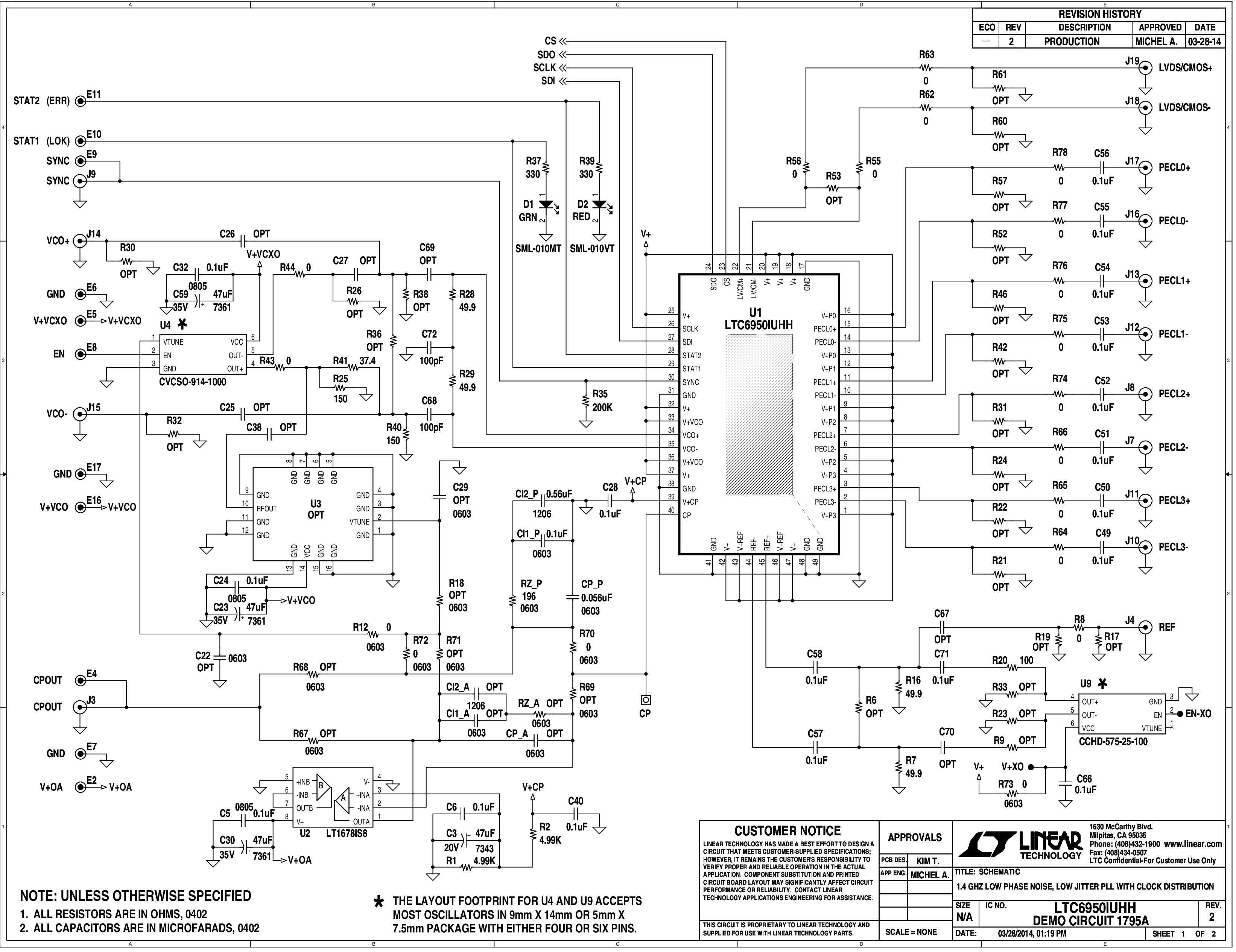

LTC®6950は、クロック分配回路を内蔵した、低位相ノイズの整数分周方式周波数シンセサイザ・コアです。LTC6950は、高周波、高分解能のデータ収集システムで要求される低位相ノイズのクロック信号を供給します。

この周波数シンセサイザは、低ノイズの完全なPLLコアの他に、プログラム可能なリファレンス分周器(R)、プログラム可能な帰還分周器(N)、位相/周波数検出器(PFD)、および低ノイズのチャージポンプ(CP)を内蔵しています。LTC6950のクロック分配部は、VCO入力に基づいて最大5つの出力を供給します。1~63の任意の整数でVCO入力周波数を分周し、0~63のVCOクロック・サイクルだけ出力を遅延させるため、各出力は個別にプログラムされます。出力のうち4つは、ノイズが非常に低く、低スキューで、最大1.4GHzの動作が可能なLVPECLロジック信号を特長としています。5番目の出力は、ロジック・タイプとしてLVDS(800MHz)またはCMOS(250MHz)を選択可能です。また、この出力は、VCO入力またはリファレンス分周器出力に基づいて出力信号を生成するようプログラムすることもできます。

Applications

- 高速、高分解能のADC、DAC、およびデータ収集システムのクロック制御

- 低ジッタのクロック信号生成および分配

ドキュメント

データシート 2

信頼性データ 1

ユーザ・ガイド 1

アプリケーション・ノート 1

技術記事 2

ソリューション・カタログ 1

製品セレクタ・カード 3

プレス・リリース 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| LTC6950IUHH#TRPBF | 48-Lead QFN (5mm x 9mm x 0.75mm w/ EP) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

9 24, 2021 - 21_0121 Obsolescence of LTC6945, LTC6946, and LTC6950 |

||

| LTC6950IUHH#TRPBF | 製造中止 | |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

評価用ソフトウェア 1

ClockWizard

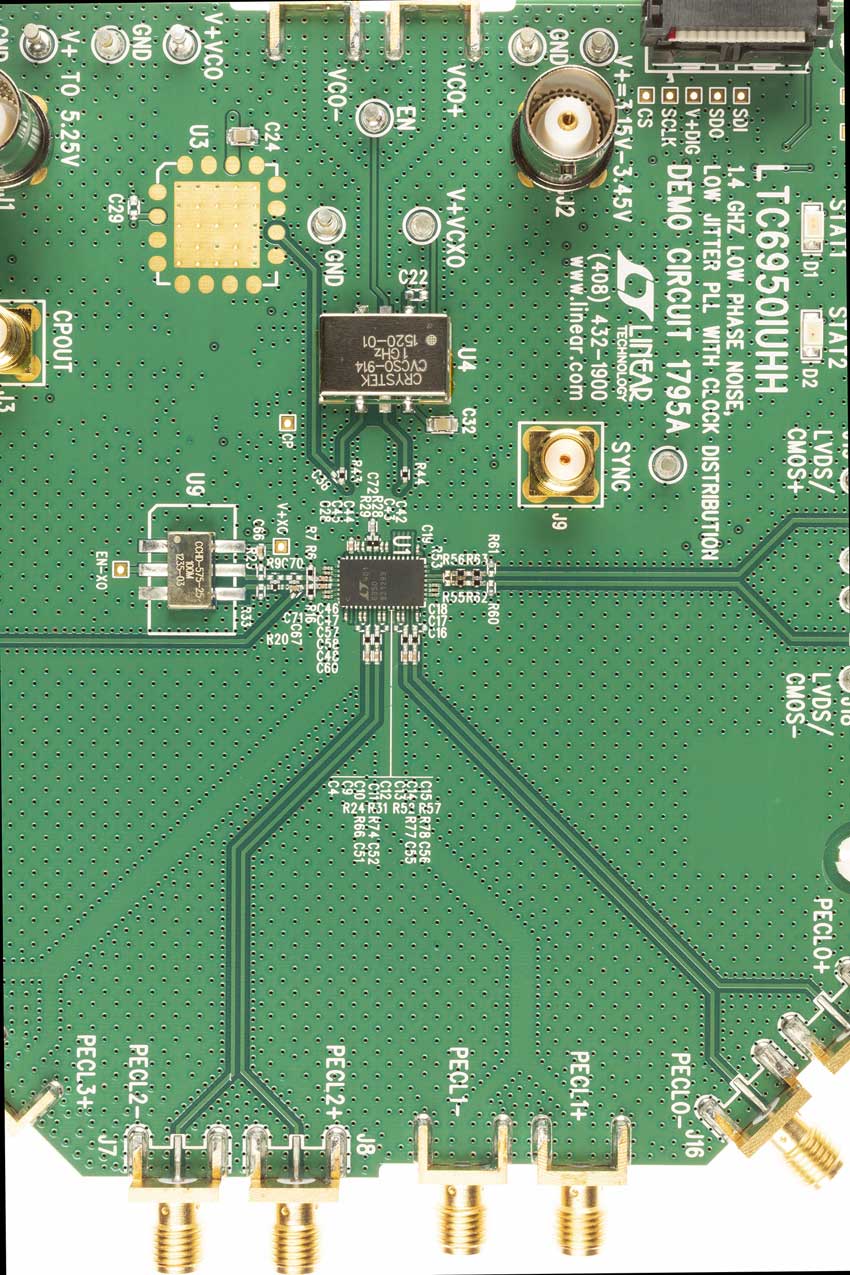

ClockWizard は 、PLLWizard をベースとしており、LTC6950 の評価プロセスを簡単に実行できます。ループ・フィルタ・コンポーネントを設計して最終的な位相ノイズとジッタ性能を予測できるだけでなく、 LTC6950 の出力を時間領域で表示し、それぞれの EZSync 設定に基づいて出力間の位相関係を確認できるスコープ・プロットを採用しています。また、DC590 または DC2026 によって LTC6950 デモ・ボードを制御できます。

必要なソフトウェア/ドライバが見つかりませんか?

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| クロック分配器 (クロック・ディストリビューション) 2 | ||

| LTC6954 | 最終販売 | 低位相ノイズ、トリプル出力クロック分配分周器/ドライバ |

| HMC1031 | 最終販売 | 0.1 MHz ~ 500 MHz のクロック・ジェネレータ、インテジャー N PLL 付き |

| シグナル・チェーン µModule レシーバー 1 | ||

| LTM9013 | 最終販売 | 300MHz広帯域レシーバ |

| 高速コンパレータ(伝播遅延100ns未満) 1 | ||

| LTC6957 | 位相ノイズの小さいデュアル出力バッファ/ドライバ/ロジック・コンバータ | |

| 標準の高速A/Dコンバータ 2 | ||

| LTC2157-14 | 製造中 | デュアル、14ビット、250Msps ADC |

| LTC2208 | 製造中 | 16ビット、130Msps ADC |

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| LTC6951 | 最終販売 | 超低ジッタ VCO内蔵の複数出力 クロック・シンセサイザ |

ツールおよびシミュレーション

Linduino 3

IBISモデル 1

Linduino はアナログ・デバイセズの Arduino 互換システムで、アナログ・デバイセズ製集積回路のファームウェア・ライブラリおよびサンプル・コードの開発と配布に使用します。Linduino対応の各製品には、LTSketchbook/Part Numberフォルダに定義されたサンプルのメイン・プログラムと、LTSketchbook/librariesフォルダに定義されたドライバ・コードが含まれています。