ADSP-21837

発売前Up to 1 GHz SHARC®-FX DSP

- 製品モデル

- 2

- 1Ku当たりの価格

- 価格は未定

製品の詳細

System Features

- SHARC-FX high performance floating-point core

- 256-bit vector size

- Peak performance at 1 GHz core frequency: 24 GFLOPS, 8 GMAC (32-bit float), 16 GMAC (16-bit fixed)

- 64/512 kB L1 instruction/data RAM with ECC

- 32/256 kB L1 instruction/data cache with ECC

- Arm Cortex-M33 connectivity core

- 400 MHz frequency, 64/128 kB instruction/data RAM with parity protection

- Memory

- Parallel operation with dedicated memory, DMA, and multichannel support

- Up to 16 Mb (2 MB) on-chip L2 SRAM with ECC protection

- One Level 3 (L3) 16-bit interface to DDR3L SDRAM devices

- On-board accelerators

- Two FIR engines (up to 1 GHz, 4 taps per cycle)

- Four IIR engines (up to 1 GHz, 6 cycles per biquad each)

- Security

- Cryptographic hardware accelerators

- Fast secure boot with IP protection

Package, Key Peripherals, and Compatibility

- 17 mm × 17 mm, 400-ball BGA_ED (0.8 mm pitch), RoHS compliant

- Ethernet, HyperBus, CAN-FD, HADC, I2C, ASRC/SPORT

- ADSP-2156x and ADSP-2159x layout-compatible options

The ADSP-2183x/ADSP-SC83x digital signal processors (DSPs) are members of the SHARC®-FX family of products. The SHARC-FX core uses a single-instruction, multiple-data (SIMD) vector floating-point architecture and can issue up to four instructions per cycle in most combinations. The SHARC-FX core inside the ADSP-2183x/ADSP-SC83x processors offers processing speeds of up to 1 GHz coupled with up to 2 MB of L2 memory for low latency applications. For applications seeking enhanced connectivity options such as Ethernet, the ADSP-SC834/SC835 includes an Arm® Cortex®-M33 in addition to the SHARC-FX core. All members of the SHARC-FX family have on-board IIR and FIR accelerators as well as an efficient auto-vectorizing compiler for C/C++ programming.

The SHARC-FX core supports scalar and vector operations on all data types in vectors up to 256 bits, including integer, fixed-point, floating-point, complex 16-bit/32-bit fixed-point and complex 32-bit/64-bit floating-point. Eight float32 multiply/accumulate operations are allowed per cycle, with no constraints on alignment. The SHARC-FX core also features large register sets (32 data registers), thus reducing the need for stack save and restore. The peripherals and system architecture of the ADSP-2183x/ADSP-SC83x processors are compatible with previous SHARC processors, allowing for easy application porting.

By integrating a set of industry-leading system peripherals and memory, this family of processors is the platform of choice for applications that require leading-edge signal processing in one integrated package. These applications span a wide array of markets, including automotive, professional audio, and industrial-based applications that require high floating-point performance.

Applications

- Automotive:

- audio for head units and amplifiers, ANC/RNC, digital cockpit, ICC, AEC/Mic beamforming, ADAS

- Consumer:

- speakers, sound bars, AVRs, conferencing systems, mixing consoles, microphone arrays

ドキュメント

データシート 1

ユーザ・ガイド 1

アプリケーション・ノート 4

集積回路異常 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| ADSP-21837KBPZ10 | 400-Ball BGA_ED (17mm x 17mm x 1.649mm) | ||

| ADSP-21837KBPZ8 | 400-Ball BGA_ED (17mm x 17mm x 1.649mm) |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

ツールおよびシミュレーション

BSDLモデル・ファイル 1

熱モデル 1

IBISモデル 1

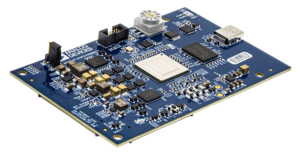

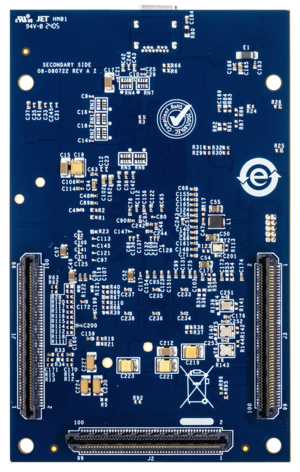

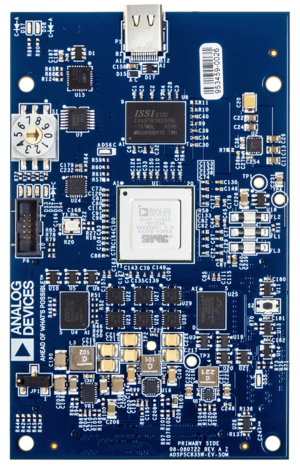

評価用キット

最新のディスカッション

ADSP-21837に関するディスカッションはまだありません。意見を投稿しますか?

EngineerZone®でディスカッションを始める