アプリケーション・ノート使用上の注意

本アプリケーションノートの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、リビジョンが古い場合があります。最新の内容については、必ず最新の英語版をご参照ください。

なお、日本語版のアプリケーションノートは基本的に「Rev.0」(リビジョン0)で作成されています。

AN-1026:高速差動ADC ドライバの設計についての考察

はじめに

最新の高性能ADC は、そのほとんどが差動入力を使用して、同相ノイズと干渉を除去し、ダイナミック・レンジを2 倍に増大し、平衡信号送信により全体の性能を改善しています。差動入力ADC はシングル・エンド入力信号も入力可能ですが、最適な特性が得られるのは入力信号が差動の場合です。ADC ドライバ(このような信号を出力するためにしばしば特別に設計される回路)は振幅スケーリング、シングル・エンドto 差動入力変換、バッファ処理、同相オフセット調整、フィルタ処理などの多数の重要な機能を実行します。AD8138 の発売以来、差動ADC ドライバはデータ・アクイジション・システムで必要不可欠なシグナル・コンディショニング部品になりました。

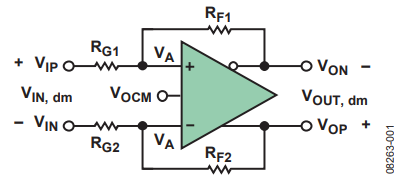

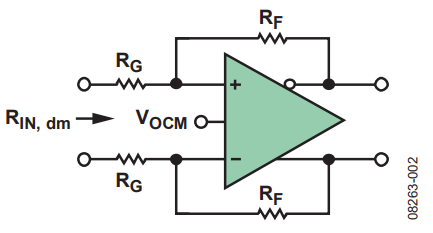

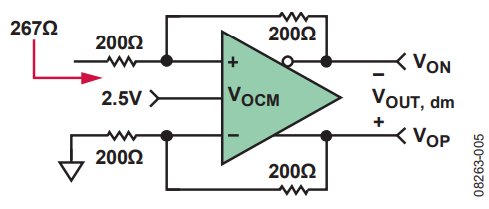

基本的な完全差動電圧フィードバックADC ドライバを図1 に示します。従来のオペアンプ帰還回路とは2 つの違いがあることがわかります。差動ADC ドライバには新たに出力端子(VON)と入力端子(VOCM)が追加されています。これらの端子は差動入力のあるADC に信号をインターフェースする場合に非常に便利です。

図1. 差動アンプ

差動ADCドライバはシングル・エンド出力の代わりに、VOCMを基準とした平衡差動出力をVOP とVON の間に生じます(P は正を、N は負を表します)。VOCM 入力は出力同相電圧をコントロールします。入出力信号が仕様規定範囲内である限り、出力同相電圧はVOCM 入力に印加された電圧に等しくなります。負帰還と高オープンループ・ゲインにより、アンプ入力端子電圧のVA+とVA−は基本的に等しくなります。

今後の説明のために、いくつかの定義を順に説明します。入力信号が平衡であれば、VIP とVIN は通常共通のリファレンス電圧を基準にして振幅は同じで位相が反対になります。入力がシングル・エンドの場合は、一方の入力が固定電圧で他方がその電圧を基準に変化します。いずれの場合も、入力信号はVIP − VINとして規定されます。

差動モード入力電圧(VIN,dm)と同相モード入力電圧(VIN,cm)は式1 と式2 で規定されます。

この同相の定義は平衡入力に印加される場合には直感的に理解できますが、シングル・エンド入力でも有効です。

出力もまた差動モードと同相モードがあり、式3 と式4 で規定されます。

実際の出力同相モード電圧(VOUT,cm)と(出力同相モード・レベルを設定する)VOCM 入力端子との間の差に注意してください。

差動ADC ドライバの解析は従来のオペアンプの解析よりもかなり複雑です。代数を簡略化するために式5、式6 に示すように2つの帰還係数β1、β2 を定義すると便利です。

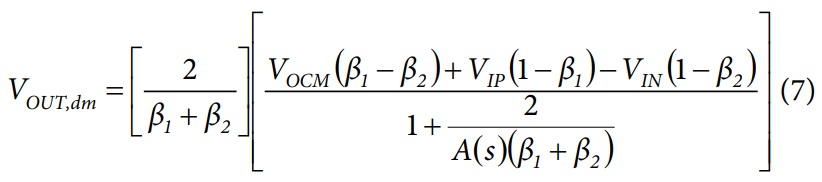

ほとんどの ADC ドライバでは β1 = β2 です。しかしベータのミスマッチが性能にどのように影響するかについて理解するのに、VIP、VIN、VOCM、β1、β2 の項をもつ VOUT, dm の一般的な閉ループ公式は役に立ちます。式 7 に示す VOUT, dm の式にはアンプの有限で周波数に依存するオープンループ電圧ゲイン、A(s)が含まれています。

β1 ≠ β2 の時、差動出力電圧は VOCM に依存します。これは差動出力にオフセットと余分なノイズを生じるので、望ましくない結果になります。電圧帰還構成のゲイン帯域幅積は一定です。ゲイン帯域幅積のゲインは 2 つの帰還率の平均の逆数です。

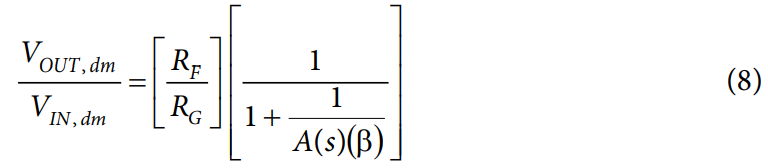

β1 = β2 ≡ β のとき、式7 は式8 のように短縮されます。

式8 の方がより見慣れた式になっており、A(s)が∞に近づくと、理想的な閉ループ・ゲインは単にRF/RG になります。ゲイン帯域幅積もまた、ノイズ・ゲインが1/β になるので、ちょうど従来のオペアンプの場合のようによく知られた形になります。

帰還係数がマッチングしている差動ADC ドライバの理想的な閉ループ・ゲインは式9 になります。

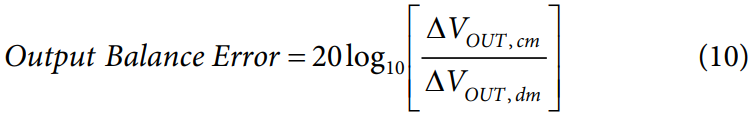

差動ADC ドライバの重要な性能指標である出力平衡には、振幅平衡と位相平衡の2 つの要素があります。振幅平衡は2 つの出力の振幅がどのくらい一致しているかを表す尺度です。理想的なアンプではそれらは正確に一致しています。出力位相平衡は2 つの出力間の位相差がどのくらい180°に近いかを表す尺度です。出力振幅または出力位相のどのような不平衡も出力に好ましくない同相成分を生じます。出力平衡誤差(式10)は差動入力信号によって生成される出力同相電圧の、(同じ入力信号によって生成される)出力差動モード電圧に対する対数比で、デシベルで表されます。

内部の同相帰還ループによりVOUT, cm がVOCM 入力に印加される電圧に等しくなり、優れた出力平衡を生みます。

ADC ドライバに対する入力の終端

ADC ドライバは高速信号を処理するシステムで頻繁に使用されます。複数のデバイス間の距離が信号波長のごく一部に過ぎない場合でも、信号のもとの波形を損なわないようにインピーダンス整合された電気伝送ラインで接続されなければなりません。伝送ラインの両端を特性インピーダンスで終端した場合に、最適の性能が得られます。ドライバは一般的にADC の近くに配置されるのでそれらの間にインピーダンス整合した接続の必要はありませんが、しばしばADC ドライバ入力までの信号経路が長いことがあるので、その場合適切な抵抗で終端してインピーダンス整合した接続をする必要があります。

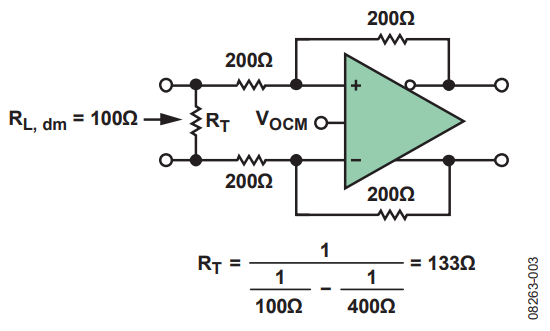

終端抵抗RT をアンプ入力と並列に追加して必要な抵抗値を実現できるように、(差動であろうとシングル・エンドであろうと)ADC ドライバの入力抵抗は、目的の終端抵抗以上でなければなりません。ここで検討する例に出てくるすべてのADC ドライバは図2 に示したようにバランスのとれたフィードバック比を持つように設計されています。

図2. 差動アンプ入力インピーダンス

アンプの2 つの入力間の電圧は負帰還によりゼロになるように動作するので、これらは実質的に接続されており、差動入力抵抗RIN は単純に2 × RGになります。伝送ライン抵抗RLに整合させるために、差動入力の間に式11 で計算した値のRT を接続します。図3 に標準的な抵抗RF = RG = 200Ω、要求される抵抗RL, dm = 100Ω とRT = 133Ωを示します。

図3. 100Ω ラインに整合

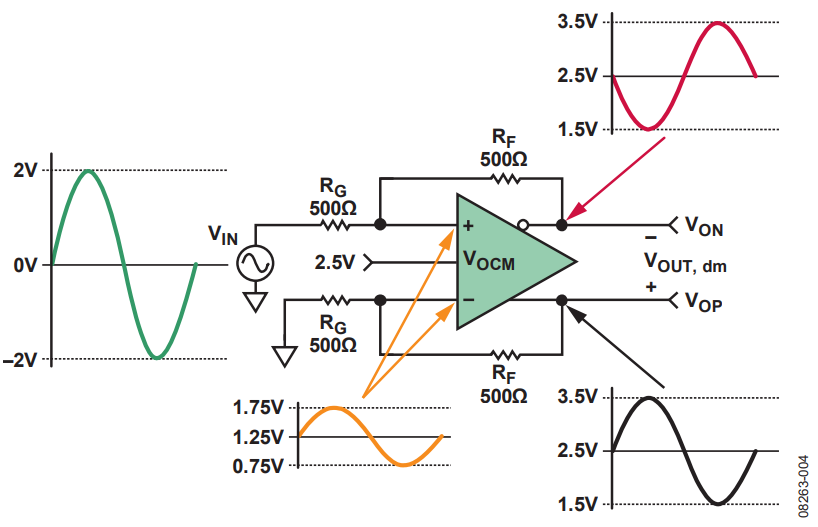

シングル・エンド入力を終端することはより多くの努力を必要とします。図4 はシングル・エンド入力、差動出力回路でADCドライバがどのように動作するかを示しています。

図4. ADC ドライバへのシングル・エンド入力の例

入力はシングル・エンドですが、VIN, dm はVIN に等しくなります。抵抗RF とRG は等しくバランスがとれているので、ゲインは1で、差動出力、VOP − VON は入力電圧、すなわち、4Vp-p に等しくなります。VOUT, cm はVOCM = 2.5V に等しく、また入力電圧VA+とVA−は、下側の帰還回路により、VOP/2 に等しくなります。

式3 と式4 を使うと、VOP = VOCM + VIN/2 となり2.5V を基準に±1V 同相スイングします。またVON = VOCM − VIN/2 となり2.5V を基準に±1V 逆相スイングします。したがって、VA+とVA−は1.25V を基準に±0.5V スイングします。VIN から供給しなければならない電流のAC 成分は(2V − 0.5V)/500Ω = 3mA です。したがって、VINから見て整合をとらなければならないグラウンドに対する抵抗は、667Ω です。

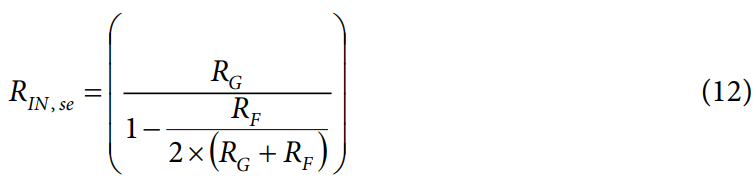

各々のループの帰還率がマッチングしている場合、このシングル・エンド入力抵抗を計算する一般的な公式は式12 で表せます。ここでRIN, seはシングル・エンド入力抵抗です。

これは終端抵抗を計算するスタート点です。ただし、アンプ・ゲインの式は入力源インピーダンスをゼロと仮定していることに注意することが重要です。大きな信号源インピーダンスはシングル・エンド入力に起因した非平衡が存在する状態でマッチングしなくてはならないので、本質的に上側のRG にのみ抵抗が追加されます。平衡を保つために、下側のRG に抵抗を追加してこれをマッチングさせなければなりませんが、それはゲインに影響します。

シングル・エンド信号を終端することの問題に対して閉形式で解を決めることは可能かもしれませんが、反復法が一般的に使用されます。その必要性は次の例で明らかです。

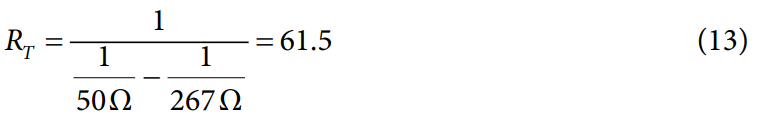

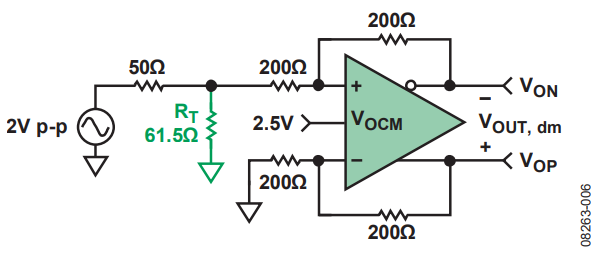

図5 は、シングル・エンドto 差動のゲインが1、入力終端抵抗が50Ω、そしてノイズを低く保つために、フィードバック抵抗とゲイン抵抗を約200Ω 付近の値にしています。

図5. シングル・エンド入力インピーダンス

式12 からシングル・エンド入力抵抗は267Ω になります。式13から入力抵抗267Ω を50Ω に下げるためには、並列抵抗、RT を61.5Ω にしなければならないことがわかります。

図6 は信号源抵抗と終端抵抗を示した回路です。信号源の解放回路電圧は2Vp-p で、信号源抵抗は50Ω です。信号源が50Ω に終端されると、入力電圧は1Vp-p に減少します。また、これはユニティゲイン・ドライバの差動出力電圧になります。

図6. 信号源と終端抵抗を加えたシングル・エンド回路

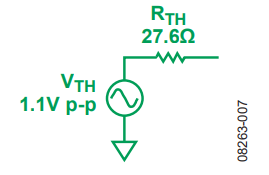

この回路は一見完全に見えますが、50Ω と並行に、ミスマッチした抵抗61.5Ω が上側のRG にのみ追加されています。この追加により、ゲインとシングル・エンド入力抵抗が変化し、帰還係数がミスマッチします。ゲインが小さいので、入力抵抗の変化は小さく、さしあたり無視されます、しかし帰還率はマッチングしていなければなりません。これを可能する最も簡単な方法は下側のRG に抵抗を加えることです。図7 はテブナン等価回路を示しますが、ここで前述した並列組み合わせ回路が信号源抵抗として働きます。

図7. 入力信号源のテブナン等価回路

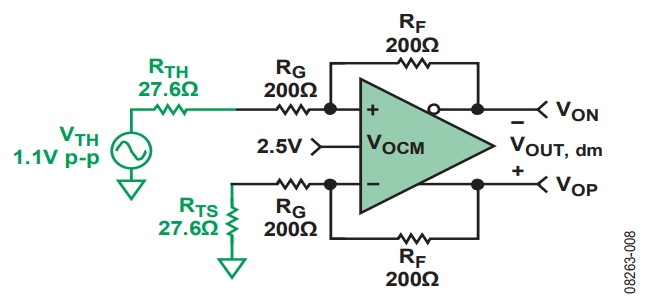

図8 に示すように、ループ帰還係数をマッチングさせるために、この置き換え回路に合わせて下側ループに27.6Ω の抵抗RTSを追加します。

図8. 平衡シングル・エンド終端回路

1.1Vp-p のテブナン電圧は適切に終端された電圧1Vp-p よりも大きくなり、ゲイン抵抗はそれぞれ27.6Ω 増えるので、閉ループ・ゲインが減少することに注意してください。これら出力電圧に対して相反する影響は、抵抗が大きく(>1kΩ)ゲインが小さい(1 または2)場合は、互いに相殺する傾向にありますが、抵抗が小さくゲインが高い場合には完全には相殺されません。

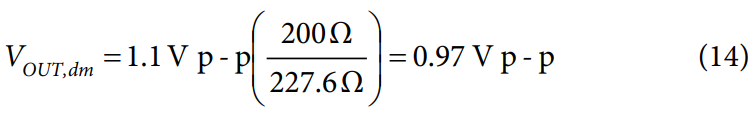

図8 の回路は簡単に解析することができ、差動出力電圧は式14で計算することができます。

差動出力電圧は目的の電圧レベル1Vp-p とまったく同じというわけではありませんが、式15 に示したようにフィードバック抵抗を変更することにより最終的な独立したゲイン調整が可能です。

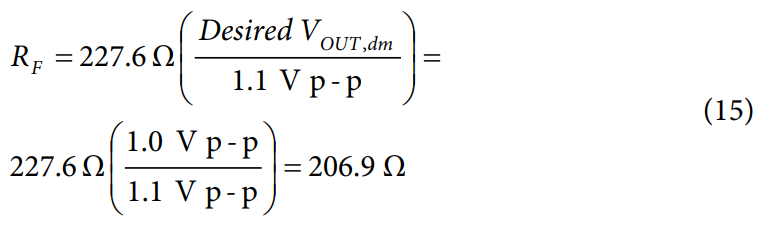

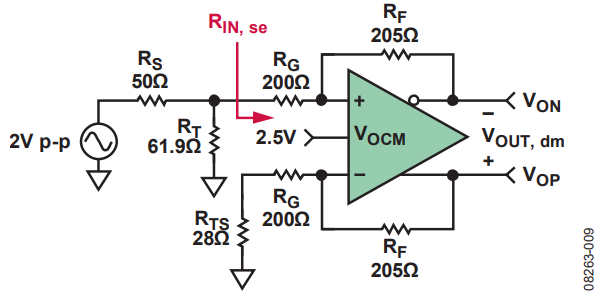

図9 に完成した回路を示します。ここで使用する抵抗の値は標準的な1%抵抗のものです。

図9. 完全シングル・エンド終端回路

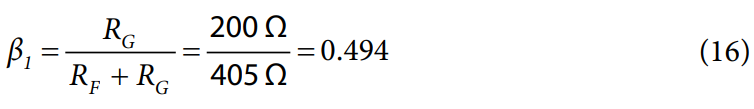

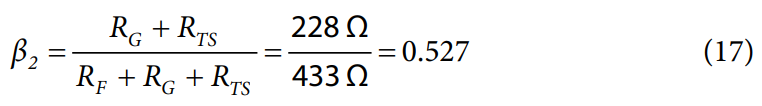

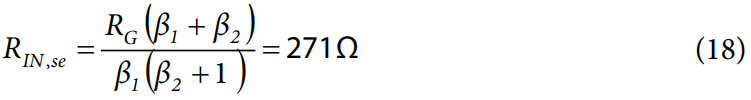

図9 の回路に関して、ドライバのシングル・エンド入力抵抗RIN,se はRF とRG の変更により変わります。ドライバの上側ループのゲイン抵抗は200Ω で、下側ループのゲイン抵抗は200Ω +28Ω = 228Ω です。ゲイン抵抗が違う場合は、RIN, seの計算を行う前に式16 と式17 に示すように2 つベータ値を計算する必要があります。

入力抵抗RIN, se は式18 に示すように計算します。この値は始めに計算した値267Ω とほとんど変わらず、RT の計算に大きな影響はありません。なぜならRIN, seはRT とは並列だからです。

もしもっと正確な全体のゲインが必要であれば、より高精度な抵抗または直列トリム抵抗を使用することができます。

ここで述べた1 度の反復計算方法は閉ループ・ゲインが1 または2 の時はよく当てはまります。ゲインが更に高い場合、RTS の値はRG の値に近くなり、式18 で計算したRIN, se の値と式12 で計算した値の差は大きくなります。このような場合には何回かの反復計算が必要です。

入手可能な差動アンプ計算ツールであるADI Diff Amp Calculator™ は、直感的なユーザ・インターフェースで前述の計算を実行します。

入力同相電圧範囲(ICMVR)

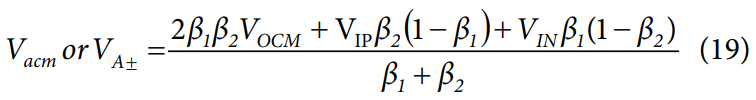

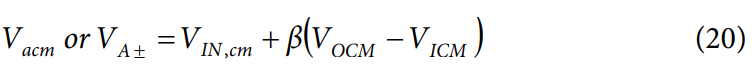

ICMVR は通常動作で差動アンプ入力に加えることのできる電圧範囲を規定します。差動アンプ入力に現れる電圧はICMV、VacmまたはVA±と呼ばれています。この仕様はしばしば誤解されます。差動アンプ入力での実際の電圧を、特に入力電圧基準で決めるのはかなり困難です。アンプ入力電圧(VA±)は変数VIN,cm、β、VOCM が既知の場合、βs が異なるときは一般的な式19 を使い、βs が同じときは簡略化した式20 を使って計算することができます。

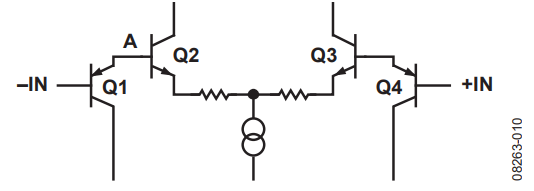

VA は、図4 に示すように、常に入力信号のスケールを小さくしたバージョンであることに注意してください。入力同相電圧範囲はアンプのタイプによって異なります。アナログ・デバイセズの高速差動ADC ドライバにはICMVR が電源の中点を中心に設定されているもの(centered)とICMVR の中点が電源の中点からシフトされたもの(shifted)の2 種類の入力段構成があります。ICMVR が電源の中点を中心に設定されているADC ドライバは各々の電源レールから約1V のヘッドルームがあります。ICMVR の中点がシフトされた入力段には2 つのトランジスタが追加されており、入力が−VS レールにより近くスイングできるようになっています。図10 は代表的な差動アンプ(Q2 とQ3)の簡略化した入力回路を示します。

図10. シフトされたICMVR の簡略化した差動アンプ

ICMVR をシフトした入力回路構成の差動アンプは、例え単電源駆動でもバイポーラ入力信号の処理が可能で、入力がグラウンドまたはそれ以下になる単電源アプリケーションに十分対応できます。入力に追加したPNP トランジスタ(Q1 とQ4)により、差動ペアへ入力する入力電圧が1 トランジスタのVBE 分上にシフトします。例えば−IN に−0.3V を印加した時、A 点(図10 参照)は0.7V になり差動ペアが正常に動作します。PNP がない場合(中心入力段の場合)、A 点の-0.3V により、NPN 差動ペアに逆バイアスがかかり、通常動作が停止します。

表1 はアナログ・デバイセズのADC ドライバの多くの仕様に対する早見表で、どのドライバがICMVR をシフトしたものか、どのドライバがそうでないかの情報も含まれています。

| ADC Driver | Supply Voltage (V) | Output Swing from Rails (V) | ISUPPLY(mA) | ||||||||||

| ICMVR | VOCM | ||||||||||||

| Part No. |

BW (MH) |

Slew Rate (V/µs) |

Noise (nV) | ±5 V1 | +5 V | +3.3 V1 | +3 V1 | ±5 V | +5 V | +3.3 V1 | +3 V1 | ||

| AD8132 | 350 | 1200 | 8 | −4.7 to +3 | 0.3 to 3 | 0.3 to 1.3 | 0.3 to 1 | ±3.6 | 1 to 3.7 | N/A | 0.3 to 1 | ±1 | 12 |

| AD8137 | 76 | 450 | 8.25 | −4 to +4 | 1 to 4 | 1 to 2.3 | 1 to 2 | ±4 | 1 to 4 | 1 to 2.3 | 1 to 2 | Rail to rail | 3.2 |

| AD8138 | 320 | 1150 | 5 | −4.7 to +3.4 | 0.3 to 3.2 | N/A | N/A | ±3.8 | 1 to 3.8 | N/A | N/A | ±1.4 | 20 |

| AD8139 | 410 | 800 | 2.25 | −4 to +4 | 1 to 4 | N/A | N/A | ±3.8 | 1 to 3.8 | N/A | N/A | Rail to rail | 25 |

| ADA4927-1/ADA4927-2 | 2300 | 5000 | 1.4 | −3.5 to +3.5 | 1.3 to 3.7 | N/A | N/A | ±3.5 | 1.5 to 3.5 | N/A | N/A | ±1.2 | 20 |

| ADA4932-1/ADA4932-2 | 1000 | 2800 | 3.6 | −4.8 to +3.2 | 0.2 to 3.2 | N/A | N/A | ±3.8 | 1.2 to 3.2 | N/A | N/A | ±1 | 9 |

| ADA4937-1/ADA4937-2 | 1900 | 6000 | 2.2 | N/A | 0.3 to 3 | 0.3 to 1.2 | N/A | N/A | 1.2 to 3.8 | 1.2 to 2.1 | N/A | ±0.9 | 40 |

| ADA4938-1/ADA4938-2 | 1000 | 4700 | 2.6 | −4.7 to +3.4 | 0.3 to 3.4 | N/A | N/A | ±3.7 | 1.3 to 3.7 | N/A | N/A | ±1.2 | 37 |

| ADA4939-1/ADA4939-2 | 1400 | 6800 | 2.3 | N/A | 1.1 to 3.9 | 0.9 to 2.4 | N/A | N/A | 1.3 to 3.5 | 1.3 to 1.9 | N/A | ±0.8 | 37 |

| 1 N/A = 該当なし。 | |||||||||||||

入力結合および出力結合:AC またはDC

AC 結合またはDC 結合する必要がある場合には、差動ADC ドライバの選び方が大きく違ってくる可能性があります。入力結合と出力結合では検討事項が異なります。

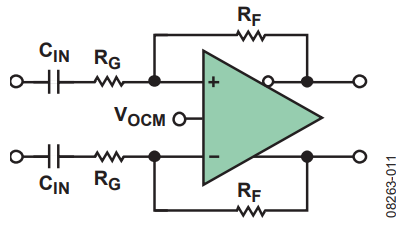

AC 結合入力段を図11 に示します。

図11. AC 結合ADC ドライバ

AC 結合入力を用いた差動to 差動アプリケーションの場合、DC帰還電流が入力コンデンサによって阻止されるので、アンプ入力端子に現れるDC 同相電圧はDC 出力同相電圧に等しくなります。また、DC の帰還係数はマッチングしており正確に1 に等しくなります。VOCM すなわちDC 入力同相電圧はほとんどの場合電源電圧の中点近くに設定されます。電源の中点を中心とする入力同相範囲のADC ドライバは、入力同相電圧がその規定された範囲の中心近くになり、これらのタイプのアプリケーションで良好に動作します。

AC結合したシングル・エンドto 差動回路はそれに相当する差動入力の回路に似ていますが、アンプ入力端子に、同相リップル、すなわち、入力信号の大きさが小さくなったレプリカ信号が観測されます。電源の中点を中心とする入力同相範囲のADC ドライバは、平均入力同相電圧が規定された範囲の中間近くとなり、ほとんどのアプリケーションでリップルに必要な十分なマージンがとれます。

入力結合が選択できる場合、AC 結合入力のADC ドライバの方がDC コモン・モード電流がどちらの帰還ループにも流れないので、DC 結合入力の類似したドライバよりも消費電力が小さくなることに注目する価値があります。

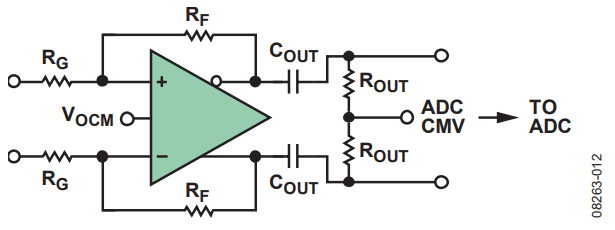

駆動ドライバの出力可能範囲を大幅に超えるような入力同相電圧をADC に印加しなければならない場合、ADC ドライバ出力をAC 結合すると効果的です。VOCM が電源中点近くに設定された時、ドライバは最大の出力振幅になります。しかしこの場合低電圧ADC を非常に低い入力同相電圧の条件下で駆動する場合に、問題が現れます。この問題の簡単な解決方法はドライバ出力とADC 入力間の接続をAC 結合して(図12 参照)、ドライバ出力からADC のDC 同相電圧を取り除き、AC 結合のADC 側にADC に合った同相レベルを供給できるようにすることです。例えば、ドライバは、VOCM = 2.5V の5V 単電源で動作が可能で、ADC は、ADC CMV ピンに必要な入力同相電圧0.9V を印加した1.8V 単電源で動作できます。

図12. DC 結合入力、AC 結合出力接続

入力同相範囲がシフトしているドライバは、一般的に単電源駆動のDC 結合システムで最適に動作します。なぜなら出力同相電圧が帰還ループを通して分圧され、その変動成分がグラウンドつまり負レールに近づく可能性があるからです。シングル・エンド入力の場合、入力同相電圧は入力に関連したリップルにより更に負のレール近くになります。

両電源動作のシステムの場合は、シングル・エンドまたは差動入力、AC 結合またはDC 結合のいずれの場合でも、ヘッドルームが増えるので一般的にはどちらのタイプの入力段でも良好に動作します。

表2 に入力結合、電源電圧の各種組み合わせに使われる最も一般的なADC ドライバ入力段タイプをまとめてあります。しかし、これらの選択は必ずしも最適ではないかもしれません。各々のシステムはケース・バイ・ケースで解析する必要があります。

| Input Coupling | Input Signal | Power Supplies | Input Type |

| Any | Any | Dual | Either |

| AC | Single-ended | Single | Centered |

| DC | Single-ended | Single | Shifted |

| AC | Differential | Single | Centered |

| DC | Differential | Single | Centered |

出力振幅

ADC のダイナミック・レンジを最大にするには、ADC をその全入力範囲に渡って駆動する必要があります。しかしADC を駆動するには注意が必要です。ADC をあまり大きく駆動すると、入力が破損する可能性があります。一方駆動電圧が小さいと分解能が悪くなります。ADC をその全入力範囲で駆動することは、アンプの出力がその全範囲で振れなければならないことを意味するわけではありません。差動出力の主な利点は各出力の振れ幅が、従来のシングル・エンド出力の振れ幅の半分だけでよいことです。ドライバ出力を各電源レールから離れた電圧に保つことができるので歪みを低減できます。しかしシングル・エンド・ドライバの場合は事情が違います。ドライバの出力電圧が電源レールに近づくと、アンプは直線性を失い歪みを招きます。

mV 単位の出力電圧が要求されるようなアプリケーションに適した表1 を参照し、標準的なヘッドルーム範囲が、負荷に応じて数mV から数百mV のレールto レール出力となっているADCドライバを探してください。

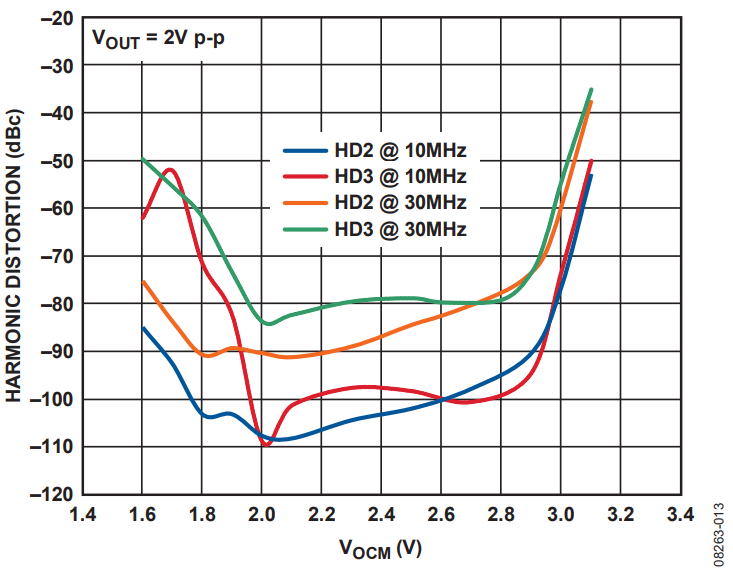

図13 はADA4932-1 の各種周波数における高調波歪みとVOCM の関係を示します。ADA4932-1 の標準的な出力振幅は各々の電源レールから1.2V 以内と規定されています。出力振幅はVOCM と信号(1V)のVPEAK との合計です。歪みは2.8V(3.8VPEAK、または5V レールの下1.2V)を超えると加速度的に大きくなります。低電圧の方を見ると、2.2V(−1VPEAK)では歪みはまだ小さいままです。同じタイプの現象が帯域とスルー・レートについての議論でも現れます。

図13. 5V 電源駆動のADA4932-1 の各種周波数における高調波歪みとVOCMの関係

ノイズ

ADC の不完全な部分として量子化ノイズ、電子(またはランダム)ノイズ、高調波歪みがあります。ノイズはほとんどのアプリケーションで重要な項目ですが、一般的に広帯域システムで最も重要な性能指標です。

すべてのADC は本質的にビット数(n)に依存する量子化ノイズがあります。量子化ノイズはビット数を増やすごとに低減します。理想的なコンバータでも量子化ノイズは存在するので、量子化ノイズはランダム・ノイズと高調波歪みを比較する際の対象となるベンチマークとして使用されます。ADC ドライバからの出力ノイズはADC のランダム・ノイズおよび高調波歪みと同等かより低いものとなっています。ADC のノイズと歪みの特性評価を見直してみることを手始めに、ADC の性能に対するADC ドライバのノイズの評価方法を示します。

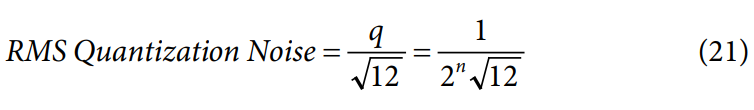

ADC は無限の分解能をもつアナログ信号を有限の数のデスクリート・レベルに量子化するので量子化ノイズが生じます。nビットADC には2n個のバイナリ・レベルがあります。1 つのレベルと次のレベルとの間の差が分解可能な最小な差を表します。これは最下位ビット(LSB)、または量子レベルqと呼ばれています。そのため1 量子レベルはコンバータの範囲の1/2n になります。もし変化する電圧が完璧なn ビットADC で変換され、それを逆に変換してアナログに戻しADC の入力信号から減算すれば、その差がノイズのように見えます。それは次のrms 値になります。

この値から、そのナイキスト帯域のn ビットADC の信号対量子化ノイズ比の対数式(dB)を導くことができます(式22 参照)。これはn ビットコンバータの得られる最良のSNR です。

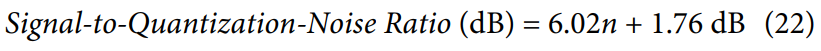

ADC の中のランダム・ノイズ(熱ノイズ、ショット・ノイズ、フリッカ・ノイズの組み合わせ)は一般的に量子化ノイズよりも大きくなります。ADC の非直線性の結果生ずる高調波歪みは(高調波的に入力信号に関係した)不要な信号を出力に生じます。全高調波歪みとノイズ(THD + N)は電子ノイズと高調波歪みをADC のフルスケール入力レンジに近いアナログ入力と比較する重要なADC の性能指標です。電子ノイズは対象とする最後の高調波周波数までの帯域全体に渡って積分されます。式23で全THD は始めの5 つの高調波歪みを含みます。これはノイズと共に2 乗和の平方根です。

v1 は入力信号、v2 からv6 までは5 つの高調波歪み積、vn はADC電子ノイズです。

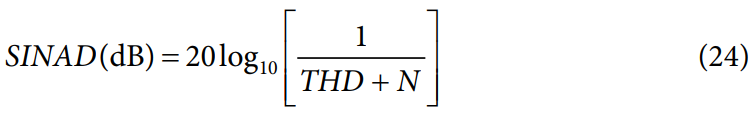

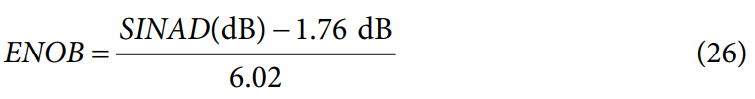

THD+ノイズの逆数の信号対ノイズ+歪み比(SINAD)は通常デシベルで表します(式24 参照)。

信号対量子化ノイズ比をSINADに置き換えれば(式22 参照)、その信号対量子化ノイズ比がそのSINAD と同じとすればコンバータがもつことができる有効ビット数(ENOB)を規定できます(式25 参照)。

ENOB はまた、式26 に示すようにSINAD に関する式で表せます。

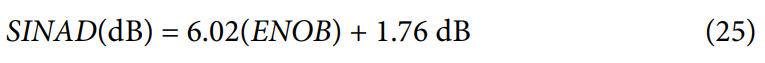

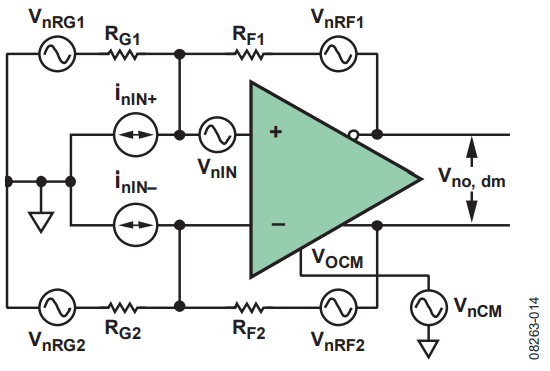

ENOB はADC ドライバのノイズ性能をADC のノイズ性能と比べて、ADC ドライバがそのADC を駆動するのに適しているかどうかを決めるために使用できます。図14に差動ADCノイズ・モデルを示します。

図14. 差動ADC ドライバのノイズ・モデル

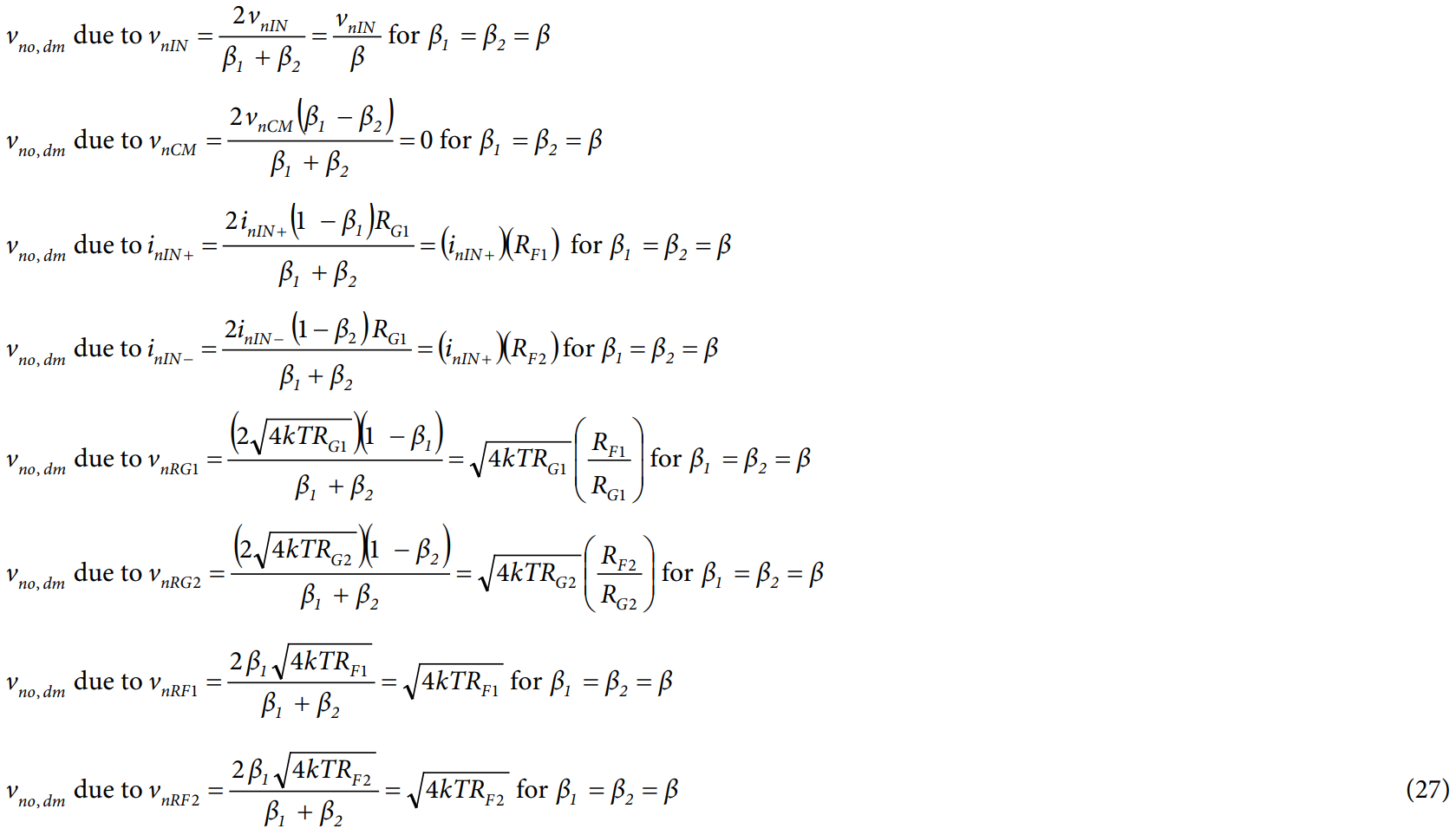

8 つのノイズ源各々の全出力ノイズ密度への寄与度を一般的な場合とβ1 = β2 ≡ β の場合について式27 に示しています。

全出力ノイズ電圧密度vno, dmはこれらの成分の二乗和の平方根を計算することにより計算されます。全出力ノイズ電圧密度を計算するには、各式をスプレッドシートに入力するのが最も良い方法です。ADI Diff Amp Calculator は、ノイズ、ゲイン、その他差動ADC ドライバの現象を速く計算することができます。

ノイズの観点から見たADC ドライバの適合性は、以下の例に示すように、ピークto ピーク出力ノイズ計算値の合計とADC のENOB の比較によって評価できます。2V のフルスケール入力を有する5V 電源でのAD9445 ADC について、ゲインが2 の差動ドライバを考えてみます。これは、単極フィルタで制限される、50MHz(−3dB)の帯域幅を占める直結型広帯域信号を処理します。各種条件のENOB 仕様をリストしてあるデータシートを参照すると、ナイキスト周波数50MHz ではENOB = 12 ビットです。

ADA4939-1 は直結可能な高性能、広帯域差動ADC ドライバです。ADA4939-1 はノイズに関してAD9445 を駆動するのに適したADC ドライバです。差動ゲインが約2 の場合、データシートではRF = 402Ω とRG = 200Ω が推奨されています。この回路構成での全出力電圧ノイズ密度は9.7nV√Hz です。

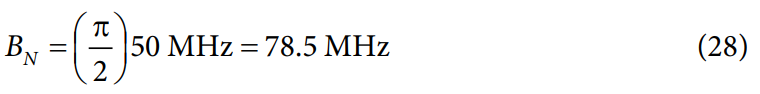

初めに、システム・ノイズ帯域幅 BNを計算します。システム・ノイズ帯域幅 BNは、与えられた一定の入力ノイズ電力スペクトル密度に対しシステム帯域幅を決める実際のフィルタと同じノイズ電力を出力する、等価長方形ローパス・フィルタの帯域幅です。1 極フィルタの場合、BNは式 28 に示すように 3dB 帯域幅の π/2 倍に等しくなります。

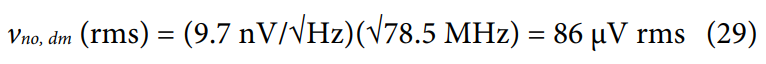

次に出力実効値ノイズを得るためにシステム帯域の平方根全体に渡ってノイズ密度を積算します。(式29 参照)

ノイズの振幅はガウス分布とします。したがって、ピークtoピーク・ノイズを得るのに一般的な±3σ リミット(ノイズ電圧は時間の約99.7%の間これらのリミット内でスイングします)を使用すると、ピークto ピーク出力ノイズは次のように計算できます。

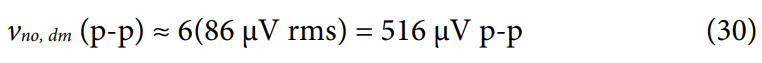

ここでADC ドライバのピークto ピーク出力ノイズを、ENOB12ビット、フルスケール入力範囲2V を基準としたAD9445 LSB の1LSB 電圧(式31 で計算しているように)とを比較します。

ドライバからのピークto ピーク出力ノイズはENOB12 ビットを基準としたADC のLSB に匹敵します。したがって、このアプリケーションではADC ドライバはノイズの観点からは検討すべき良い候補です。最終決定はドライバとADC の組み合わせ回路を組み立て、テストすることにより行わなければなりません。

電源電圧

電源電圧と電源電流を調べることはADC ドライバの選択を絞る手早い方法です。表1 は電源を基準にしたADC ドライバ性能の簡単なリファレンスです。電源電圧は帯域幅、信号振幅、ICMVR に影響します。差動アンプの選択には、それぞれの仕様を比べ、トレード・オフを検討することが重要です。

電源電圧除去(PSR)はもう1 つの重要な仕様です。アンプに対する入力として電源端子の役割はしばしば無視されます。電源ラインまたはそれらに結合されるどのようなノイズも基本的に出力信号を壊す可能性があります。

例えば、ADA4937-1 の電源ラインに60MHz で50mVp-p のノイズが乗っている場合を考えます。そのPSR は50MHZ で−70dB です。これは電源ラインのノイズがアンプ出力で約16μV に減衰することを意味します。1V フルスケール入力で16 ビット・システムの場合1LSB は15.3μV です。したがって、電源ラインからのノイズはLSB を妨害します。

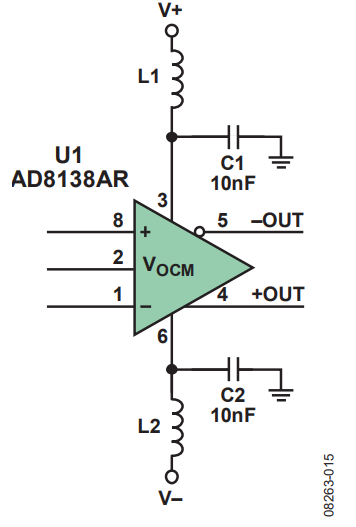

この状況を改善するためには、直列にSMT フェライト・ビーズL1 とL2 と、シャント・バイパス・コンデンサC1 とC2、(図15 参照)を接続してください。

図15. 電源のバイパス

50MHz でフェライト・ビーズのインピーダンスは60Ω で、10nF(0.01μF)コンデンサのインピーダンスは0.32Ω です。この2 つの素子によって構成される減衰回路により45.5dB の減衰度が得られます。(式32 参照)

デバイダ減衰度と−70dB のPSR との組み合わせで約115dB の除去が得られます。これによりノイズは1LSB より十分小さな約90nVp-p に減少します。

高調波歪み

周波数領域での低高調波歪みは狭帯域と広帯域システムの両方で重要です。ドライバの非直線性はアンプ出力でシングル・トーンの高調波歪みと複数トーンの相互変調歪み積を生じます。

ノイズ解析例に使用された同じアプローチが歪み解析に適用できます。ADA4939-1 の高調波歪みをフルスケール出力2V でENOB12 ビットのAD9445 の1LSB と比較します。ENOB の1LSBはノイズ解析では488μV になります。

ADA4939-1 の仕様表の歪みデータはゲイン2 とした時の値で、各種周波数での2 次高調波と3 次高調波を比較しています。表3はゲイン2、差動出力スイング2Vp-p の条件での高調波歪みを示します。

| Parameter | Harmonic Distortion (dBc) |

| HD2 at 10 MHz | −102 |

| HD2 at 70 MHz | −83 |

| HD2 at 100 MHz | −77 |

| HD3 at 10 MHz | −101 |

| HD3 at 70 MHz | −97 |

| HD3 at 100 MHz | −91 |

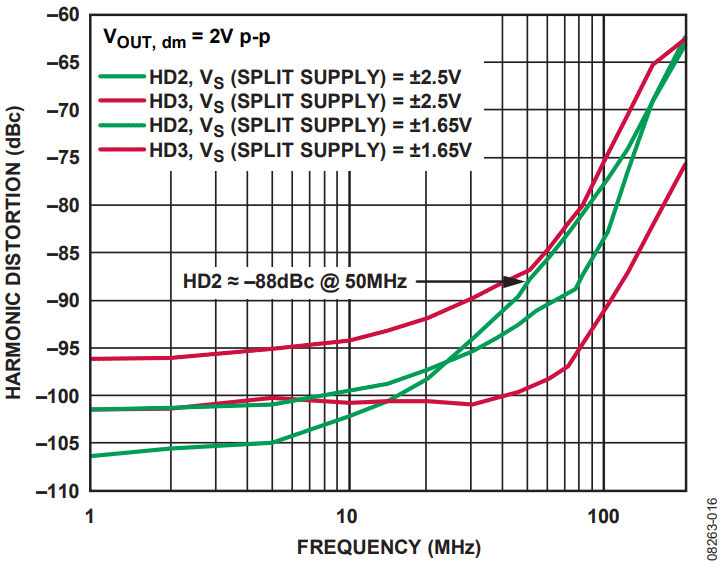

データは周波数が高くなると共に高調波歪みが増えることと、対象の周波数(50MHz)ではHD2 がHD3 より悪いことを示しています。高調波歪み積は対象の周波数よりも周波数が高いのでそれらの振幅はシステム帯域制限により低減できます。もしシステムに50MHz でブリック・ウォール・フィルタがあれば25MHz 以上の周波数のみが対象になります。なぜならばより高い周波数の全高調波はフィルタで減衰されるからです。それでもシステムを50MHz まで評価しました。なぜなら存在するどのフィルタも高調波を十分に減衰することは難しく、歪み積が信号帯域内に折り返される可能性があるからです。図16 は2Vp-p出力として各種電源電圧についてADA4939-1 の高調波歪みと周波数の関係を示しています。

図16. 高調波歪みの周波数特性

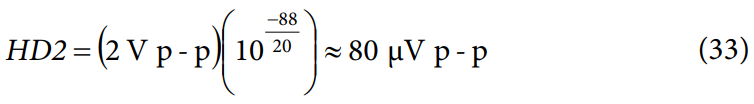

50MHz でのHD2 は入力信号2Vp-p に対して約−88dBc です。高調波歪みのレベルを1ENOBLSB と比較するために、式33 に示したようにこのレベルを電圧に変換する必要があります。

この歪み積はわずか80μVp-p、または1ENOB LSB の16%です。このように歪みの点からADA4939-1 はAD9445 ADC を駆動するドライバとして検討すべき良い選択肢になります。

ADC ドライバは負帰還型アンプなので、出力歪みはアンプ回路のループ・ゲインの大きさに依存します。負帰還アンプのもともとのオープンループ歪みはファクタ1/(1 + LG)分縮小します。ここでLG はアンプのループ・ゲインです。

アンプの入力(誤差電圧)は大きな順電圧ゲインA(s)と乗算され、帰還率β を通して入力にフィードバックされますが、ここで誤差が最小限になるように出力電圧が調整されます。そのため、このタイプのアンプのループ・ゲインはA(s) × β です。ループ・ゲイン(A(s)、β、または両方)が減少すると、高調波歪みが増します。積分器のような電圧帰還アンプはDC と低周波数で大きなA(s)を持ち、規定された高周波でゲインが1 になるまで1/f でロール・オフするように設計されています。A(s)はロール・オフすると、ループ・ゲインが減少し、歪みが増大します。そのため、高調波歪み特性はA(s)の逆になります。

電流帰還型オペアンプは誤差電流を帰還信号として使います。誤差電流は大きなトランスインピーダンスT(s)に乗算され、出力電圧に変換されます。それから帰還率1/RF を経由して出力電圧を帰還電流に変換します。その帰還電流は入力誤差電流を最小限にするように働きます。そのため、理想電流帰還アンプのループ・ゲインはT(s) × (1/RF) = T(s)/RFになります。A(s)と同じようにT(s)は大きなDC 値を持っており、周波数が高くなるとロール・オフし、ループ・ゲインが低減してきて高調波歪みが増大します。

ループ・ゲインはまた、帰還率1/RF に直接依存します。理想的な電流帰還アンプのループ・ゲインは閉ループ・ゲインに依存しません。そのため、高調波歪み特性は閉ループ・ゲインが増しても低下しません。しかし実際の電流帰還型アンプではループ・ゲインは閉ループ・ゲインの大きさに多少影響されます。しかしその影響度は電圧帰還型アンプよりはるかに少なくなっております。この依存性により、ADA4927-1 のような電流帰還型アンプは、高い閉ループ・ゲインと低い歪みを必要とするアプリケーション向けには、電圧帰還型アンプよりも良い選択肢になります。

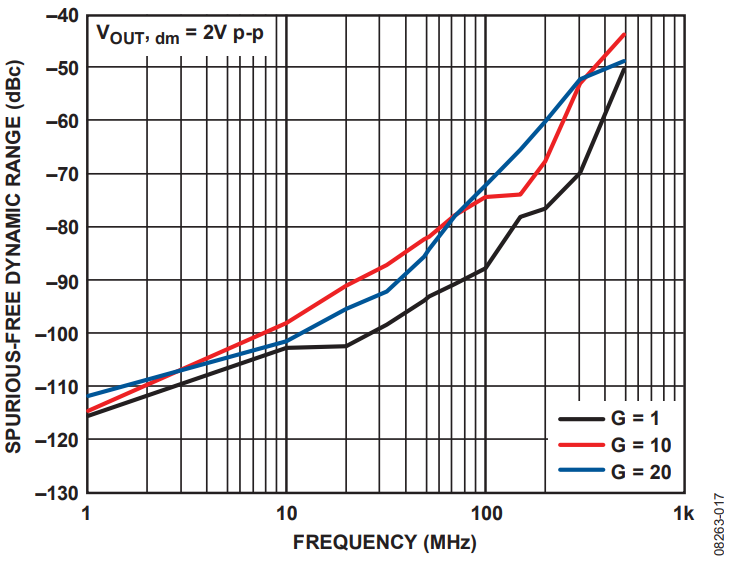

図17 はADA4927-1 について閉ループ・ゲインが大きくなるに伴い、歪み特性がどのように良好に維持されているかを示しています。

図17. 高調波歪みと周波数およびゲインの関係

帯域幅とスルー・レート

帯域幅とスルー・レートはADC ドライバ・アプリケーションで特に重要です。一般的にデバイスの帯域幅は小信号帯域幅です。一方スルー・レートはアンプ出力での大信号振幅の最大変化率です。

ENOB に似ている用語で有効使用可能帯域幅(EUBW)がありますが、これは帯域幅のことを述べています。多数のADC ドライバとオペアンプは帯域幅の仕様を誇示していますが、実際に使用可能な帯域幅は限られています。例えば−3dB 帯域幅は帯域幅を評価する一般的な方法ですが、すべての帯域幅が使用可能という意味ではありません。−3dB 帯域幅の振幅誤差と位相誤差は実際のカットオフ周波数よりも1 桁早く観測されます。使用可能な帯域幅を決定する良い方法はデータシートの歪みに関するグラフを参照することです。

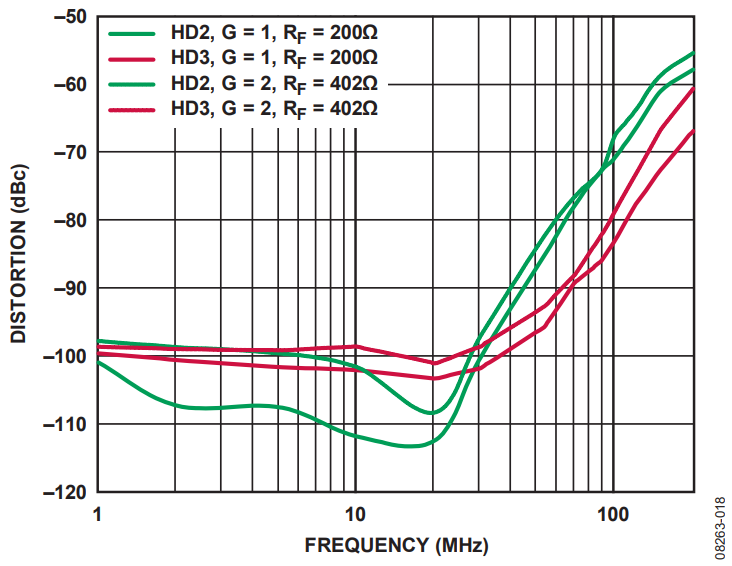

図18 は2 次、3 次高調波歪みを−80dBc 以上に保つには、ADC ドライバを60MHz.以上の周波数で使用するべきではないことを示しています。アプリケーションは様々なので、システム条件がそのアプリケーションに対して十分な帯域幅と十分な歪み特性を持った適切なドライバを選択するためのガイドとなります。

図18. 電流帰還ADC ドライバADA4937-1 の歪み曲線

スルー・レート(大信号パラメータ)はアンプ出力が大きな歪みを伴わないで入力に追従することのできる最大の変化率です。サイン波出力のスルー・レートについて考えてみましょう。

式34 のゼロ交差での導関数(変化率)、すなわち最大変化率は次のとおりです。

ここで、

dv/dt max はスルー・レート。

VP はピーク電圧。

f はフルパワー帯域幅(FPBW)です。FPBW について解くと下記の式になります。

そのため、ADC ドライバを選ぶときには、アンプが対象アプリケーションで十分使用可能か判断するために、ゲイン、帯域幅、スルー・レート(FPBW)を確認することが重要です。

安定性

差動ADC ドライバの安定性に関する評価はオペアンプと同じです。主な仕様は位相余裕です。特定のアンプ回路の位相余裕はデータシートから決定されます。しかしそれは実際のシステムではPC 基板レイアウトの寄生的な影響により大きく低減します。

負電圧帰還オペアンプの安定性はループ・ゲインA(s) × β の大きさと符号に依存します。差動ADC ドライバには2 つの帰還係数があるので標準的なオペアンプ回路よりも多少複雑です。ループ・ゲインは式7 と式8 の分母の中にあります。式37 は帰還係数がマッチングしてない(β1 ≠ β2)場合のループ・ゲインです。

帰還係数がマッチングしてない場合、有効な帰還係数は単に2つの帰還係数の平均です。それらがマッチングしていてβ と規定した時、ループ・ゲインはA(s) × β に簡略化できます。

帰還アンプを安定させるには、ループ・ゲインが−1 またはそれと等価、すなわち、−180°の位相シフトでループ・ゲインが+1になることを避けなければなりません。電圧帰還アンプの場合、オープン・ループ・ゲイン周波数曲線でループ・ゲインの大きさが1(すなわち、0dB)に等しい点でA(s)の大きさが帰還係数の逆数に等しくなります。基本的なアンプのアプリケーションでは帰還は純粋に抵抗性なので帰還ループ周辺で位相シフトは生じません。帰還係数がマッチングしている場合、周波数依存性のない帰還係数の逆数、1 + RF/RG はノイズ・ゲインと呼ばれることがあります。デシベル表示の一定のノイズ・ゲインをオープン・ループ・ゲインA(s)と同じグラフに描いた場合、2 つの曲線が交差する周波数がループ・ゲイン1、または0dB になる周波数です。その周波数でのA(s)の位相と−180°との間の差が位相余裕と定義されます。安定動作のためには、位相余裕は45°以上でなければなりません。

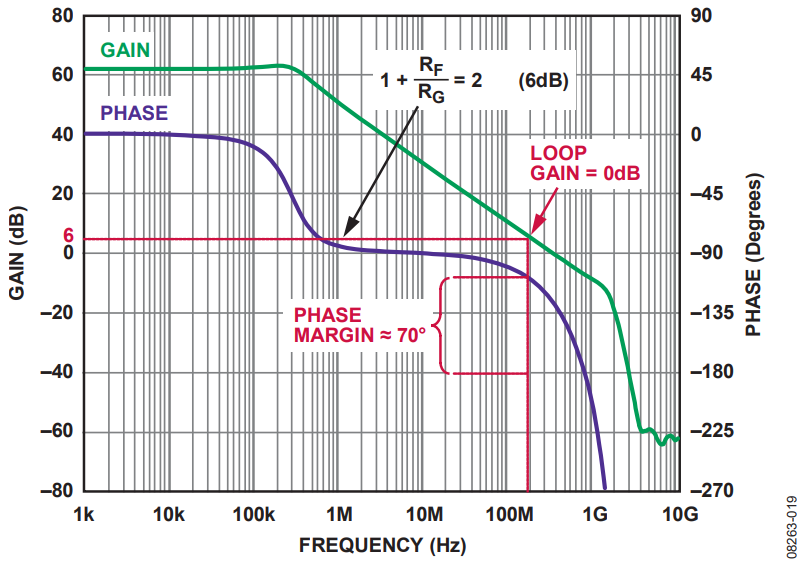

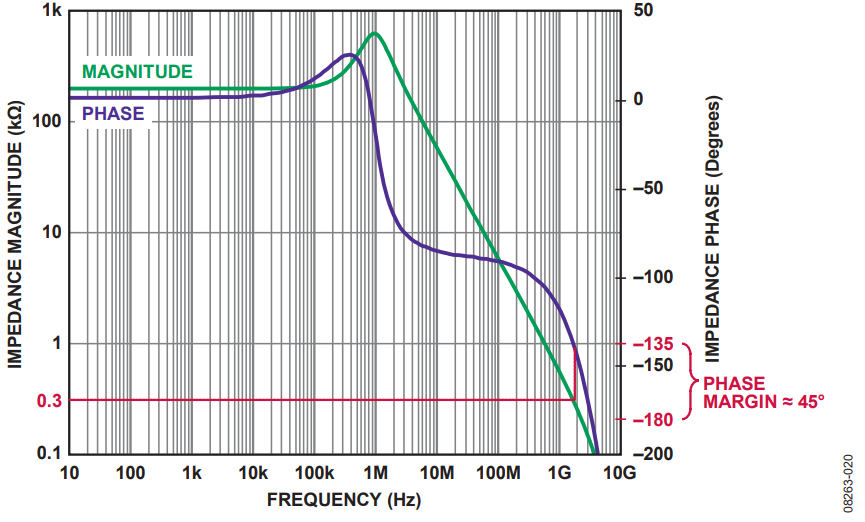

図19 はRF/RG = 1(ノイズ・ゲイン = 2)に設定したADA4932-2のユニティ・ループ・ゲイン点と位相余裕について説明しています。

図19. ADA4932-2 のオープン・ループ・ゲインの大きさおよび位相と周波数の関係

図19 を更に詳しく調べるとADA4932-2 はノイズ・ゲイン1(各ループで100%帰還)で約50°の位相余裕があります。ADC ドライバをゼロ・ゲインで動作させることは現実的ではありませんが、このことはADA4932-2 が整数でない差動ゲイン(例えばRF/RG = 0.25、ノイズ・ゲイン=1.25)で安定動作することを示しています。この現象は、全ての差動ADC ドライバに当てはまるわけではありません。安定動作する最小ゲインはすべてのADCドライバのデータシートに記述されています。

電流帰還形ADC ドライバの位相余裕もまた、オープンループ応答特性から決定されます。電流帰還型アンプの場合はフォワード・ゲインの代わりにフォワード・トランスインピーダンスT(s)を使用し、誤差電流がフィードバック信号となります。フィードバック抵抗がマッチングしている電流帰還型ドライバのループ・ゲインはT(s)/RF です。したがって、電流帰還型アンプのループ・ゲインはT(s) = RFの時1(すなわち、0dB)に等しくなります。この点はオープンループ・トランスインピーダンスと位相のグラフで、電圧帰還型アンプの場合と同じ方法で簡単に探し出すことができます。抵抗の1kΩ に対する比率をプロットすることにより抵抗を対数グラフで表せます。図20 はRF = 300 とした場合の電流帰還型差動ADC ドライバADA4927-1 のユニティ・ループ・ゲイン点と位相余裕について説明しています。

図20. ADA4927-1 のオープン・ループ・ゲインの大きさおよび位相と周波数の関係

300Ω フィードバック抵抗の水平線がトランスインピーダンス曲線と交差する所でループ・ゲインが0dB になります。この周波数ではT(s)の位相が約−135°となりますので、位相余裕が+45°になります。位相余裕と安定性は、RF が大きくなると増し、RF が小さくなると低減します。電流帰還型アンプにはいつも純粋な抵抗性フィードバックを用い、十分な位相余裕をもつ必要があります。

PCB レイアウト

安定したADC ドライバの設計はPC 基板で実現されなければなりません。基板の寄生要素により位相余裕がある程度失われてしまうため、これを最小限に保たなくてはなりません。特に懸念されるのが負荷容量、帰還ループ・インダクタンス、加算ノード容量です。これら各々の寄生リアクタンスにより遅延する位相シフトが帰還ループに加わり、位相余裕が低減します。PC 基板レイアウトの設計が悪いと位相余裕が20°またはそれ以上失われます。

電圧帰還型アンプの場合、RF とサミング・ノード容量で形成される極による位相シフトを最小限にするために、できるだけ小さなRFを使うのがベストです。もし大きなRFが必要な場合、小さな容量CF を各帰還抵抗間に接続することによりそのサミング・ノード容量を補償することができます。この場合CFはRF ×CFがサミング・ノード容量のRG倍に等しくなるような値に設定します。

PC 基板レイアウトは必然的に設計の最後のステップの1 つです。高速回路の性能はレイアウトに大きく依存しますが、あいにくPC 基板レイアウトは、設計で最も見落としがちなステップの1つでもあります。不注意な、または貧弱なレイアウトによって高性能設計の性能低下を余儀なくさせられたり、場合によっては使用を諦めさせられたりすることになります。ここでは適切な高速PC 基板設計のすべての面をカバーできませんが、いくつかの主なトピックスについて述べます。

寄生成分は高速回路の性能を低下させます。寄生容量は部品のパッド、パターン、グランド・プレーンまたは電源プレーンによって生じます。グランド・プレーンのない長いパターンは寄生インダクタンスが生じ、過度応答にリンギングを生じたり、他の不安定な現象をもたらしたりします。特にアンプのサミング・ノードで生ずる寄生容量は大きな影響があります。なぜならそれはフィードバック応答に極をつくり、ピーキングや不安定性の原因になるからです。1 つの解決方法は基板全部の層において、ADC ドライバの実装部分の下とフィードバック部品のパッドの下の領域にはグランド・プレーンや電源プレーンを設けないようにすることです。

不要な寄生リアクタンスを最小限にするためにすべてのパターンをできるだけ短く保ってください。FR-4 のPCB の外側層の50Ω パターンはおおよそ2.8pF/インチと7nH/インチあります。内側層の50Ω パターンの場合これらの寄生リアクタンスは約30%増えます。更にパターン・インダクタンスを最小限にするために、長いパターンの下には確実にグランド・プレーンがあるようにしてください。パターンを短く、小さく保つことは寄生容量と寄生インダクタンスを最小限にし、設計の完全性を維持するのに役立ちます。

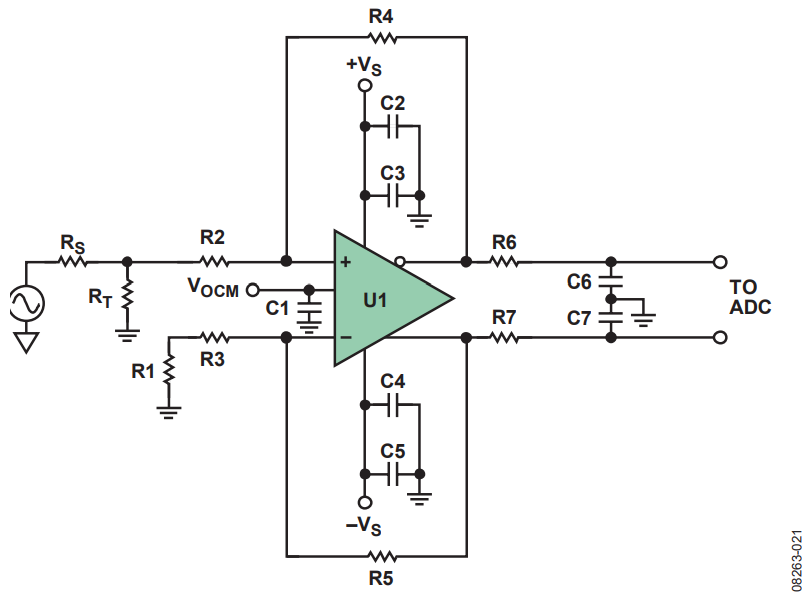

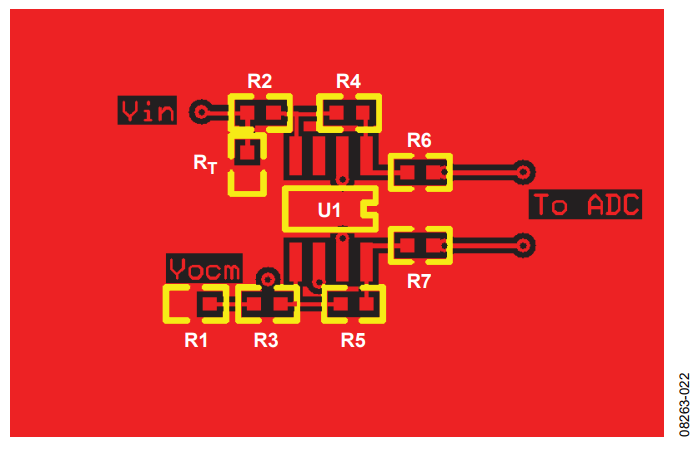

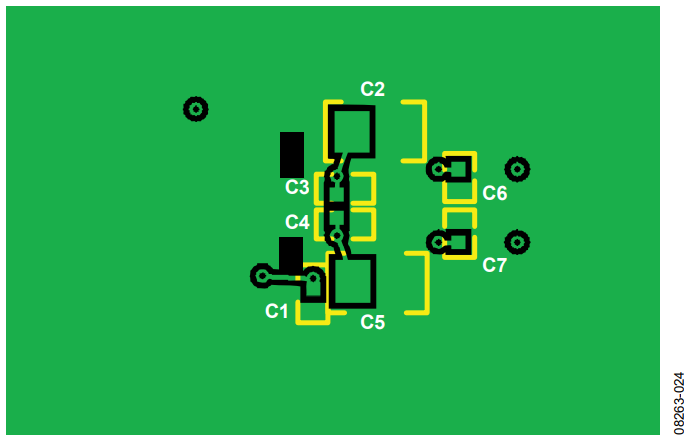

電源バイパスはレイアウトを行うに際し問題となるもう1 つの主な分野です。VOCM バイパス・コンデンサと同様に、電源バイパス・コンデンサをアンプのピンのできるだけ近くに配置することを確実に行ってください。更に複数のバイパス・コンデンサを電源ラインに使うことは、広帯域ノイズに対して低インピーダンス・パスにすることを確実なものにする助けになります。図21 は電源バイパスと出力にローパス・フィルタを接続した標準的な差動アンプ回路です。ローパス・フィルタは帯域幅とADC に入るノイズを制限します。理想的には電源バイパス・コンデンサのリターンは負荷リターンの近くに配置します。これは、グランド・プレーンの中の還流電流を減らしADC ドライバ性能を改善する助けになります(図22、図23 参照)。

図21. 電源バイパスと出力ローパス・フィルタを接続したADC ドライバ

グランド・プレーンの使用や一般的な接地方法は複雑で内容が深いテーマなのでこのアプリケーション・ノートの範囲外です。しかし、いくつかの主なポイントを次に述べます(図22、図23 参照)。

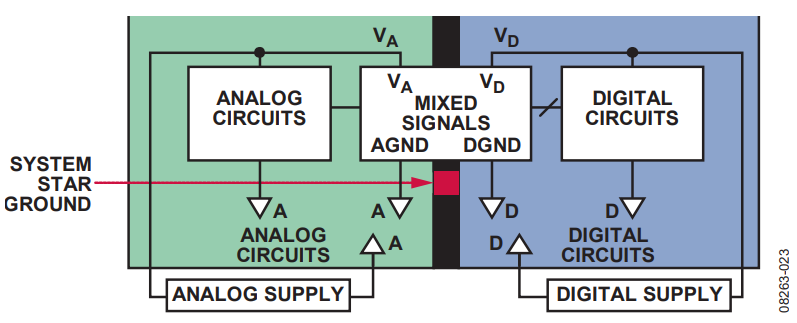

- アナログ・グラウンドとデジタル・グラウンドを共に1 点で接続してください。そのようにすることで、グランド・プレーンを流れるアナログ電流とデジタル電流の相互作用(これがシステムにノイズを招きます)を最小限にできます。

- アナログ電源をアナログ電源プレーンに終端し、デジタル電源をデジタル電源プレーンに終端してください。

- ミックスド・シグナルIC の場合、デジタル電流とアナログ電流が混じり合わないように、アナログ・グラウンド・リターンをアナログ・グランド・プレーンに終端し、また、デジタル・グラウンド・リターンをデジタル・グランド・プレーンに終端し、2 つのプレーンを共に1 つの小さな接続だけで接続してください(図24 参照)。

図22. 部品側

図23. 回路側

図24. ミックスド・シグナルの接地

高速PCB レイアウトについての詳細な説明は、高速プリント回路基板レイアウトの実務ガイドを参照してください。

このアプリケーション・ノートの情報はADC ドライバを使って回路設計をする場合に考慮しなければならない、多数の課題について考えるお手伝いをするのが目的です。プロジェクトの初めに差動アンプについて理解し、ADC ドライバの設計の詳細に注意を払うことは将来の問題を最小限に抑え、リスクを減らし、堅牢な設計を確かなものとします。