質問:

DC/DCデバイスに2つの出力があって、それを2相単一出力として使用した場合、ソフト・スタート時間にはどのような影響があるでしょうか?

回答:

デバイスに2本のソフト・スタート・ピンがある場合、それぞれのピンには専用の電流ソースがあり、単一出力構成として実装するにはそれを並列に接続します。この場合、電流ソースの値は2倍になるので、同じ出力キャパシタを使用した場合、時間はオリジナル構成だったときの半分になります。したがって、同じソフト・スタート時間にするには、ソフト・スタート・キャパシタの値も2倍にする必要があります。

概要

多くのパワー・マネージメントIC(PMIC)は、ソフト・スタートと呼ばれる機能を内蔵しています。ソフト・スタート機能は主にスイッチング電源に使われますが、リニア電源(LDO)にも使われる例があります。ソフト・スタートの目的は、出力電圧を制御された形で徐々にランプ・アップさせることによって、スタートアップ時の突入電流を制限することにあります。これは、最初に電源を入れたときに生じる、電流や電圧の突然のサージを防ぐ助けになります。ほとんどのスイッチング電源にはソフト・スタート機能が組み込まれていて、これは外部で調整したり内部で固定したりすることができます。しかし、ICがソフト・スタート機能をサポートしていたとしても、データシートにソフト・スタートの式が記載されていない場合があります。本稿では、様々なソフト・スタート・メカニズムについて説明し、データシートにソフト・スタートの式が記載されていない場合のソフト・スタート時間の評価と測定に関する推奨事項を示します。また、ICにソフト・スタート機能が含まれていないにも関わらず設計に必要な場合の対処方法についても解説します。

ソフト・スタートとプリバイアス・ソフト・スタート

絶縁されていないDC/DC ICの入力に初めて電源を供給するときは、通常、出力キャパシタは充電されておらず、電圧レベルは0Vのままです。回路の視点から見ると、入力から出力への経路はインピーダンスが小さく、スイッチング・レギュレータICが出力キャパシタを急速に充電しようとすると、その帰還ループが飽和してしまいます。そのため、ICが制限値になるまで電流を供給し、スイッチ電流がピークに達する可能性があります。ソフト・スタート機能がないと、このスタートアップ・サージ電流がパワー・スイッチの故障やインダクタの飽和を引き起こしたり、電流制限フォルトによりICが起動しなくなったりするおそれがあります。スイッチングDC/DC製品によってはプリバイアス・ソフト・スタート機能を備えていることがありますが、この機能は、DC/DC電源のパワーアップ前に、既に負荷に電圧が存在する(したがって出力キャパシタにも存在する)場合に動作します。プリバイアス状態は複数電源の設計や冗長電源の設計で発生することがあります。これらの設計では、FPGA/ASICのようなロジックICの電界効果トランジスタ(FET)やクランプ・ダイオードを介した経路で電圧が伝わります。この電圧がソフト・スタート電圧を超えた場合、ICにプリバイアス防止回路がないと、ICは出力電圧が高すぎると見なしてローサイドFETをアクティブにし、出力電圧を放電します。更にこれによって、インダクタのシンク電流が大きくなることがあります。近年のほとんどのICには、ソフト・スタート・ピンと帰還ピンの電圧が等しくなるまでICによるFETのスイッチングを防ぐプリバイアス回路が組み込まれており、これらの電圧が等しくなった時点でソフト・スタート・プロセスが開始されます。

スタートアップ時に出力キャパシタに流れ込む電流は次式で表されます。

この式は、容量またはスタートアップ時に加えられる電圧が大きいほど、あるいは時間が短いほど、スタートップ電流が大きくなることを示しています。ソフト・スタートは高インピーダンスの経路を使用して、制御された形で出力キャパシタを充電できるようにします。ソフト・スタートを行う一般的な方法には、リファレンス電圧を徐々に増加させる方法や、パワー・スイッチ電流の上昇率を制御する方法などがあります。

ソフト・スタートの実行

ソフト・スタートの実行方法には電圧ソフト・スタートと電流ソフト・スタートの2つがあります。電圧ソフト・スタートは降圧レギュレータによく見られる方法で、その一例であるLT8640は、42VのVIN(最大値)で5Aの負荷電流を供給できる第1世代のSilent Switcher®降圧コンバータです。図1は電圧ソフト・スタートを行うセクションのブロック図です。

図1. 降圧レギュレータで一般的な電圧ソフト・スタートの例、LT8640のブロック図

ソフト・スタート時間tSSの間はソフト・スタート・ピンに接続された電流ソースがソフト・スタート・キャパシタを充電し、ソフト・スタート・ピンの電圧はゼロからリファレンス(REF)電圧まで徐々に増加します。電圧ソフト・スタート方式では、帰還(FB)電圧がREF電圧に達するまで、外部電圧レギュレーション・ループがソフト・スタート・ピンの電圧をリファレンスとして使用して出力電圧(VOUT)を安定化します。これらの電圧が等しくなった時点で、内部REF電圧を使ってVOUTを安定化するようにループが切り替わります。この外部ループ用リファレンス電圧の漸増は、VOUTがゼロからランプ・アップしてその目標電圧になるまでの間、FB電圧を強制的にソフト・スタート電圧VSSを等しくなるようにすることによって実現されます。ソフト・スタート・キャパシタCSSを充電する電流ソースISSは一定の値なので、ソフト・スタートの式は次のように表せます。

また、ソフト・スタート・キャパシタCSSの目標充電電圧はリファレンス電圧なので、この式は次のように書き直すことができます。

LT8640の場合、ISS = 1.9μA、VREF = 0.97Vです。

図2に、LT8362の電流ソフト・スタートを受け持つセクションのブロック図を示します。このデバイスは60V/2AのパワーFETを内蔵する昇圧レギュレータで、SEPIC設計や反転設計にも使用できます。ブロック図では、外部電圧レギュレーション・ループのエラー・アンプのREFが、固定リファレンスに直接接続されています。ソフト・スタートの実行中は、ソフト・スタート・ピンの電圧をピーク電流制限用のリファレンスとして使い、ピーク電流制限コンパレータの入力が徐々に増加します。この増加プロセスは、完全なピーク電流制限値に達するまで続きます。ソフト・スタート機能は、Q1を介してVCの上昇率を制御することによって、パワー・スイッチ電流の勾配を制御します。基本的には、これが使用可能な電流をサイクルごとにランプ・アップさせて出力を充電します。電圧ソフト・スタートではREF(およびその後はVFBとVOUT)のランプ・アップ・レートをソフト・スタート・キャパシタ(CSS)が制御しますが、電流ソフト・スタートでは、ソフト・スタートの実行中、CSSが所定の時間でピーク電流をランプ・アップさせます。結果として、CSSキャパシタと電流ソース間の関係は単純な線形関係ではなくなります。出力電圧がゼロからそのレギュレーション設定ポイントまでランプ・アップするのに必要な時間は、VOUT、COUT、および負荷電流を含む様々な要素に依存します。

図2. 電流ソフト・スタート、LT8362のブロック図

ソフト・スタート時間tSSを予測する方法

電圧ソフト・スタートを使用するシステムでは、多くの場合、ソフト・スタート時間(tSS)の式は線形で、しかもデータシートに記載されているので、予測は比較的容易です。これは、ある値のソフト・スタート・キャパシタ(CSS)によって特定のソフト・スタート時間が得られるとすると、CSSの値を倍にするとソフト・スタート時間も倍になることを意味します。例えば、CSS = 1nFの場合のソフト・スタート時間が1msだとすると、CSS = 2nFではtSS = 2msになります。これは、LT8640デモ・ボードのソフト・スタート・キャパシタC8を0.1μFから1μFに変更することによって確認できます。このようにキャパシタ値を変更すると、それに応じてソフト・スタート時間も変化して長くなります。

C8を変更し、それぞれについて負荷電流を変更します。ここでは、0Aと4Aの負荷電流でソフト・スタートを確認します。1μFは0.1μFの10倍なので、ソフト・スタート時間も10倍になると予想されます。

図3. LT8640デモ・ボードの回路図。C8がソフト・スタート・キャパシタ。

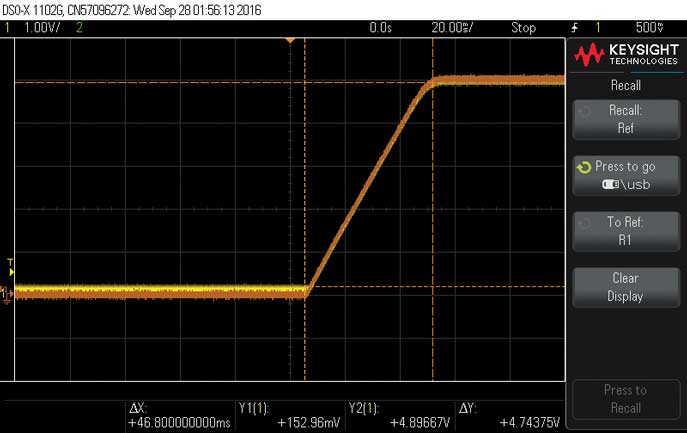

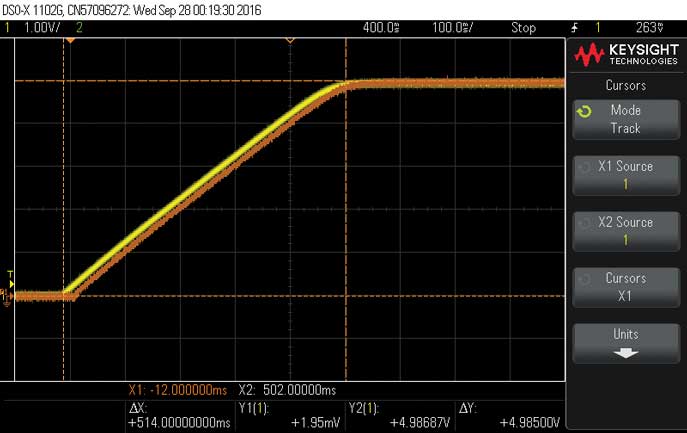

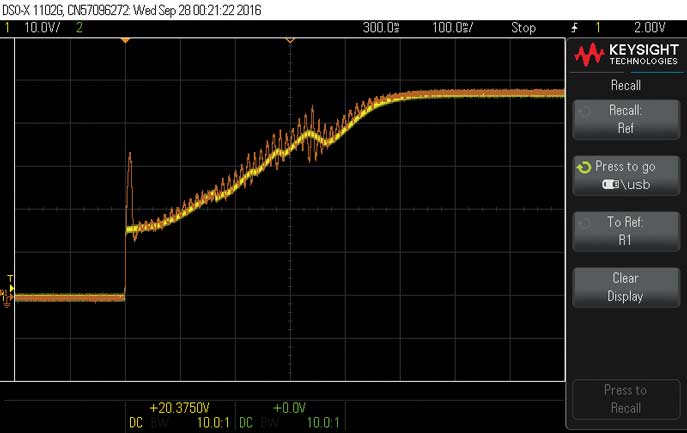

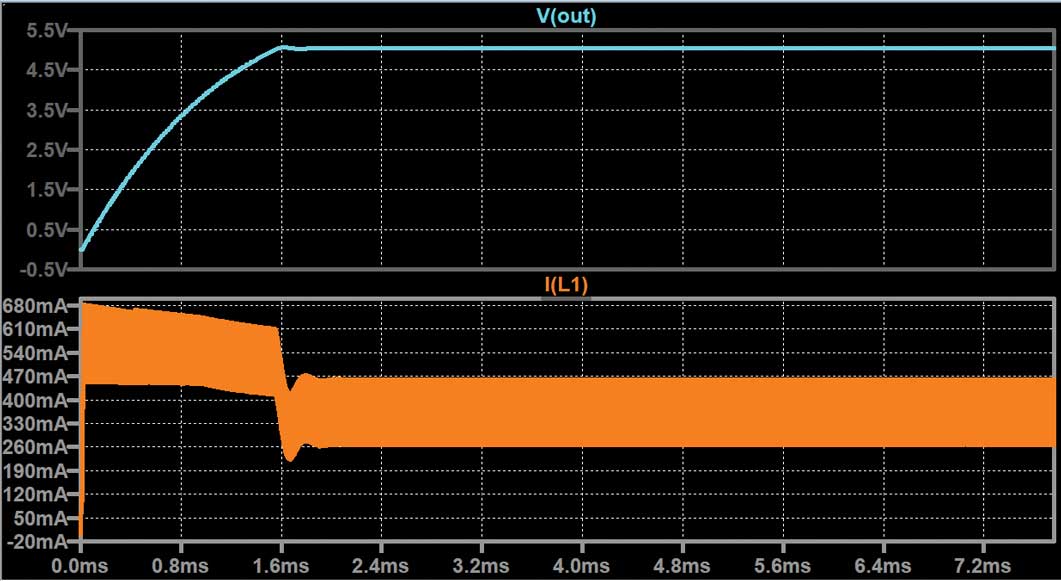

図4(C8 = 0.1μF)と図5(C8 = 1μF)において、黄色のトレースは負荷電流0Aの場合を表し、茶色のトレースは負荷電流4Aの場合を示します。どちらの負荷電流でもスタートアップ時間は同じなので、ソフト・スタート時間も同じです。予想通り、1μFではスタートアップ時間が10倍になり、その結果として時間が約50ms(0.1μF)から約500ms(1μF)に変化しました。負荷電流の違いはスタートアップ時間には影響しませんでした。

図4. LT8640:C8 = 0.1μF、負荷電流0A(黄)と4A(茶)でのスタートアップ時間は約50ms

図5. LT8640:C8 = 1μF、スタートアップ時間は約500ms、負荷電流はスタートアップ時間に影響しません。

LT8362のデータシートにはソフト・スタートの式は記載されていません。デモ・ボード(図6)を使用して、ソフト・スタート・キャパシタC6の値を変更することにより、ソフト・スタート時間をテストすることができます。テストは0A(無負荷)、0.19A、および0.38Aの3つの異なる負荷電流値を使って行います。

図6. LT8362デモ・モードの回路図。ソフト・スタート・キャパシタC6と負荷電流が変更されます。

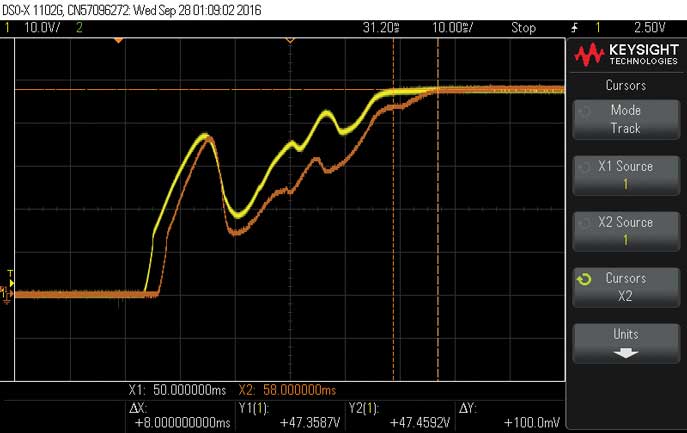

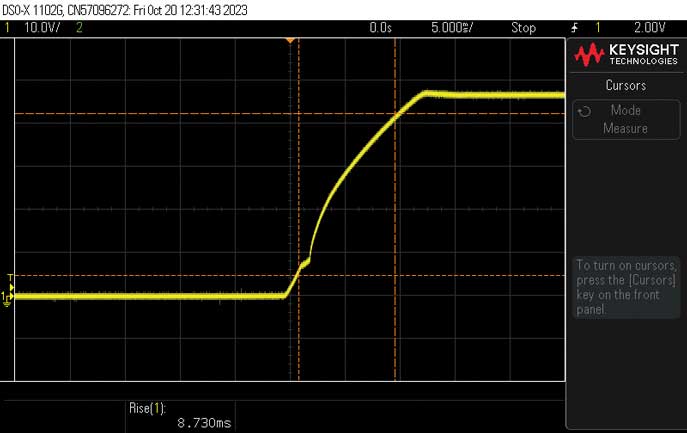

図7では、C6 = 0.22μF、負荷電流は0.19A(黄)と0.38A(茶)です。負荷を大きくするとソフト・スタート時間も長くなります。スタートアップ時間の差は約10msで、45msから約55msに変化しています。初期動作の波形に注意してください。これは、出力が急激に変化しても一定の抵抗値を保とうとするデジタル負荷を使ってテストしたことによる結果です。デジタル負荷はCR(Constant Resistance = 一定抵抗)に設定されています。負荷を純粋な抵抗負荷に変更すると、図8に示すように、より安定したモノトニックなスタートアップ動作となります。時間に関する結果はデジタル負荷でも抵抗負荷でもほとんど同じなので、スタートアップの違いに関するテストには引き続きデジタル負荷を使用することができます。

図7. C6 = 0.22μF:負荷電流を0.19Aから0.38Aに変更するとソフト・スタート時間も変化

図8. CSS = 0.22μF、CRでデジタル負荷を使用した場合(茶)と抵抗負荷を使用した場合(黄)、0.19A

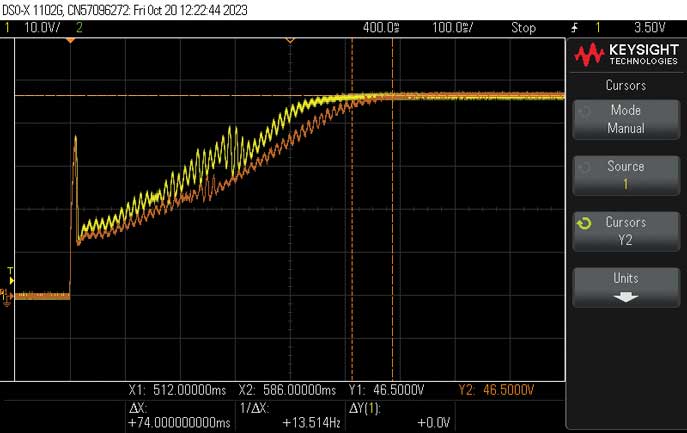

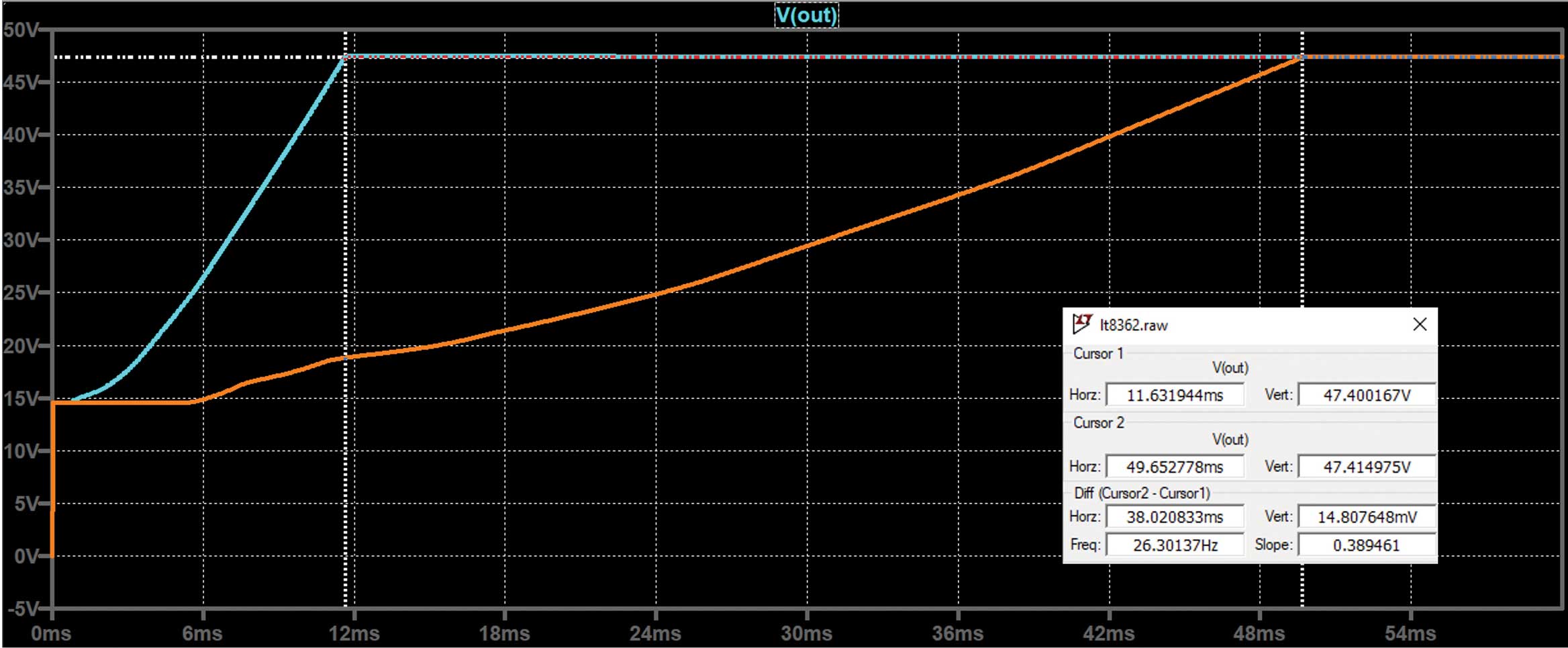

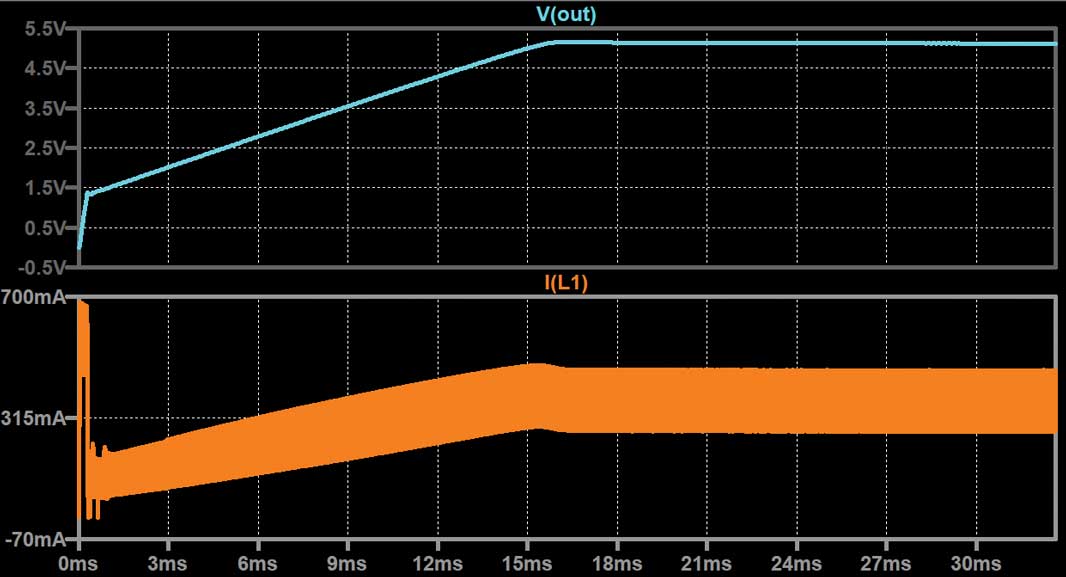

図9ではC6を2.2μFに変更しており、スタートアップ時間は、図8と比較すると0.19Aで約45msから約500msに変化しており(黄)、0.38Aでは約55msから約580msに変化しています(オレンジ)。この結果は、ソフト・スタート・キャパシタの比と同様に、10倍に近い値となっています。しかし、この場合は、電圧ソフト・スタートを使用するLT8640の場合と異なり、負荷電流がソフト・スタート時間に影響しています。また、この結果は、図7のような起伏の多い状態は緩和されたことを示していますが、スタートアップ波形にはある程度のリップルが生じています。図10はデジタル負荷の波形(茶)と純粋な抵抗負荷による結果(黄)を比較したもので、突然の変化によってデジタル負荷が正しくない値までジャンプしていますが、その後に補正されて平均値になっていることが分かります。デジタル負荷のスタートアップ時間と平均値は、最終的には純粋な抵抗負荷の時間および平均値と同じになっています。これらの観測結果から分かるのは、このシナリオでは負荷電流がソフト・スタート時間に影響しますが、デジタル負荷でも補正によって純粋な抵抗負荷の場合と同様の結果が得られるということです。

図9. C6 = 2.2μF:負荷電流を0.19Aから0.38Aに変更すると、スタートアップ時間も変化します。

図10. C = 2.2μF:スタートアップ時間が長ければ、それだけデジタル負荷による正しいCRの設定が容易になります。

RFアンプへの電源供給時には、場合により先に電源を立ち上げることが優先されて、その後に負荷が接続されます。このアプローチでは、負荷電流が非常に小さい状態またはゼロの状態で電源を立上げることができ、これは突入電流を減らす助けとなります。このシナリオを図11に示します。結果としてスタートアップ時間は約12msに短縮されています。負荷を0.19Aや0.38Aといった特定の値に固定するCC(Constant Current = 一定電流)モードでデジタル負荷を使う場合でも、約12msのスタートアップ時間を得ることができます。これは、負荷を接続しない場合とほぼ同じです。CCはDC/DCコンバータからすると高インピーダンスであることを意味することにもなるので、考え得るすべてのシナリオでソフト・スタート時間を正確に測定するように注意する必要があります。

図11. C6 = 0.22μF、負荷電流なし

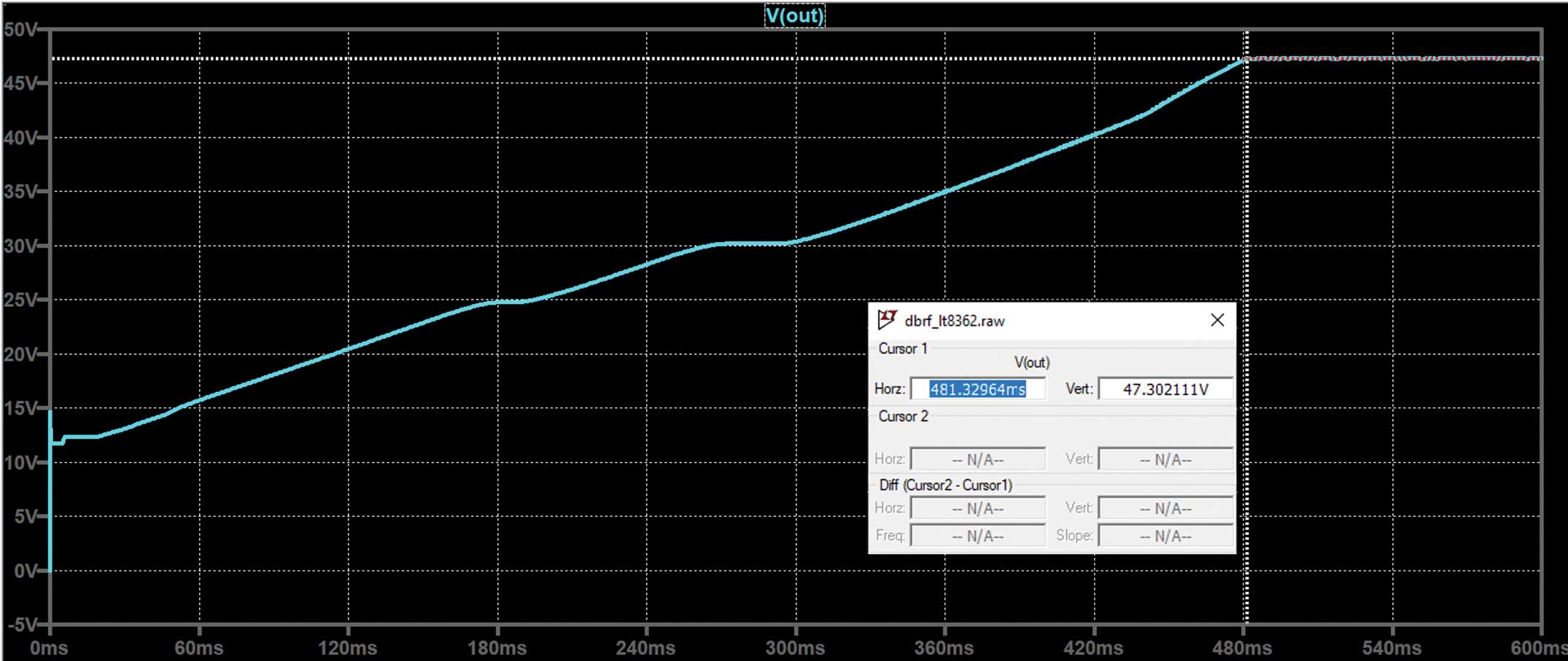

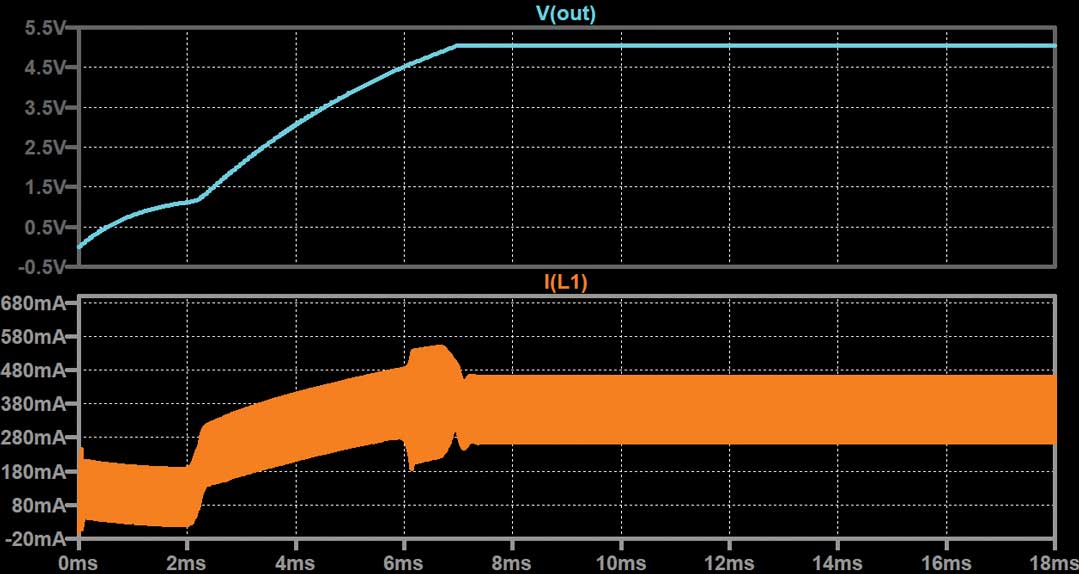

ソフト・スタートの式がない場合は、回路の動作を予測するための有効なツールとしてLTspice®を利用することができます。図12は、約500msのスタートアップ時間を示した図10の測定を、LTspiceでシミュレーションした結果です。0.22μFのソフト・スタート・キャパシタを使用した場合の無負荷時と電流が0.19A時のシミュレーションも、図11と図8の結果と同じ約12msと約50msで、いずれも正しい結果を示しています。ソフト・スタートの式が明確に示されていない場合でも、LTspiceシミュレーションを利用することによって、回路の動作を予測してソフト・スタート時間を見積もることが可能になります。これは、回路の性能を理解して最適化するための貴重なツールとなり得ます。

図12. LT8362のスタートアップ波形のLTspiceシミュレーション。図10に示す結果に対応しています。

図13. LT8362のLTspiceシミュレーションは正しい結果を示しており、図11と図8に対応しています。

ソフト・スタート機能がないときにこれを追加する方法:

ICにソフト・スタート機能がない場合、出力キャパシタが充電されていないときにICがそれらのキャパシタに供給しようとする電流の値は、そのICの最大電流または制限電流です。ソフト・スタート機能を追加するには、遅延を発生させるためのRCの組合せなどの追加ディスクリート部品が必要で、保護用のダイオードやFETが必要になることもあります。LT3990は、62V/0.35A FET、超低IQ(静止電流)、AEC-Q100適合、広い動作周波数範囲、極めて小さい出力電圧リップルなどの特徴を持つ降圧レギュレータです。しかしソフト・スタート機能はありません。データシートには、代表値0.7Aの電流制限値が仕様規定されています。ディスクリート部品の追加前と追加後のLT3990の動作は、組込みのLTspiceサンプル回路(図14参照)を使用して評価することができます。この回路は10Vを5V/0.35Aに変換します。この回路をシミュレートすることによって、ソフト・スタート機能がない場合は、スタートアップ時にインダクタ電流が電流制限(代表値)に達することが分かります(図15)。

図14. LTspiceのLT3990用組込みデモ回路

図15. スタートアップ時に制限値に達するLT3990のインダクタ電流

FBピンとの間に単純なRCの組合せと保護ダイオードを追加することで、FB電圧を徐々に増加させることができます。これは、スタートアップ電圧の増加をスロー・ダウンして突入電流を小さくします(図16)。図17は、短時間ながら発生する初期電流サージを示す回路シミュレーションです。このアプローチは、電流と出力電圧の両方を制御された形でランプ・アップさせることを可能にするもので、コスト効果に優れたソフト・スタート機能の組込み方法を提供します。ただし、このソリューションはパワー・グッド(PG)ピンに影響を与える可能性があることを考慮する必要があります。PGピンはソフト・スタート回路によって緩やかにランプ・アップしますが、そのために、高速のパワー・グッド信号に依存する特定の設計では、このソリューションが不向きなものとなる可能性があります。

図16. C4、R6、D1を追加してLT3990のFBピンをバイアスし、スタートアップ動作をスロー・ダウン。

図17. シミュレーション結果には依然としてピーク電流が生じていますが、ランプ・アップは緩やかになっています。

スタートアップ時のサージ電流を完全に除去するためのもう1つの方法は、FETによってバイパスされる直列抵抗を追加することです。FETがそのVgs(th)定格に達して導通を開始するまでに要する時間の長さは、RC定数と入力電源によって決まります。このアプローチを取り入れた回路の例を図18に示します。図19はそのシミュレーション結果です。この構成を使用することによって、スタートップ時のサージ電流を効果的に除去できます。FETが閾値電圧に達して導通を開始するまでに要する時間は、抵抗とキャパシタの値によって決まるRC定数と、入力電源の特性によって決まります。これは、出力電圧と出力電流を制御された形で徐々に増加させることを可能にして、スタートアップに付きもののサージ電流をなくします。

図18. M1とRC を追加して制限抵抗R5をバイパス。

図19. 電流はまずR5によって制限されて電流サージをなくし、Vgs(th)に達すると電流が徐々にランプ・アップします。

この方法は、ソフト・スタート機能を実装するための信頼できる手段を提供して、サージ電流のないスムーズで制御された形のスタートアップを実現します。ただし、望みのソフト・スタート動作を実現するには、回路の電源および負荷に関する要求を考慮しながら、抵抗、キャパシタ、およびFETの値を慎重に選ぶことが重要です。

このシミュレーションのPGピンは、オープン・ドレインの場合にそこから期待されるようには正常に動作しない可能性もあるので、すべての設計に適している訳ではありません。

まとめ

ソフト・スタートの実行方法には電圧ソフト・スタートと電流ソフト・スタートがあります。通常、電圧モード・ソフト・スタートの場合、ソフト・スタート時間tSSとCSSの関係は直線的です。しかし、電流モード・ソフト・スタートの場合は、負荷電流、出力電圧、および出力キャパシタに依存するので、関係はより複雑になります。データシートには電流モード・ソフト・スタートの明確な式が記載されていないことがあるので、ソフト・スタート時間の最小値と最大値を知るために、様々な負荷電流シナリオをテストしなければならないことがあります。電流ソフト・スタートを使用するデバイスのtSSを予想する良い方法は、LTspiceを使ってシミュレーションを行うことです。ソフト・スタート機能が組み込まれていないICで出力電圧を緩やかに増加させるには、追加部品が必要です。これらの部品がない場合、ICは電源オン時にその最大電流能力を発揮しますが、これがアプリケーションによっては望ましくないこともあります。したがって、ソフト・スタートを実装するときは、具体的な実行方法(電圧モードまたは電流モード)を理解し、様々な負荷シナリオをテストしてソフト・スタート時間を決定する必要があります。