所望のシステム性能を達成するためには、高性能A/Dコンバータ(ADC)の前段の入力構成、すなわち「フロントエンド」の設計がきわめて重要になります。設計全体の最適化は、アプリケーションの特性、システム分割、ADCのアーキテクチャなど、数多くの要因に依存しています。以下のQ&Aは、アンプとトランスを用いたADCフロントエンドの設計に関連する、実用上の重要項目を取り上げています。

Q. アンプとトランスの基本的な違いは何ですか?

A. アンプは能動素子ですが、トランスは受動素子です。アンプはすべての能動素子と同じく電力を消費してノイズを増加させますが、トランスは電力を消費せず、ノイズの増加はごくわずかです。どちらにも選択するべき機能的な効果があります。

Q. なぜアンプを使用するのですか?

A. アンプの性能は、トランスと比べてほとんど制限がありません。またDCレベルの保持が必要な場合は、アンプを使用する必要があります。トランスは本質的にAC結合のデバイスであるからです。トランスは必要に応じてガルバニック絶縁が可能です。アンプは出力インピーダンスが本質的にゲインとは無関係であるため、より簡単にゲインを得ることができます。それに対して、トランスの出力インピーダンスは、電圧ゲイン(巻線比によって決定)の2乗に応じて増大します。アンプを使用するとパスバンドの応答が平坦になり、トランスの寄生的な相互作用によるリップルがありません。

Q. 通常、アンプが付加するノイズの量はどのくらいですか? これを低減するにはどうすればよいですか?

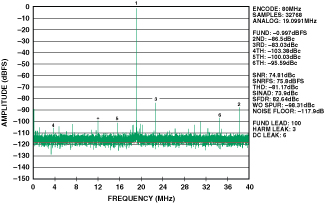

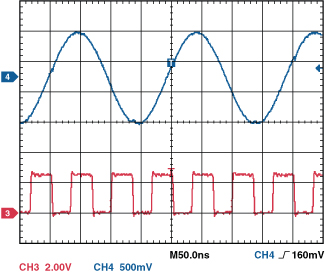

A. 標準的なアンプ、たとえばADA4937の場合で考えると、このアンプをG=1用に設定した場合、高周波における出力ノイズ・スペクトル密度は6nV/√ Hz になります。一方、80MSPSのADC AD9446-80の入力ノイズ・スペクトル密度は10nV/√Hzです。ここでの問題は、アンプのノイズ帯域幅(約500MHz)はADCの全帯域幅に相当しますが、ADCノイズは1つのナイキスト帯(40MHz)に折り返されることです。フィルタがない場合、総合ノイズは、アンプについては155μVrms、ADCについては90μVrmsになります。理論上は、これによりシステムのSNR(信号対ノイズ比)全体が6dBだけ低下します。これを実験的に確認するため、AD9446-80をADA4937で駆動した状態でSNRを測定すると76dBFSになり、ノイズ・フロアは-118dBです(図1)。トランス駆動の場合、SNRは82dBFSです。したがって、ドライバ・アンプによってSNRが6dB低下しています。

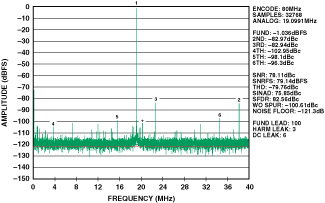

ADCのSNRを改善するためには、アンプとADCの間にフィルタを挿入します。100MHz の2 極フィルタの場合、アンプの総合ノイズは71μVrmsになり、ADCのSNRで3dB分低下します。2極フィルタを使用することで、図2aに示すように、- 121dBのノイズ・フロアで、図1 の回路のSNR性能は79dBFSまで改善します。2極フィルタは、アンプの各出力に直列に配置された24Wの抵抗と30nHのインダクタ、および差動接続された47pFのコンデンサで構成されます(図2b)。

80MSPSでAD9446-80ADCを駆動するADA4937アンプの回路図

Q. 高速アンプとADCの消費電力はどのようにして比較すればよいですか?

A. 使用するアンプとADCによって異なります。類似の消費電力を持つ標準的な2つのアンプとして、5Vで37mA(185mW)を消費するAD8352と、5Vで40mA(200mW)を消費するADA4937があります。3.3V電源を使用することで性能はわずかに低下しますが、総消費電力を約3分の1だけ削減できます。ADCの消費電力は、分解能と速度に応じて多岐にわたっています。16ビット、80MSPSのAD9446-80 は2.4Wを消費し、14ビット、125MSPSのAD9246-125は415mWを消費し、12ビット、20MSPSのAD9235-20はわずか95mWしか消費しません。

Q. トランスを使用する必要があるのはどのような場合ですか?

A. トランスは、非常に高い信号周波数のとき、およびADC入力段で大きな付加ノイズを許容できないときに、アンプに比べて優れた性能を発揮します。

Q. ゲインを設けるとき、トランスとアンプではどのような違いがありますか?

A. 主な違いは、ADC入力に加わるインピーダンスであり、これはシステム帯域幅に直接影響します。トランスの入出力インピーダンスは、巻線比の2乗に関係しますが、アンプの入出力インピーダンスは、基本的にゲインとは無関係です。

たとえば、G=2のトランスを50Wの信号源インピーダンスから使用するとき、トランスの2次側に現れるインピーダンスは200Wです。AD9246 ADCの差動入力容量は4pFですが、これが200Wのトランス・インピーダンスと結合して、ADCの-3dB帯域幅を650MHzから200MHzに低減しています。性能を向上してコンバータからのキックバックを低減するためには、ほとんどの場合、特別な直列抵抗と差動容量が必要であり、これにより-3dBの帯域幅をさらに100MHzまで制限する可能性があります。

ADA4937などの低出力インピーダンスのアンプを使用した場合は、非常に低い信号源インピーダンス(通常5W未満)になります。25W の過渡電流制限抵抗を各ADC入力と直列に使用できます。AD9246の場合は、ADCのアナログ入力帯域幅650MHzの全体を使用できます。

ここまでは-3dB帯域幅について説明してきました。さらに厳しい平坦性が必要な場合は(1極システムで0.5dBなど)、-3dB帯域幅は約3倍の幅が必要となります。1極で0.1dBの平坦性の場合、この割合は6.5倍まで上昇します。0.5dB平坦性が最大150MHzで必要な場合、450MHzを超える-3dB帯域幅が必要となります。これをG=2のトランスで実現することは困難ですが、低出力インピーダンスのアンプでは簡単に実現できます。

Q. ADCを駆動するためのトランスやアンプを選択する場合、考慮すべき要素は何ですか?

A. 以下の6つのパラメータに注目してください。

| パラメータ | 通常の設定 |

| 帯域幅 | トランス |

| ゲイン | アンプ |

| パスバンド平坦性 | アンプ |

| 電源要件 | トランス |

| ノイズ | トランス |

| DC対AC結合 |

アンプ(DCレベルの保持)

トランス(DC絶縁) |

主要なパラメータが競合するアプリケーションでは、さらに解析とトレードオフが必要です。

Q. この解析で考慮すべき事項は何ですか?

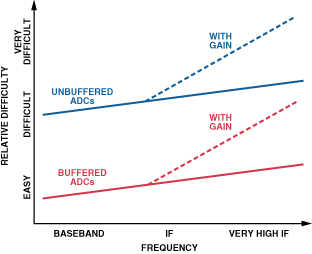

A. あるADCのフロントエンドを設計する場合、その難易度を把握することから始める必要があります。最初に、ADCは内部バッファ付きですか、バッファなし(スイッチド・キャパシタ・タイプなど)ですか? いずれの場合も周波数が上がると、必然的に難易度が増します。ただし、スイッチド・キャパシタ・タイプの方が設計は一段と難しくなります。

ADCの入力範囲を十分に活用するためにゲインが必要な場合、トランスを利用するアプリケーションでは、必要なゲイン(巻線比)が上昇するほど、難易度も上昇します。

当然ながら、難易度は周波数とともに増します。バッファ付きADCを備えた100MHz未満のIFシステムの設計は、図3に示すように、非バッファADCを使用する低信号レベルの高IF設計に比べてかなり簡単になります。多くのパラメータがさまざまに設定されている場合は、トレードオフが難しくなる場合があり、ほとんどの場合、部品の変更や評価を行う際の追跡が困難になります。

スプレッドシートや表を利用して、設計の進行にともなってパラメータのすべてをそのまま保存しておくと便利です。すべての場面にあてはまる最適な設計はありません。入手可能な部品やアプリケーションの仕様によって、最適な設計は異なります。

Q. わかりました。設計は難しいということですね。では、システム・パラメータの詳細についてはどうですか?

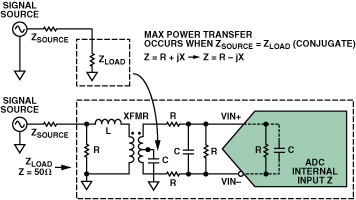

A. 最初に、ADCのフロントエンドを設計する際にすべてを考慮に入れることが最も重要です。各部品を前段の負荷の一部と見なす必要があり、ZSOURCEが共役ZLOADのときに最大の電力伝送が生じます(図4)。

ここから、設計パラメータに話を進めましょう。

「入力インピーダンス」は、設計の特性インピーダンスです。ほとんどの場合、これは50Wですが、異なる値が必要になる場合があります。トランスは、良好なトランスインピーダンス・デバイスになります。これを使えば、必要に応じて、異なる特性インピーダンス間のカップリングが可能になり、システムの全体負荷の平衡を完全に保つことができます。増幅回路では、入出力特性としてインピーダンスが規定されており、トランスのように周波数に対して変化することがないように設計できます。

「電圧定在波比(VSWR)」は、無次元パラメータであり、これを使用すると、対象とする帯域幅の全体にわたって負荷に反映される電力量を把握できます。これは重要な尺度であり、ADCのフルスケール入力を実現するのに必要な入力駆動レベルを決定できます。

「帯域幅」は、システムで使用される周波数の範囲です。ベースバンドは狭い場合もあれば広い場合もあります。また、複数のナイキスト帯を対象とすることもできます。帯域幅の周波数制限は通常-3dBポイントです。

「パスバンド平坦性(またはゲイン平坦性)」は、規定した帯域幅内の周波数に対する応答(正および負)のばらつきを規定します。これは、バターワースのフィルタ特性と同様に、リップルの場合もあれば単調ロールオフの場合もあります。どのような場合でもパスバンド平坦性は通常1dB以下にする必要があり、システム・ゲイン全体を設定するのに重要となります。

「入力駆動レベル」は、特定のアプリケーションに必要なシステム・ゲインによって決定されます。帯域幅仕様と密接に関係し、フィルタやアンプ/トランスなど、選択したフロントエンド部品に依存します。その特性のため、駆動レベルの要件は維持することが最も難しいパラメータの1つになります。

「信号対ノイズ比(SNR)」は、フルスケール信号のRMS値と、所定の帯域幅内のすべてのノイズ成分(ただし歪み成分は含まれていません)の2乗和の平方根との対数比です。フロントエンドの観点からは、帯域幅、ジッタ、ゲインの増加とともにSNRは低下します(低ゲインでは無視できる程度であったアンプのノイズ成分が、高ゲインでは顕著になります)。

「スプリアス・フリー・ダイナミック・レンジ(SFDR)」は、フルスケールのRMS値と、最大スプリアス・スペクトル成分のRMS値との比です。フロントエンドにおけるスプリアスの2つの大きな要因は、主として2次高調波歪みを生成するアンプの非直線性(すなわちトランスの完全な平衡の欠如)と、入力ミスマッチおよびゲインによるその増幅であり(高ゲインになるほどマッチングは難しくなり、寄生非直線性は増幅されます)、通常、3次高調波歪みと見なされます。

Q. トランスについて認識すべき重要なこととは何ですか?

A. トランスには、電圧ゲインとインピーダンスの比率、帯域幅と挿入損失、大きさと位相の不平衡、リターン損失など、さまざまな特性があります。その他の要件として、電力定格、構成のタイプ(バランやトランスなど)、センター・タップのオプションがあります。

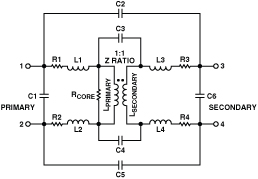

トランスの設計は、必ずしも簡単というわけではありません。たとえば、トランスの特性は周波数に対して変化するため、モデルが複雑になります。ADCアプリケーション用のトランスをモデル化する場合の基本例を図6に示します。各パラメータは、選択したトランスによって決まります。可能であれば、トランスのメーカーに連絡してモデルを入手することを推奨します。

主なトランスの特性を以下に示します。

「巻線比」は、2次電圧と1次電圧との比です。

「電流比」は、巻線比に反比例します。

「インピーダンス比」は、巻線比の2乗です。

「信号ゲイン」は、理想的には巻線比と等しくなります。電圧ゲインは本来ノイズフリーですが、以下で取り上げるその他の事項を考慮する必要があります。

トランスは、単純にいえば、公称ゲインを備えたパスバンド・フィルタと見なすことができます。「挿入損失(規定した周波数範囲におけるフィルタの損失)」は、データシートに記載された最も一般的な測定仕様ですが、それ以外にも考慮すべき事項があります。

「リターン損失」は、トランスの1次側で見られる、2次側の終端の実効インピーダンスのミスマッチの尺度です。たとえば、2次側対1次側の巻数比の2乗が2:1の場合、2次側を100Wで終端すると、1次側に50Wのインピーダンスが反映されると想定されます。ただし、この関係は正確ではありません。たとえば、1次側に反映されるインピーダンスは、周波数によって変動します。通常、インピーダンス比が大きくなると、リターン損失のばらつきも大きくなります。

「振幅」および「位相不平衡」は、トランスを検討する際のきわめて重要な性能特性です。これらの2つの仕様がわかれば、高IF周波数(100MHzを上回る)が設計で必要な場合に、どの程度の非直線性が求められるのかについての見通しを得ることができます。周波数が上昇すると、トランスの非直線性も大きくなり(通常は位相不平衡が主体)、偶数次歪み(主に2次高調波)に変換されます。

図7は、シングル/ダブル・トランス構成における、周波数の関数としての標準的な位相不平衡を示しています。

すべてのメーカーがすべてのトランスを同じ方法で規定しているわけではありません。一見したところ仕様が同じトランスであっても、同じ状況において異なる動作をする可能性があります。設計に合ったトランスを選択する最良の方法は、対象となるすべてのトランスの仕様を集めて理解し、メーカーのデータシートに記載されていない主要なデータ項目があれば請求することです。この他にも、ネットワーク・アナライザを使用して自分でその性能を測定してみるとよいでしょう。

Q. アンプを選択する際は、どのパラメータが重要ですか?

A. トランスの代わりにアンプを使用する主な理由は、より良いパスバンド平坦性を得るためです。設計上、この仕様が重要である場合、アンプの方がばらつきが小さく、周波数範囲全体で±0.1dB(typ)になります。トランスは応答が平坦ではないため、トランスを使用する必要があって平坦性が問題となる場合は微調整が必要です。

アンプを使用するもう1つの利点は駆動能力です。トランスは、PCボード上の長いパターンを駆動するように作られたものではなく、ADCに直接接続することを想定しています。「ドライバ/カプラ」をADCから離れたところや別のボードに配置するようシステム要件に記述されている場合、アンプを強く推奨します。

DC結合であることもアンプを使用する理由になります。トランスは本質的にAC結合であるからです。高周波アンプは、DCに至るまでのすべての周波数で結合できます(スペクトルのその部分がアプリケーションにおいて重要である場合)。検討すべき標準的なアンプとして、AD8138とADA4937があります。

また、アンプは動的絶縁(約30~40dBの逆絶縁)も可能であり、非バッファADCの入力における過渡電流からのキックバック・グリッチを抑えることができます。

設計に広帯域ゲインが必要な場合、アンプは、ADCのアナログ入力に対して、トランスよりも優れたマッチングを実現します。

別のトレードオフとして、帯域幅対ノイズがあります。150MHzを超える周波数を必要とする設計の場合、トランスの方が、SNRとSFDRを保持するのに優れた働きをします。ただし、1番目または2番目のナイキスト帯では、トランスまたはアンプのいずれでも使用できます。

Q. 高性能ADCを駆動するには、どのアナログ・デバイセズのアンプがよいですか?

A. 高速ADCのフロントエンドに最適なアンプはほんの少数ですが、AD8138、AD8139、AD8350、AD8351、AD8352、ADA4937、ADA4938などが該当します。

対象とする入力周波数が50MHz未満の場合、ベースバンド設計には一般的にAD8139を使用します。高IF設計の場合は、一般的にAD8352を使用します。このアンプは、かなり広い周波数帯域(最大200MHzの範囲)にわたって、ノイズとスプリアスを良好に除去しています。ADA4937は、最大150MHzの周波数に使用できます。広範囲の同相出力電圧を取り扱うことができるため、ADCとDC結合されるアプリケーションで大きな利点となります。

Q. 使用できるADCの重要な特性とはどのようなものですか?

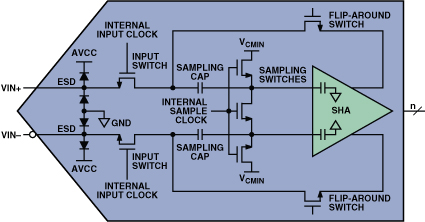

A. 一般的なCMOSスイッチド・キャパシタADCは、内部入力バッファがないため、バッファ付きタイプよりも消費電力がはるかに低くなります。外部電源は、ADCの内部スイッチド・キャパシタのサンプル&ホールド(SHA)回路に直接接続します(図8)。これにより、2つの問題が生じます。第1に、時間とともに、また、モードが「サンプル」と「ホールド」の間で切り替わるたびに入力インピーダンスが変化します。第2に、サンプリング・コンデンサに注入された電荷が信号源に反射します。このため、駆動回路の受動フィルタに対してセトリング遅延を生じる場合があります。

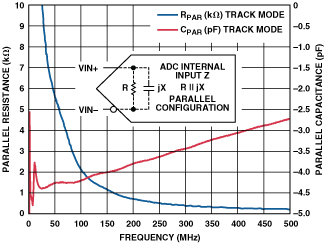

図9に示すように、ADCトラック・モード・インピーダンスに外部ネットワークをマッチングさせることが重要です。この図でわかるように、入力インピーダンスの実数部すなわち抵抗部(青線)は、低周波(ベースバンド)で非常に高くなり(数キロオームのレンジ)、100MHzを超えると2kW未満に減衰します。

入力インピーダンスの虚数部、すなわち容量部(赤線)は、かなり大きな容量性負荷から始まり、高周波で約3pF(右側の目盛)まで次第に減少します。

この入力構造にマッチングさせることは、特に100MHzを超える周波数では、かなり困難な設計課題になります。

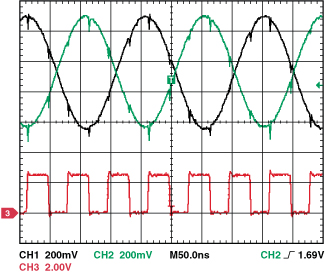

図10と11の波形は、差動信号方式の利点を示しています。一見すると、図10の各シングルエンドのADC入力波形はかなり乱れているように見えます。ただし、図11は、シングルエンドのパターンの破損が単に同相の影響であることを示しています。

差動測定のADC入力を見ると(図11)、入力信号がはるかにクリアであることがわかります。クロックに関連する「破損」グリッチは消滅しています。差動信号に固有の同相ノイズ除去によって、電源、デジタル信号源、電荷注入のいずれの同相ノイズも相殺しています。

バッファ付き入力ADCは、さらに簡単に理解して使用できます。入力信号源は、一定のインピーダンスで終端されています。信号は、低インピーダンスで変換プロセスを駆動するトランジスタ段によってバッファリングされるため、電荷注入スパイクとスイッチングの過渡電流は著しく低減します。スイッチド・キャパシタADCとは異なり、入力終端は、ADCのアナログ入力周波数範囲に対してほとんどばらつきがないため、適切な駆動回路を簡単に選択できます。バッファは、特に優れた直線性と低ノイズを発揮できるように設計されていますが、唯一のマイナス面は、その消費電力によりADC全体の電力消費が増加することです。

Q. トランスおよびアンプの駆動回路の例はありますか?

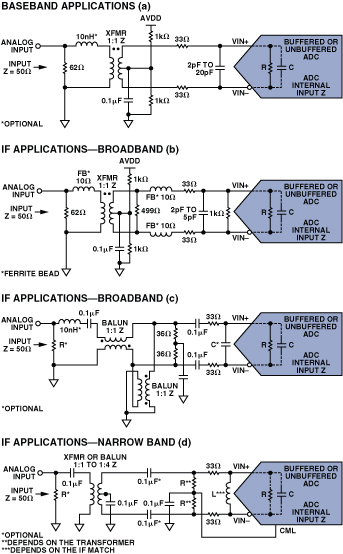

A. 図12に、トランスを使用したADC入力構成の4つの例を示します。

ベースバンド・アプリケーション(a)では、入力インピーダンスはかなり大きくなるため、マッチングは、高周波でのマッチングよりも簡単で、またそれほど重要でもありません。通常、値の小さな直列抵抗だけで、差動接続されたコンデンサによる電荷注入を十分に減衰させることができます。この単純なフィルタによってブロードバンド・ノイズを減衰させ、最適な性能を達成できます。

ブロードバンド・アプリケーション(b)で適切にマッチングされた入力を得るには、入力の実数(抵抗)成分が主体となるようにします。アナログ・フロントエンドと並列または直列のインダクタやフェライト・ビーズで、容量性の項を最小化します。これにより、良好な帯域幅が得られ、ゲイン平坦性が向上し、AD92xxのスイッチド・キャパシタADCファミリーを使用して見られるような性能(SFDR)の向上が得られます。

バッファ付き高IFアプリケーション(c)の場合、ベースバンド構成と類似のフィルタを備えたダブルバラン構成を示しています。これにより、最大300MHz の入力が可能となり、また偶数次歪みを最小化する優れた平衡が得られます。

ナローバンド(共振)アプリケーション(d)の場合、トポロジはブロードバンドとよく似ています。ただし、規定された周波数に帯域幅を狭めるため、マッチングは直列ではなく並列になっています。

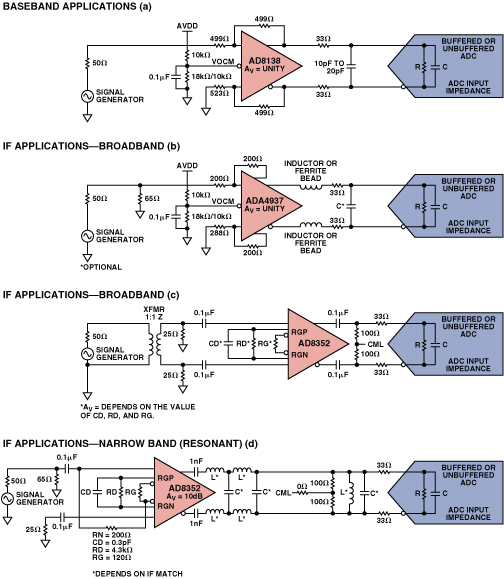

ベースバンド・アプリケーションでアンプをバッファ付きまたは非バッファADCに使用するときの設計はかなり簡単です(図13)。アンプの同相電圧がADCと分配されるようにし、さらに簡易なローパス・フィルタを使用して不要なブロードバンド・ノイズを除去するだけです(a)。IFアプリケーション(bとc)のマッチング・ネットワークはベースバンドのものと基本的によく似ていますが、通常は、ロールオフが浅くなります。インダクタやフェライト・ビーズをアンプの出力で使用することで、必要に応じて帯域幅を広げることができます。ただし、これは必ずしも必要ではありません。アンプはトランスに比べて、対象とする帯域に対して特性が変動する傾向が少ないからです。ナローバンドまたは共振アプリケーションの場合(d)、フィルタはアンプの出力インピーダンスにマッチングされて、ADCの入力容量を相殺しています。通常、多極フィルタを使用して、対象とする周波数領域外のブロードバンド・ノイズを除去します。

Q. 重要な点をまとめるとどうなりますか?

A. 新しい設計に取り組む際は、以下の点に留意してください。

- 設計の難易度を理解する。

- 設計の重要なパラメータを格付けする。

- トランスやアンプの全負荷を求める際には、ADC入力インピーダンスと外付け部品を入力回路に含める。

トランスを選択する際は、以下の点に留意してください。

- すべてのトランスが等しく作られているとは限らない。

- トランスの仕様を理解する。

- 与えられていないパラメータについては、メーカーに問い合わせてモデル化する。

- 高IF設計は、トランスの位相不平衡に影響されやすい。

- 超高IF設計において、偶数次歪みを抑制するためには、2つのトランスまたはバランを必要とする場合がある。

アンプを選択する際は、以下の点に留意してください。

- ノイズ仕様に注目する。

- アンプ仕様を理解する。

- 低IFまたはベースバンド周波数には、AD8138/AD8139を使用する。

- 中間IFには、ADA4937を使用する。

- 高IF設計では、AD8352を使用する。

- アンプは不平衡の影響を受けにくく、偶数次歪みを自動的に抑制する。

- 一部のアンプは、ADCの入力にDC結合できる(AD8138/AD8139やADA4937/ADA4938など)。

- アンプは本質的に出力負荷の影響から入力信号源を分離しているため、影響を受けやすい入力信号源を取り扱う場合、トランスよりも便利である。

- アンプは長い距離にわたって駆動できるため、システム分割によって複数のボードが設計で要求されるときに特に便利である。

- アンプは別の電源領域を必要とする場合があり、常にシステムの電力要件が増大することになる。

ADCを選択する際は、以下の点に留意してください。

- ADCは内部でバッファリングされるのか?

- スイッチド・キャパシタADCの入力インピーダンスは時間とともに変化するため、高IFで設計することは難しい。

- 非バッファADCを使用する場合、常にトラック・モードで入力マッチングを行う。

- バッファ付きADCは、高IFにおいても設計が簡単である。

- バッファ付きADCは、より多くの電力を消費する傾向がある。

最終的にまとめると、次のようになります。

- ベースバンド設計は、どのタイプのADCでも最も簡単である

- フェライト・ビーズや低Qインダクタを使用して、スイッチド・キャパシタADCの入力容量を調整する。これにより、入力帯域幅が最大になり、良好な入力マッチングが得られ、またSFDRが維持される。

- 高IFを設計するためには、場合によっては2つのトランスが必要となる。

Q. 詳細な参考文献はありますか?

A. アプリケーション・ノート

AN-742 「スイッチド・キャパシタADCの周波数領域応答」

AN-827 「共振方式によるアンプとスイッチド・キャパシタADCのインターフェース」(日本語版あり)

B. 技術記事

Rob Reeder 著「Transformer-Coupled Front-End for Wideband A/D Converters」(Analog Dialogue、2005年第39巻第2号、3~6ページ)

Rob Reeder、Mark Looney、Jim Hand 著「Pushing the State of the Art with Multichannel A/D Converters」(Analog Dialogue、2005年第39巻第2号、7~10ページ)

Walt Kester著「Which ADC Architecture Is Right for Your Application?」(Analog Dialogue、2005年第39巻第2号、11~18ページ)

Rob ReederおよびRamya Ramachandran著「Wideband A/D Converter Front-End Design Considerations - When to Use a Double Transformer Configuration」(Analog Dialogue、2006年第40巻第3号、19~22ページ)

C. テクニカル・データ

AD9246 :80/105/125MSPS、14ビット、1.8V、スイッチド・キャパシタADC

AD9445 :105/125MSPS、14ビット、5/3.3V、バッファ付きADC

AD9446 :16ビット、80/100MSPS、バッファ付きADC

AD8138 :低歪み差動ADCドライバ

AD8139 :超低ノイズ完全差動ADCドライバ

AD8350 :1.0GHz差動アンプ

AD8351 :低歪み完全差動RF/IFアンプ

AD8352 :2GHz超低歪み差動RF/IFアンプ

ADA4937 :超低歪み差動ADCドライバ

ADA4938 :超低歪み差動ADCドライバ

AD9215、AD9226 、AD9235 、AD9236 、AD9237 、AD9244 、AD9245のADCスイッチド・キャパシタ入力インピーダンスのデータ(Sパラメータ)については、各製品ページの「評価用ボード」をクリックして、s-parameterデータをダウンロードしてください。