概要

設計リソース

機能と利点

- 高 IF サンプリング・レシーバ

- 127MHz バンドパス・フィル

- SNR = 71.7dBFS, SFDR = 92dBc

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

UG-386: Evaluating the AD9642/AD9634/AD6672 Analog-to-Digital Converters2012/04/12PDF3293 kB

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

CN0279: 12-Bit ,1 MSPS SAR ADC and Driver with Total Power Dissipation Less than 5 mW2012/07/23PDF169 kB

回路機能とその特長

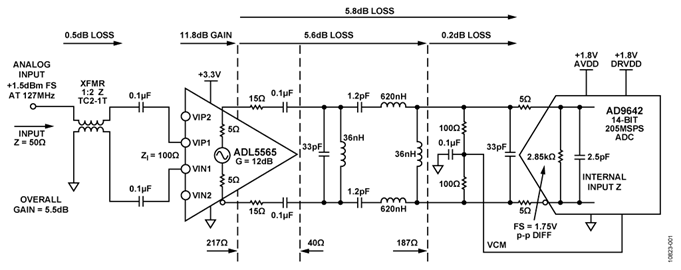

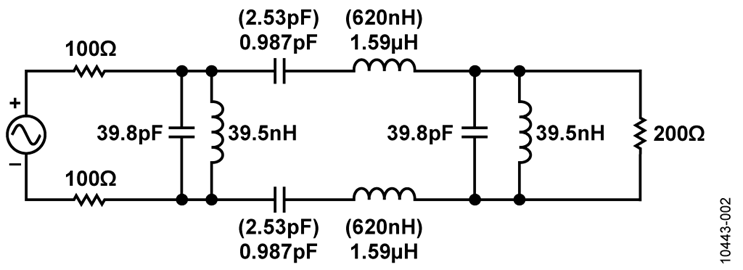

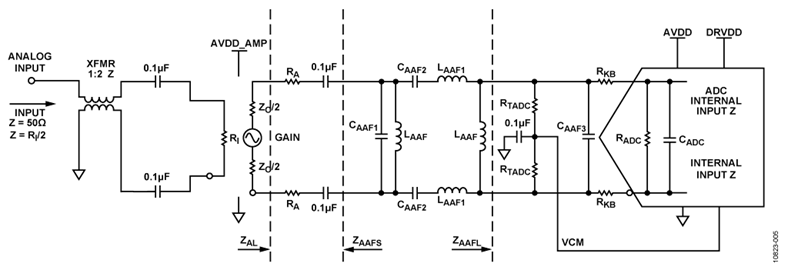

図1に示す回路は、超低ノイズ差動アンプ・ドライバADL5565と14ビット、250MSPS A/Dコンバータ(ADC)AD9642をベースにした狭帯域バンドパス・レシーバ・フロントエンドです。

3次バターワース・アンチエイリアシング・フィルタは、アンプとADCの性能とインターフェースの要件に基づいて最適化されています。フィルタ回路やその他の要素による総合挿入損失はわずか5.8dBです。

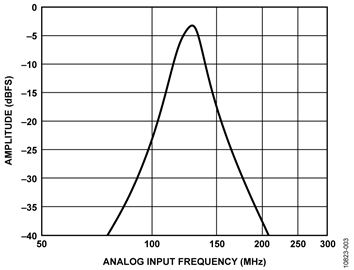

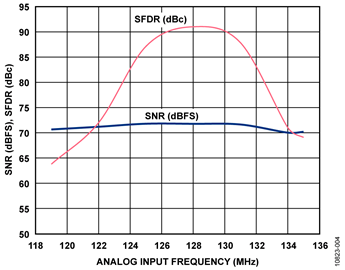

通過帯域の平坦度が3dBの回路全体の帯域幅は18MHzです。127MHzのアナログ入力で測定した信号対ノイズ比(SNR)とスプリアスフリー・ダイナミック・レンジ(SFDR)は、それぞれ71.7dBFSと92dBcです。サンプリング周波数が205MSPSなので、第2ナイキスト・ゾーンのIF入力信号の位置は102.5MHzと205MHzの間になります。

回路説明

この回路はシングルエンド入力を受け入れ、広帯域(3GHz)1:2トランスMini-Circuits TC2-1Tを使って差動入力に変換します。6GHzの差動アンプADL5565の差動入力インピーダンスは、6dBのゲインで動作するときに200Ω、12dBのゲインで動作するときに100Ωと異なる値を持ちます。15.5dBのゲインも選択できます。ADL5565はAD9642に最適なドライバであり、バンドパス・フィルタを経由してADCへ入力するまで完全差動構成になっているため、優れた高周波数同相ノイズ除去性能を提供するとともに、2次歪み成分を最小限に抑えます。ADL5565のゲインは入力接続に応じて6dBまたは12dBになります。この回路では、フィルタ回路とトランスの挿入損失(約5.8dB)を補償するために12dBのゲインを使って、全体の信号ゲインを5.5dBにしました。

1.5dBmの入力信号で、ADC入力に1.75V p-pのフルスケール差動信号が生成されます。

アンチエイリアシング・フィルタは、標準フィルタ設計プログラムを使って設計した3次バターワース・フィルタです。バターワース・フィルタを選択した理由は通過帯域が平坦なためです。3次フィルタのACノイズ帯域幅比は1.05で、Nuhertz Technologies Filter Freeやquite universal circuit simulator (Qucs) free simulationのようないくつかの無償のフィルタ・プログラムで設計することができます。

最高の性能を得るには、ADL5565に200Ωの差動負荷をかけます。15Ωの直列抵抗はフィルタ容量をアンプ出力から隔離し、後段のインピーダンスと並列の100Ω抵抗は、30Ωの直列抵抗に接続されることで217Ωの負荷インピーダンスになります。

ADC入力と直列の5Ω抵抗は内部スイッチング・トランジェントをフィルタとアンプから隔離します。

2.85kΩの入力インピーダンスは、AD9642のホームページでダウンロード可能なスプレッドシートを使って決定したものです。対象となるIF周波数の中心でパラレル・トラック・モード値を使用するだけです。このスプレッドシートには実数と虚数の両方の値が示されています。

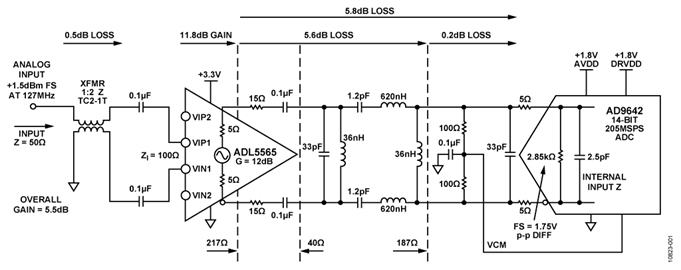

3次バターワース・フィルタは、200Ωの信号源インピーダンス(差動)、200Ωの負荷インピーダンス(差動)、127MHzの中心周波数、および20MHzの3dB帯域幅を使って設計しました。標準フィルタ設計プログラムで計算した値が図1に示されています。必要な直列インダクタンスの値が大きいため、1.59μHのインダクタを620nHまで小さくし、0.987pFのコンデンサをそれに応じて2.53pFまで大きくすることで、より現実的な部品の値を使って同じ127MHzの共振周波数を維持しています。

ADCの2.5pFの内部容量が2番目のシャント・コンデンサの値から差し引かれ、この値は37.3pFになっています。回路では、電荷キックバックを低減/吸収するため、このコンデンサをADCの近くに配置しています。

実際の回路の寄生要素に対して調整した後の最終的なフィルタの受動部品として選択した値が、図1に示されています。

システムの実測性能を表1にまとめてあります。ここでは、127MHzを中心とした3dB帯域幅は18MHzです。回路の総合挿入損失は約5.8dBです。周波数応答を図3に、SNRとSFDRの性能を図4に、それぞれ示します。

| Performance Specifications at -1 dBFS (FS = 1.75 V p-p), Sample Rate = 205 MSPS | Final Results |

| Center Frequency | 127 MHz |

| Pass-Band Flatness (118 MHz to 136 MHz) | 3 dB |

| SNRFS at 127 MHz | 71.7 dBFS |

| SFDR at 127 MHz | 92 dBc |

| H2/H3 at 127 MHz | 93 dBc/92 dBc |

| Overall-Gain at 127 MHz | 5.5 dB |

| Input Drive at 127 MHz | 0.5 dBm (-1 dBFS) |

フィルタとインターフェースの設計手順

このセクションでは、バンドパス・フィルタを備えたアンプとADCのインターフェースの一般的な設計手順について説明します。最適な性能(帯域幅、SNR、およびSFDR)を実現するために、アンプとADCを使った一般的な回路はある程度の設計上の制約を受けます。

- 最適な性能を得るには、アンプに接続されるDC負荷にデータシートで推奨されている適正な値を設定する必要があります。

- アンプとその負荷(フィルタ)の間に適正な大きさの直列抵抗を接続する必要があります。この抵抗は通過帯域での望ましくないピーキングを防ぐためのものです。

- ADCへの入力は外付け並列抵抗によって低減することが必要で、ADCをフィルタから隔離するために適正な直列抵抗を接続する必要があります。この直列抵抗はピーキングの低減も行います。

図5に示す一般的な回路はほとんどの高速差動アンプとADCのインターフェースに適合し、バンドパス・フィルタの基本として使用されています。この設計方法は、ほとんどの高速ADC の入力インピーダンスが相対的に高いことと駆動源(アンプ)のインピーダンスが相対的に低いことを利用して、フィルタの挿入損失を最小限に抑える傾向があります。

基本的な設計プロセスを以下に示します。

- RTADCとRADCの並列接続の値が200Ω~400Ωになるように、外付けADC終端抵抗RTADCを設定します。

- 経験値またはADCのデータシートの推奨値を基にRKBを選択します(標準的には5Ω~36Ω)。

- . 次式を使ってフィルタの負荷インピーダンスを計算します。

- アンプの外付け直列抵抗RAを選択します。アンプの差動出力インピーダンスが100Ω~200Ωの場合はRAを10Ωより小さくし、アンプの出力インピーダンスが12Ω以下の場合はRAを5Ω~36Ωにします。

- アンプから見た総合負荷ZALが個別の差動アンプに適合するように次式を使ってZAAFLを選択します。

- 次式でフィルタのソース抵抗を計算します。

- フィルタ設計プログラムまたは表を利用し、信号源インピーダンスZAAFS、負荷インピーダンスZAAFL、フィルタ・タイプ、帯域幅、次数を使ってフィルタを設計します。周波数帯域が平坦になるように、アプリケーションの通過帯域が必要とする帯域幅より約10%高い帯域幅を使用します。

これらの予備の計算をしたら、回路の次の項目に関して速やかにレビューを行う必要があります。

- CAAF3の値がCADCより数倍大きくなるように、CAAF3の値を10pF以上にする必要があります。これにより、CADCの変動に対するフィルタの感度が最小限に抑えられます。

- フィルタが大部分のフィルタ表、フィルタ設計プログラムの制限内に入るように、ZAAFSに対するZAAFLの比が約7を超えないようにする必要があります。

- 寄生容量と部品のばらつきに対する感度を最小限に抑えるため、CAAF1の値を5pF以上にする必要があります。

- インダクタLAAFは少なくても数nHの適切な値にする必要があります。

- CAFF2とLAAF1も適切な値にする必要があります。回路シミュレータにより、これらの値が小さくなりすぎるか大きくなりすぎる場合があります。これらの値をより適切なものとするには、同じ共振周波数を維持するより好ましい標準値部品を使ってこれらの値の比率を調整するだけです。

フィルタ設計プログラムが複数のユニークなソリューション(得に高次フィルタの場合)を提供する場合があります。常に最も適切な部品値の組合せを採用するソリューションを選択する必要があります。また、シャント・コンデンサとADCの入力容量を組み合わせられるように、シャント・コンデンサが最終段となる回路構成を選択します。が必要で、ADCをフィルタから隔離するために適正な直列抵抗を接続する必要があります。この直列抵抗はピーキングの低減も行います。

回路の最適化技術とトレードオフ

このインターフェース回路のパラメータは相互に大きく依存しているため、主な仕様(帯域幅、帯域幅の平坦度、SNR、SFDR、ゲインなど)全てに対して回路を最適化することはほとんど不可能です。ただし、応答帯域幅でしばしば生じるピーキングはRAとRKBを変更することにより最小限に抑えることができます。

RAの値はSNR性能にも影響を及ぼします。RAの値を大きくすると帯域幅のピーキングが小さくなりますが、ADCをフルスケールで駆動するためにより大きな信号レベルが必要となるので、SNRはわずかに向上する傾向になります。

ADC入力のRKB直列抵抗は、ADCの内部サンプリング・コンデンサからの残留チャージ・インジェクションによって生じる歪みを最小限に抑えるように選択する必要があります。この抵抗を大きくしても帯域幅のピーキングは小さくなる傾向があります。

ただし、RKBを大きくすると信号減衰が大きくなるので、アンプはADCの入力範囲を満たすためにより大きな信号を駆動しなければなりません。

中心周波数を最適化するため、通過帯域特性と直列コンデンサCAAF2をわずかに変えることができます。

通常、ADCの入力終端抵抗RTADCは、ADCの正味入力インピーダンスが多くのアンプに固有の負荷の標準値である200Ω~400Ωになるように選択する必要があります。大きすぎるか小さすぎる値を使用すると、アンプの直線性に悪影響を与える可能性があります。

これらのトレードオフのバランスをとることは多少難しい面があります。この回路設計では、各パラメータを同じ重み付けにしたため、選択された値は全ての回路特性に対する代表的なインターフェース性能を実現します。設計によっては、システム要件に応じて、SFDR、SNR、または入力駆動レベルを最適化するために異なる値を選択することができます。

この回路のSFDR性能は図1に示されているように、アンプのインターフェース部品の値とADCのインターフェース部品の値の2つの要素で決まります。

この回路の信号が、アンプとその終端抵抗、ADC入力の間の同相電圧を遮断するために0.1μFコンデンサでAC結合されている点に注目してください。同相電圧に関する詳細についてはAD9642のデータシートを参照してください。

受動部品とPCボードの寄生容量に関する検討事項

このような高速回路の性能は適切なプリント回路ボード(PCB)のレイアウトに大きく依存します。これには電源バイパス、管理されたインピーダンス・ライン(必要な場合)、部品配置、信号配線、電源プレーン、グラウンドプレーンなどが含まれますが、これらに限定されません。高速のADCやアンプのPCBレイアウトに関する詳細については、チュートリアルMT-031とMT-101を参照してください。この他、CN-0227とCN-0238も参照してください。

フィルタの受動部品には、寄生要素が小さい表面実装コンデンサ、インダクタ、および抵抗を使用します。インダクタはCoilcraftの0603CSシリーズから選択しました。フィルタの表面実装コンデンサは安定性と精度を考慮して、5%、C0G、0402タイプを使用しました。

システムの詳細な文書についてはCN-0279設計サポート・パッケージを参照してください。

回路の評価とテスト

この回路は、修正したAD9642-250EBZ回路ボードとFPGAをベースにしたHSC-ADC-EVALCZ データ・キャプチャ・ボードを使用します。2つのボードには接続用高速コネクタが備わっているので、回路のセットアップと性能評価を短時間で行うことができます。修正したAD9642-250EBZボードには、この回路ノートに記述されているように評価済み回路が含まれています。ADCを適切に制御してデータをキャプチャするために、HSC-ADC-EVALCZデータ・キャプチャ・ボードをVisualAnalog®評価用ソフトウェアならびにSPIコントローラ・ソフトウェアとともに使用します。AD9642-250EBZボードの回路図、部品表、レイアウトについてはユーザー・ガイドUG-386(英語版)を参照してください。CN-0279設計サポート・パッケージの中のreadme.txtファイルに標準AD9642-250EBZボードの修正点が記述されています。アプリケーションノートAN-835には、この回路ノートに記述されているテストを実行するためのハードウェアとソフトウェアのセットアップ方法が記載されています。