AD6676

推荐用于新设计宽带中频接收机子系统

- 产品模型

- 1

产品详情

- 高瞬时动态范围

- 噪声系数(NF)低至13 dB

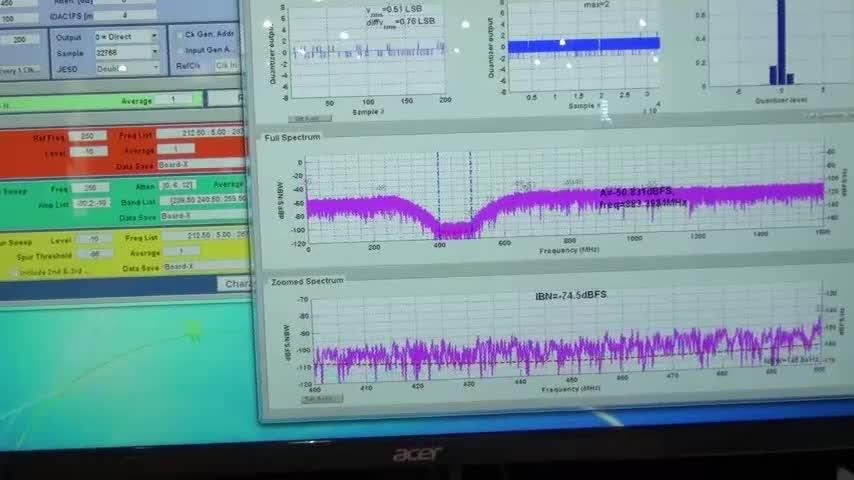

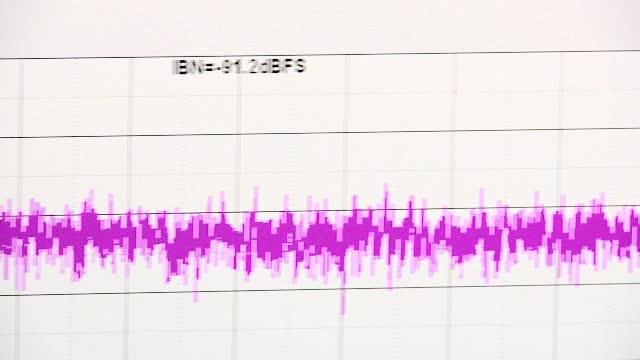

- 噪声频谱密度(NSD)低至−159 dBFS/Hz

- IIP3高达36.9 dBm,杂散音低于−99 dBFS

- 可调谐带通Σ-Δ型模数转换器(ADC)

- 信号带宽:20 MHz至160 MHz

- 中频中心频率:70 MHz至450 MHz

- 可配置输入满量程电平:−2 dBm至−14 dBm

- 易于驱动的阻性中频输入

- 1 dB增益平坦度,带外峰化低于0.5 dB

- 混叠抑制大于50 dB

- 2.0 GSPS至3.2 GSPS ADC时钟速率

- 片内PLL时钟倍频器

- 16位I/Q速率高达266 MSPS

- 片内数字信号处理

- NCO和正交数字下变频器(QDDC)

- 可选抽取系数:12、16、24和32

- 支持自动增益控制(AGC)

- 片内衰减器范围为27 dB、步进为1 dB

- 通过可配置AGC数据端口实现衰减器快速控制

- 具有可编程阈值的峰值检测标志

- 单通道或多通道,支持JESD204B

- 低功耗:1.20 W

- 电源电压:1.1 V和2.5 V

- TDD省电高达60%

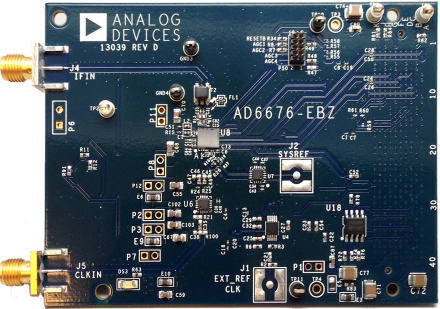

- 4.3 mm × 5.0 mm WLCSP

AD6676是一款高度集成的中频子系统,可数字化高达160 MHz的射频(RF)频段,并且此频段在70 MHz至450 MHz中频(IF)范围内为宽度居中。 与传统奈奎斯特IF采样ADC不同,AD6676依靠具有高过采样率的可调谐带通Σ-Δ型ADC,无需特定频段的IF SAW滤波器和增益级,极大简化宽带无线电接收机架构。 片内正交数字下变频后接可选抽取滤波器,可将复数的数据速率降低至62.5 MSPS至266.7 MSPS范围内便于管理的速率。 16位复数输出数据通过单通道或双通道JESD204B接口传输至主机,支持的线路速率高达5.333 Gbps。

应用

- 多模、宽带蜂窝基础设施设备

- 点对点微波设备

- 仪器仪表

- 频谱分析仪和通信分析仪

- 软件定义无线电

如需获取少量样片,请联系 highspeed.converters@analog.com。

参考资料

数据手册 1

用户手册 1

技术文章 4

信息 1

视频 6

器件驱动器 2

FPGA 互操作性报告 2

ADI 始终高度重视提供符合最高质量和可靠性水平的产品。我们通过将质量和可靠性检查纳入产品和工艺设计的各个范围以及制造过程来实现这一目标。出货产品的“零缺陷”始终是我们的目标。查看我们的质量和可靠性计划和认证以了解更多信息。

| 产品型号 | 引脚/封装图-中文版 | 文档 | CAD 符号,脚注和 3D模型 |

|---|---|---|---|

| AD6676BCBZRL | 80-Ball WLCSP (4.29mm x 5.04mm) |

| 产品型号 | 产品生命周期 | PCN |

|---|---|---|

|

3月 13, 2018 - 18_0042 AD6676 Assembly Bumping Site Transfer from Amkor to TSMC |

||

| AD6676BCBZRL | 量产 | |

这是最新版本的数据手册

软件资源

Evaluation Software 2

JESD204x Frame Mapping Table Generator

The JESD204x Frame Mapping Table Generator tool consists of two Windows executables that will allow the user to input any valid combination of JESD204x parameters (L, M, F, S, NP) in order to output a .csv file that illustrates the frame mapping of the JESD204x mode in table format. There is an executable that allows the user to input a single JESD204x mode and another, that allows the user to input the parameters for multiple JESD204x modes in a specified .csv format in order to output a .csv file that illustrates the frame mapping of each of the JESD204x modes that were input into separate tables.

JESD204接口框架

Integrated JESD204 software framework for rapid system-level development and optimization

找不到您所需的软件或驱动?

硬件生态系统

| 部分模型 | 产品周期 | 描述 |

|---|---|---|

| 单/双/三平衡混频器 1 | ||

| ADL5801 | 推荐用于新设计 | 高IP3、10 MHz 至6 GHz 有源混频器 |

| 集成LO的RF混频器 1 | ||

| ADRF6620 | 过期 | 700 MHz 至 2700 MHz接收混频器,集成IF DGA、小数N分频PLL和VCO |

| 小数N分频PLL 1 | ||

| ADF4355-2 | 推荐用于新设计 | 集成VCO的宽带频率合成器 |

| 增益模块 2 | ||

| ADL5541 | 量产 | 射频/中频( RF/IF)增益模块,工作频率50 MHz 至6 GHz ,增益15 dB |

| ADL5542 | 量产 | 20dB固定增益、50 MHz到6 GHz RF/IF增益模块 |

| 正线性稳压器(LDO) 2 | ||

| ADP223 | 推荐用于新设计 | 双通道、300 mA 可调输出、低噪声、高PSRR电压调节器 |

| ADP1752 | 量产 | 800MA低VIN LDO稳压器 |

工具及仿真模型

ADC Companion Transport Layer RTL Code Generator Tool

This command line executable tool generates a Verilog module which implements the JESD204 receive transport layer. The user specifies in a configuration file one or more modes to be supported by the transport layer module. These modes are defined as a set of JESD204 parameter values: L, M, F, S, N', and CF. The transport layer converts JESD204 lane data output from a JESD204 link layer IP to a data bus with a fixed width, containing interleaved virtual converter samples. Both JESD204B and JESD204C link layers are supported.

打开工具AD6676 AMI Model

打开工具评估套件

最新评论

需要发起讨论吗? 没有关于 AD6676的相关讨论?是否需要发起讨论?

在EngineerZone®上发起讨论