概要

アナログ・デバイセズは、位相ノイズ性能に優れる高速D/Aコンバータ(DAC)を提供しています。それらの製品を利用すれば、位相ノイズが小さく、高速周波数ホッピングが可能なRF/マイクロ波対応の次世代アジャイル・シンセサイザを実現できます。しかも、サイズ、重量、消費電力、性能、コストの面で優位性を得ることが可能です。但し、そうしたDACの能力を引き出すには、固定周波数のサンプリング・クロックを使用する場合のSSB(Single Side Band)位相ノイズを十分に低く抑えなければなりません。具体的には、広帯域に対応する一般的な電圧制御発振器(VCO)/フェーズ・ロック・ループ(PLL)の能力を上回るレベルを達成する必要があります。そこで、本稿では、アナログ位相検出器(PD:Phase Detector)を使用することにより、位相/周波数検出器(PFD:Phase/Frequency Detector)を使用するシンセサイザと比べてループ内の位相ノイズ性能を10dB~20dB高める手法を提案します。位相ノイズに関する最も厳しいシステム要件を満たすためには、アナログPLLを使用して誘電体共振発振器(DRO:Dielectric Resonator Oscillator)をロックし、固定周波数のクロックを生成する方法が推奨されます。それとは異なる一般的な実装例としては、MMICとして提供されている市販のVCOが挙げられます。本稿では、DACをベースとして粗調/微調ミキサーの機能を実現したマイクロ波対応のシンセサイザがもたらすメリットについて説明します。また、本稿の読者が実験による確認を行えるように、ブロック図や位相ノイズの測定結果、アプリケーション回路なども紹介します。

はじめに

航空宇宙/防衛(ADEF)の分野では、位相ノイズが重要な問題になります。例えば、レーダー、電子戦(EW:Electronic Warfare)などを含む多くのアプリケーションでは、高速ホッピングに対応する周波数シンセサイザとエキサイタに対しては、クラス最高レベルの位相ノイズ性能が求められます。多くの場合、レーダーのクラッタ減衰をはじめとする重要なシステム性能は、それらの周波数機能ブロックによって決まるからです。それらのブロックは、周波数変換、チューナ、変調といったより大きな機能ブロックで使用されます。アナログ・デバイセズが提供する最新世代の高速DACでは、位相ノイズが極めて小さく抑えられています。その性能は、周波数合成用のアジャイルなアーキテクチャを簡素化するという長年の夢に手が届くレベルに達しました。DACをベースとする周波数合成器への移行を進めれば、サイズが大きく高価な従来のシグナル・チェーンを改善できます。すなわち、SWaP-C(サイズ、重量、消費電力、コスト)がはるかに小さいソリューションを実現することが可能になります。但し、そうしたDACの位相ノイズ性能を引き出すには、サンプリング・クロックを供給するための信号源についても改善が必要になります。すなわち、従来の方式の信号源では不十分だということです。本稿では、DACの位相ノイズ性能を引き出すために、サンプリング・クロックの位相ノイズに関して考慮すべき事柄やトレードオフについて説明します。また、KuバンドからKaバンドの範囲で高速周波数ホッピングに対応可能なシンセサイザにおいて、位相ノイズを抑えるための実装方法について検討します。更に、設計者が本稿の内容を実験で再現し、本稿で示すアプローチを設計に適用できるようにするために、アプリケーション回路のブロック図や測定結果なども紹介します。

レーダー/EWにおけるSSB位相ノイズの影響

ADEF分野のアプリケーションでは、検出されたくないと考えている敵の目標物からの小さな信号や反射信号をセンシング・システムによって検出する必要があります。つまり、過酷な電磁環境において、タイム・クリティカルな方法での傍受を実現しなければなりません。一般的な性能指標としては、瞬時スプリアスフリー・ダイナミック・レンジ(SFDR)が使用されます。これは、大きなブロッカが存在する状態で、受信システムが小さな信号をどのくらい検出できるのかということを表します。SFDRは、IMD2(2次相互変調歪)またはIMD3(3次相互変調歪)とノイズ・フロアで表現されます。その際、ノイズ・フロアは一様なものであると想定されます。つまり、周波数オフセットに対する依存性によって式が複雑になりすぎないように、キャリアの位相ノイズのショルダ形状の部分(以下、ショルダ)から十分に離れている(オフセットしている)と見なすということです。この仮定は、例えばキャリアから10MHzほど外側であれば許容できます。しかし、レーダーやEWのアプリケーションは、10MHzのオフセット領域内において、キャリアのより近い位置で動作する必要があります。そのため、キャリアのノイズのショルダに埋もれることなく、送信キャリアの近くまでダイナミック・レンジを維持できるかどうかということが、SFDRでは明確には捕捉できない重要な側面になります。このノイズのショルダがSSB位相ノイズです。SSB位相ノイズは、キャリアからの周波数オフセットの関数L(f)として表すことができます。

通信システムや衛星通信システムでは、積分RMSジッタの値を重視するケースがあります。つまり、位相ノイズのショルダに含まれるすべてのノイズを、対象となるオフセット範囲にわたって積分した値に注目するということです。ただ、ほとんどのレーダー/EWシステムでは、キャリアからの特定の周波数オフセット位置におけるスポットのSSB位相ノイズのエンベロープを重視します。通常、その数値は可能な限り低く抑えられていなければなりません。1kHz~1MHzの範囲のドップラー・オフセットでは、特にそのことが重要になります。多くの場合、シンセサイザの設計における課題は、この重要な領域においてはPLLのノイズ構成と関連して位相ノイズが高いプラトー(plateau)になっているということです。本稿の目的は、この領域におけるノイズの影響を最小限に抑える方法を示すことです。

ほとんどのレーダー/EWシステムでは、DACに供給するサンプリング・クロックのSSB位相ノイズを、DACの付加ノイズのカーブより10dBほど小さく抑えることが理想になります。それにより、クロックではなくDACによってシステムの位相ノイズのノイズ・フロアが決まるようになるということを覚えておいてください。但し、実際にこのような条件を満たすのは非常に困難です。アナログ・デバイセズのDACでは、非常に優れた位相ノイズ性能が得られます。その潜在能力は、DACをベースとするシンセサイザを構築する上で非常に革新的なレベルにあると言えます。

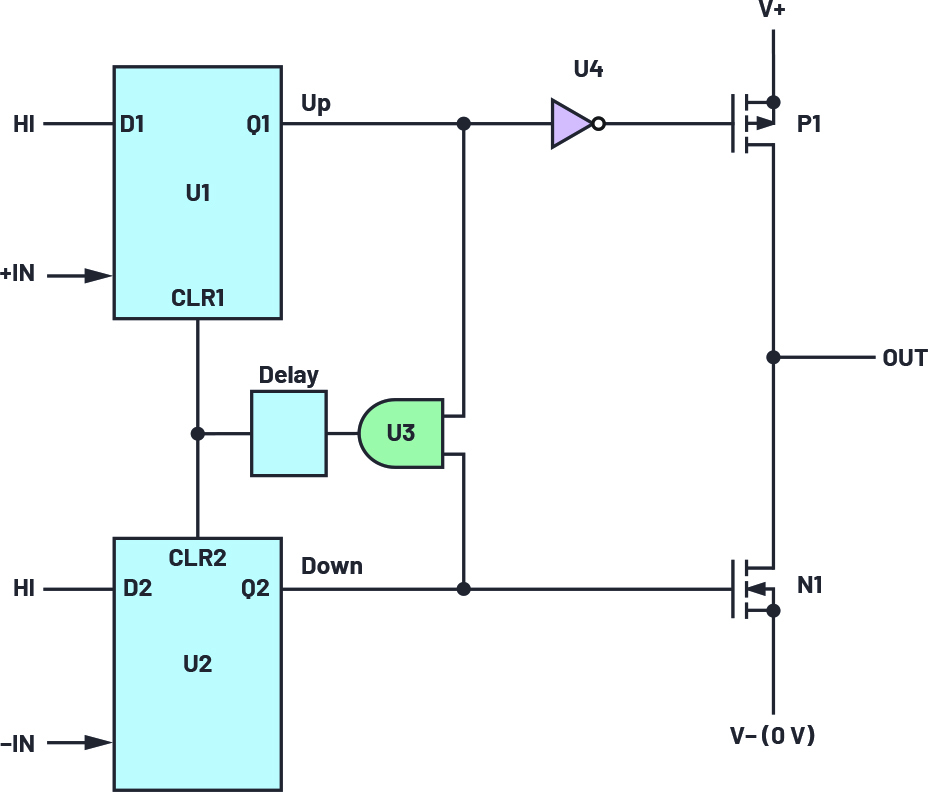

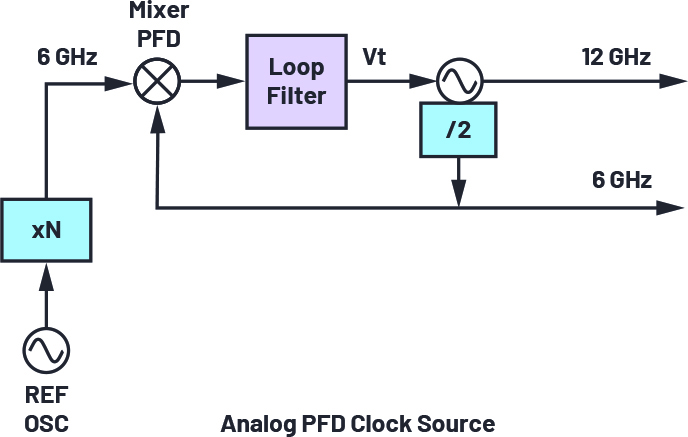

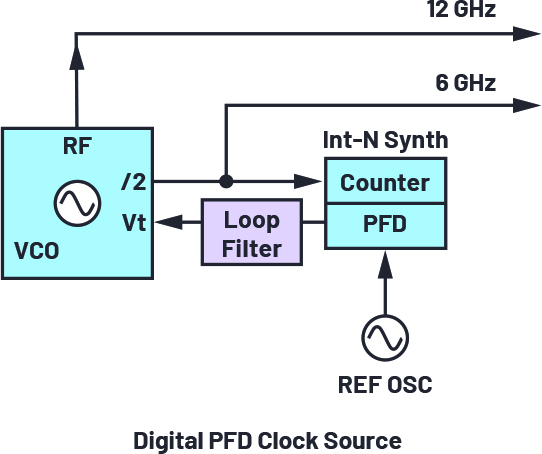

本稿では、DPLL(デジタルPLL)という用語を次のような意味で使用します。すなわち、アクティブなPFDと周波数分周器を組み合わせたPLL ICまたはシンセサイザICのことを指します。図1に、従来型のデジタルPFDの回路構成を示しました。一方、本稿では、PDとしてパッシブ・ミキサーを採用しているものをAPLL(アナログPLL)と呼ぶことにします。

図1. 従来型のデジタルPFD

誤解のないように説明しておきますが、SSB位相ノイズが適切かどうかは、特定の要件やユース・ケースに応じて異なります。広帯域に対応するPLL/VCOシンセサイザMMICを採用すれば、マルチオクターブにわたるマイクロ波のチューニング、プログラマビリティ、使いやすさ、SWaP-Cを低減できるといったメリットを享受できます。ここでは、広帯域に対応する同調型シンセサイザのアプリケーションの大部分は対象にしていません。そうしたアプリケーションには、アナログ・デバイセズが提供するPLL/VCOシンセサイザICが最適です。本稿では、DACに供給する固定周波数のサンプリング・クロックという特定のユース・ケースだけを対象にして検討を進めます。例えば、後ほど示す表1は、この特定のユース・ケースに関する性能を比較することを意図して作成したものです。この点には注意してください。

従来とは何が異なるのか?

従来、DACをベースとする周波数合成器を実IFで実装する際には、DACの比較的低いサンプリング・レート(100MSPS程度)と低いアナログ周波数帯域幅(250MHz程度)が障壁になっていました。旧来のDACを使用する場合、IFが低いのでアップコンバージョンの実施が困難でした。また、RFフィルタのサイズが大きくなってしまうなど、実現が不可能になるケースも存在しました。もう1つの選択肢としては、周波数逓倍を利用する方法が考えられます。しかし、その方法では、必要な逓倍率Nが大きい場合、DACの付加位相ノイズLDAC(f)がノイズ・フロアに対して高くなりすぎ、実用的ではありません。例えば、周波数F1から同F2にアップコンバートする場合、コヒーレントな周波数変換の影響は次式で表されます。

アナログ・デバイセズのDACの場合、よりサンプリング・レートが低い既存の製品であれば、付加位相ノイズ性能は非常に優れていました。ただ、SWaP-Cを低く抑えつつ、マイクロ波の帯域に変換するには、直接キャリア周波数が低すぎるということになります。

しかし、現在ではそのような状況は一変しました。DACのサンプリング・レート、アナログ帯域幅、その結果としての直接実IF周波数に対する能力は、数GHzのレベルにまで達したのです。しかも、付加位相ノイズLDAC(f)は優れた値に維持されているので、遂に汎用性の高いビルディング・ブロックが得られたことになります。このような高性能のDACは、SWaPを低く抑えつつ、広帯域にわたりマイクロ波の高速チューニングを可能にする周波数シンセサイザを実現するための新たな選択肢になります。

高速DACをベースとする広帯域対応のマイクロ波シンセサイザ

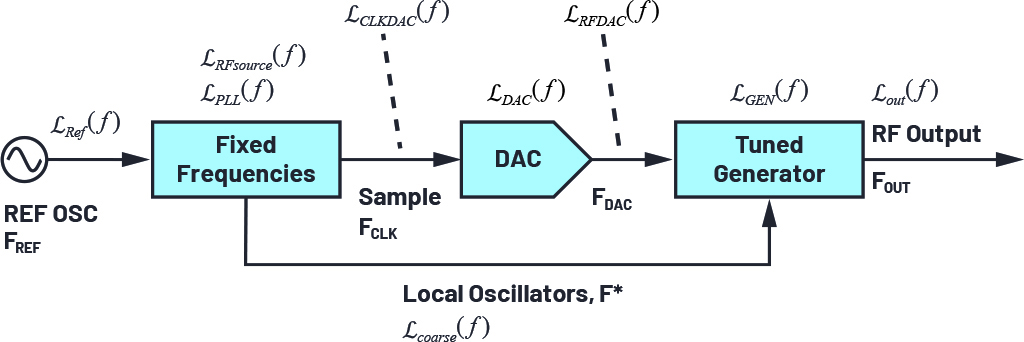

図2に示したのが、本稿で扱うDACをベースとしたシンセサイザの基本構成です。各機能ブロックにおいてキャリアからのオフセットが異なると、全体の位相ノイズに及ぶ影響にも少し違いが生じます。ここでの論点は、DACの小さな付加位相ノイズ(残留位相ノイズとも呼びます)LDAC(f)によってシステムの位相ノイズが決まるよう、いかに各ブロックを設計するのかということです。以下に説明するように、それは簡単なことではありません。

- LDAC(f) は、デバイスの 1/f ノイズ、あるいはシャッフル・モードのような実装方式など、複数の要因によって生成されます。電源の位相ノイズが増加すると大きな悪影響が及ぶので、低ノイズの LDO(低ドロップアウト)レギュレータを慎重に実装することが非常に重要になります。

- リファレンス発振器 FREF は、シンセサイザをロックするシステムの位相リファレンス信号です。多くの場合、100MHz 程度の周波数が使用されます。信号源の絶対位相ノイズLREF(f)は、最もオフセットが小さい場合(通常 1kHz 未満)のシンセサイザの位相ノイズを決める要素です。システムにおいては、リファレンスの位相ノイズ性能、周波数、SWaP-C のトレードオフによりバランスをとることが重要になります。リファレンスの位相ノイズが適切でない場合、下流で位相ノイズ性能を挽回するのは不可能であるか非常に困難です。したがって、リファレンス・クロックについては最大限の配慮が必要になります。

- 固定周波数(Fixed Frequencies)のブロックには、ローカルの VCO(RF 信号源)を周波数リファレンスにロックするための PLL が配置されています。RF 信号源の絶対位相ノイズLRFsource(f) の選択は、SWaP-C と同様のトレードオフ要因になります。それよって、オフセットが大きい位置での位相ノイズが決まり、ショルダのレベルがノイズ・フロアのレベルと適合します。PLL を採用していることから、付加位相ノイズの 1 つの要因である LPLL(f) が生じます。それによって、非常に重要な中間オフセットのプラトー(通常は 1kHz ~ 1MHz)における位相ノイズが決まります。PLL のアクティブ・ループ・フィルタにはオペアンプを使用します。オペアンプには、考慮すべき重要なノイズ要因が存在するので、この項目に含めて検討する必要があります。この中間オフセットの SSB 位相ノイズの領域は、LRFDAC(f) に最大の影響を及ぼします。多くの場合、シンセサイザが用途に適合するかどうかを左右するものだと言えます。本稿では、DAC の位相ノイズ LDAC(f) によってLRFDAC(f) が決まるようにするために、サンプリング・クロックの位相ノイズ LCLKDAC(f) を最小限に抑えることに焦点を絞ります。

- 同調型発生器(Tuned Generator)のブロックは、DAC のRF 出力と、絶対位相ノイズ Lcoarse(f) を含む一連の固定周波数とをミキシングし、広帯域に対応するアジャイルな RF 出力にアップコンバートするためのものです。これにより、付加位相ノイズ LGEN(f) が生じます。本稿では、DAC の出力を取得し、それをより高いマイクロ波帯に変換する必要がある場合に、位相ノイズ Lout(f) とスプリアスを最小限に抑える手法に焦点を絞ります。

図2. 広帯域に対応するDACベースの周波数合成器。位相ノイズの要因も示しています。

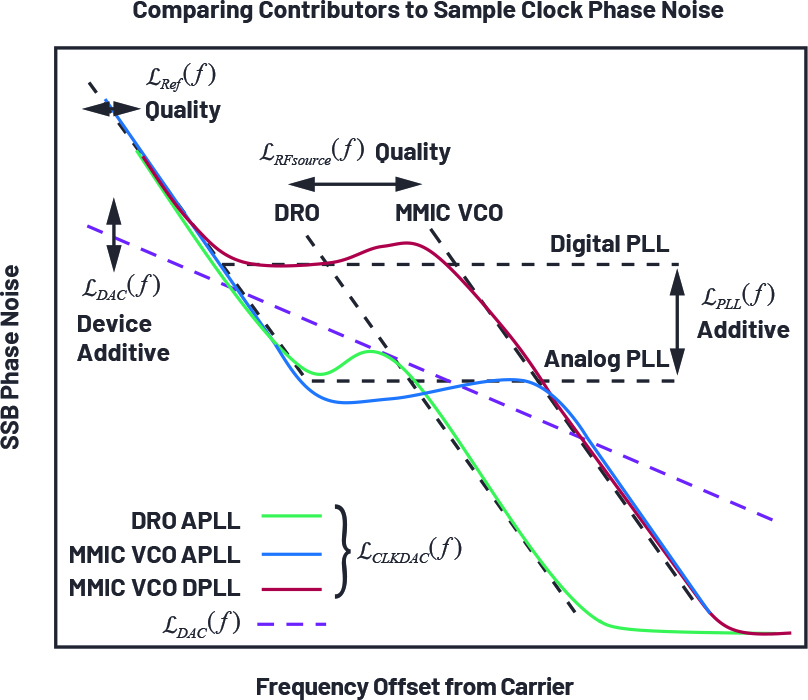

図3. DACのクロック信号源の位相ノイズに影響を及ぼす要因

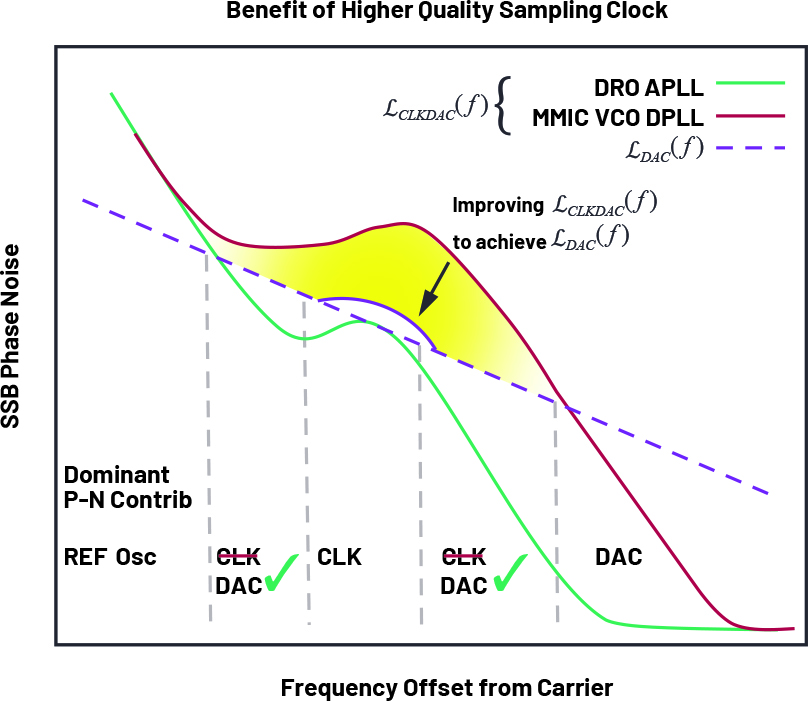

図4. サンプリング・クロックの位相ノイズを抑えなければならない理由

図2、図3、図4に位相ノイズに関する情報をまとめました。これらを吟味すると、以下のようなことがわかります。

- 重要なのは、LCLKDAC(f) の影響を可能な限り抑え、LDAC(f) によって LRFDAC(f) が決まるようにすることです。

- Lout(f < 1kHz) は、LREF(f < 1kHz) + 20LogN です。ここで、N は最終的な周波数とリファレンス周波数の比を表します。

- LCLKDAC(f > 1kHz) は、LRFsource(f) と LPLL(f) に関わる実装方法に大きく依存します。LREF(f) のノイズ・フロアの影響も及びます。

- Lout(f > 1kHz) は、上記の要因に加え、LRFDAC(f > 1kHz) に関わるアップコンバート方法の選択にも依存します。Lcoarse(f < 1kHz) に関連する方法を選択することが推奨されます。

新たなDACがもたらすメリット、クロック供給の新たな課題

筆者の同僚は、SWaP-Cの低減を進めるために従来のシグナル・チェーンの改良に取り組んでいます。その際、その同僚は「悲しみの保存」という自然法則に直面すると述べています。DACをベースとする同調型周波数合成器の機能ブロックを実現するためには、従来のSWaP-Cのうちごく一部しか必要としません。つまり悲しみの保存の法則で言えば、悲しみが減少することになります。一方で、固定周波数の信号源については微妙な状況にあり、悲しみは増加してしまいます。DACの付加位相ノイズは非常に小さく(良いことです)、サンプリング・クロックもかなり高い12GSPSを使用できます(これも良いことです。合理的なフィルタ処理が可能な実IFを使用できます)。ただ、結果として、サンプリング・クロックの信号源に必要なSSB位相ノイズの削減に向けて、より複雑なクロック信号源の実装方法を検討しなければなりません。つまり、VCO/PLL MMICでは、DACの付加位相ノイズ性能を引き出すには十分ではないということです。

まず、図2のリファレンス発振器、固定周波数ブロック、DACの相互作用について検討しましょう。固定周波数ブロックは、PLLを構成するVCOから成ります。そのPLLは、リファレンス発振器に対してRF信号源をロックする役割を果たします。その構成要素は、周波数分周器(または周波数変換器)、PFD、オペアンプを使用したアクティブ・ループ・フィルタです。

表1は、DACのクロック信号源として使用する3つの異なる実装方法を比較したものです。

| 種類 | RF発振器 | PD/PFD | SSB位相ノイズ | SWaP-C |

使いやすさ |

| MMIC VCO DPLL | MMIC VCO | アクティブPFD | 良好 | 最良 | 最良 |

| MMIC VCO APLL | MMIC VCO | パッシブ・ミキサーPD | より良好 | より良好 | 不十分 |

| DRO APLL | DRO | パッシブ・ミキサーPD | 最良 | 不十分 | 不十分 |

古いものが再び新しく

アナログPDの歴史は非常に古く、アクティブPFDを採用した現在のシンセサイザICの祖先に相当します。いまでは、広帯域に対応する最新のシンセサイザ・アプリケーションが圧倒的多数を占める状況にあります。そうした中で、アナログPDは時代遅れなものになっている感があります。当然のことながら、シンセサイザICの方が著しい進歩を見せています。SWaP-Cに優れ、広帯域に対応する同調型VCO/PLLが必要な場合、アナログPDは適切な選択肢だとは言えません。では、本稿で取り上げているDAC用のクロックを生成するためのものとして、なぜアナログPDを選択するのでしょうか。その理由は、アナログPD(パッシブPD)の付加位相ノイズ性能が優れているからです。PDは、2つの入力周波数を比較し、その位相差を表すビート信号を出力します。比較する周波数が直交である場合、あるいはロックしている場合、PDから出力されるのは0VのDC信号です。多くの場合、アクティブPFDを使用するインテジャーN型(整数分周型)のシンセサイザやフラクショナルN型(少数分周型)のシンセサイザでは、比較の対象となる2つの入力信号の最高周波数は100MHz~500MHz程度です。「HMC698ファミリ」のようなPFD/シンセサイザICは、1.3GHzまでの入力信号で動作します。DC的な消費電力が多くなるという代償は伴いますが、位相ノイズの面では有利です。最も重要なのは、アクティブPFDの場合、実装に大きく依存して付加1/fノイズが生成されるということです。つまり、どの製品を使用しても同じノイズ性能が得られるというわけではありません。そのため、ここでは、1/fノイズが非常に小さいPFDとして「HMC440」を選択することにします。また、PDは可能な限り高い周波数で動作させるという経験則に従うこととします。そうすると、ループ内のPDの周波数をRF出力周波数に変換する際、PDの付加位相ノイズのプラトーが理論上20LogN増加するのを抑えることができます。アクティブ周波数分周器からのノイズを回避しつつ、可能な限り高いPFD周波数を実現するために、変換ループとしては「ADF4401A」のような製品を使用します。

図5. APLLのブロック図

図6. DPLLのブロック図

例として、付加ノイズが-153dBc/HzのPFDを使って位相をロックした10GHzのRF出力信号を得るケースについて考えてみましょう。ここでは、話を簡素化するために、ループ内の支配的なノイズ要因はPFDであると仮定します(実際には必ずしもそうではありません)。仮に、PFDを10MHzで動作させたとすると、帯域内の位相ノイズ(つまりプラトー)は次式で与えられます。

全く同じシナリオで、周波数が10倍高い100MHzでPFDを動作させたとします。その場合、ループ内の位相ノイズは次式で表される値まで改善します。

この20dBの改善は重要です。PFDには、常に可能な限り周波数の高いクロックを供給するべきだということがわかります。アナログ・ミキサーをベースとするPDを使用すると、以下に示す2つのメリットが得られます。

- パッシブ・ミキサーの付加ノイズは非常に小さく、多くの場合、無視することができます。オペアンプによるアクティブ・ループ・フィルタのノイズは、ループ内の限定的なノイズ要因として表に現れます。

- 比較する周波数は、必要に応じて高くすることができるので(多くの場合、数 GHz まで)、ループ内のコンポーネントの残留ノイズとの間でバランスを取ることが可能です。一般に、周波数が高くなるほど、残留ノイズが十分に小さい RF アンプの選択肢は少なくなります。

まとめると、PDの付加ノイズと周波数分周器の帯域内の付加ノイズが、リファレンスの逓倍信号の絶対位相ノイズを下回るように、パッシブPDの周波数は十分に高く設定するべきです。とはいえ、RFアンプの残留ノイズが性能を低下させるレベルまで高くしないように配慮しなければなりません。RFアンプはいくつか必要になります。

RFアンプの残留位相ノイズは、それ自体が1つのテーマになり得ます。プロセス技術だけでなく、ノードや回路のアーキテクチャもその大きな要因になります。一般に、シリコン・ベースのBJT(Bipolar Junction Transistor)の性能が最高ですが、周波数範囲に限界があります(1GHz未満)。その次に性能が高いのはGaAsベースのHBT(Heterojunction Bipolar Transistor)です。この種のデバイスの中には、Kuバンドまで対応できるものも存在します。例えば「ADL8150」、「HMC606LC5」、「HMC3653」、「HMC3587」といった製品です。

pHEMT(Pseudomorphic High Electron Mobility Transistor)アンプは高い周波数で広く使用できます。但し、残留位相ノイズが大きく変化するので注意が必要です。一般に、pHEMTデバイスの位相ノイズは大きくはありませんが、温度に依存して変化が現れる可能性があります。

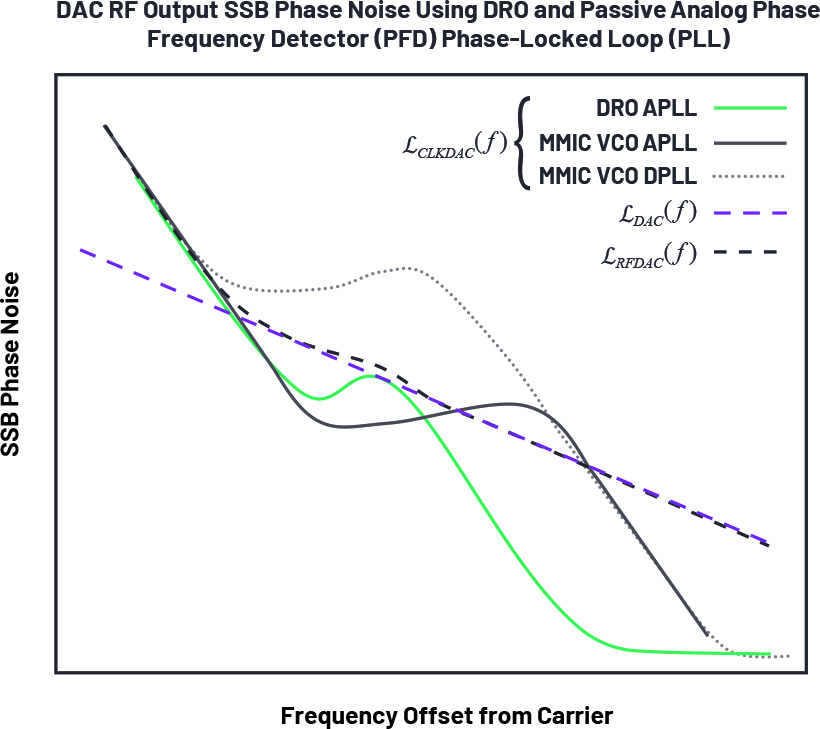

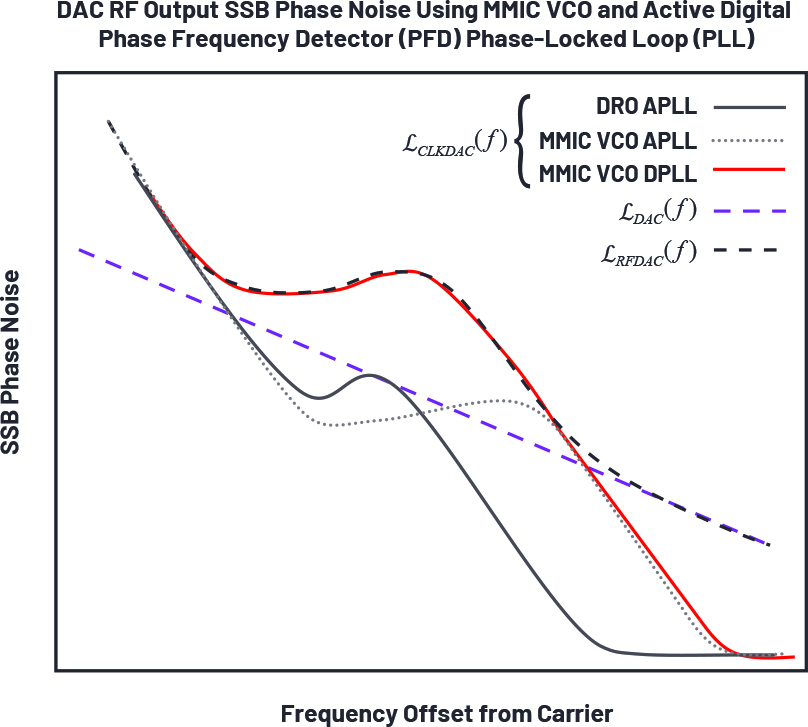

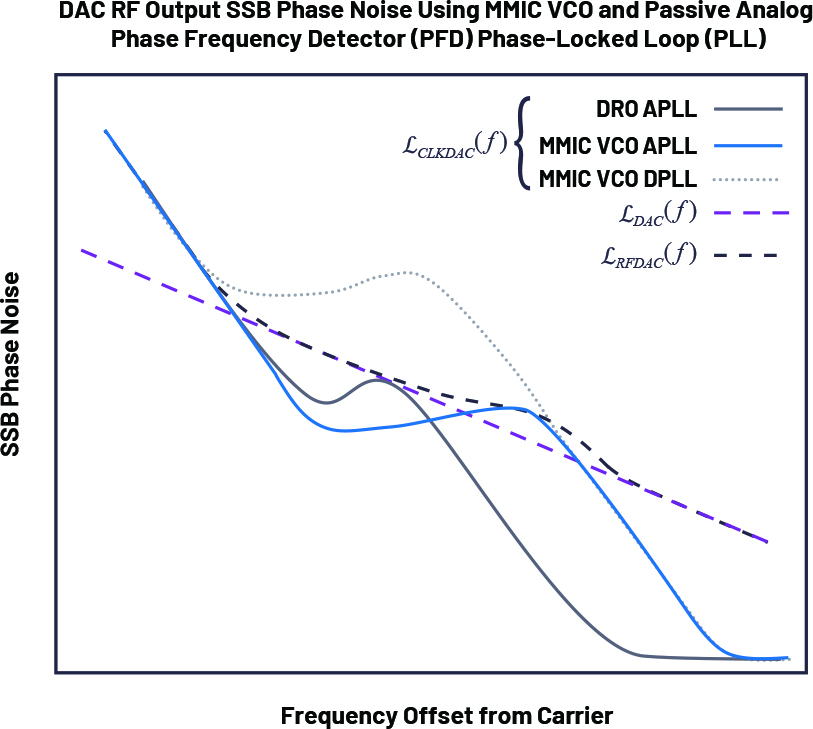

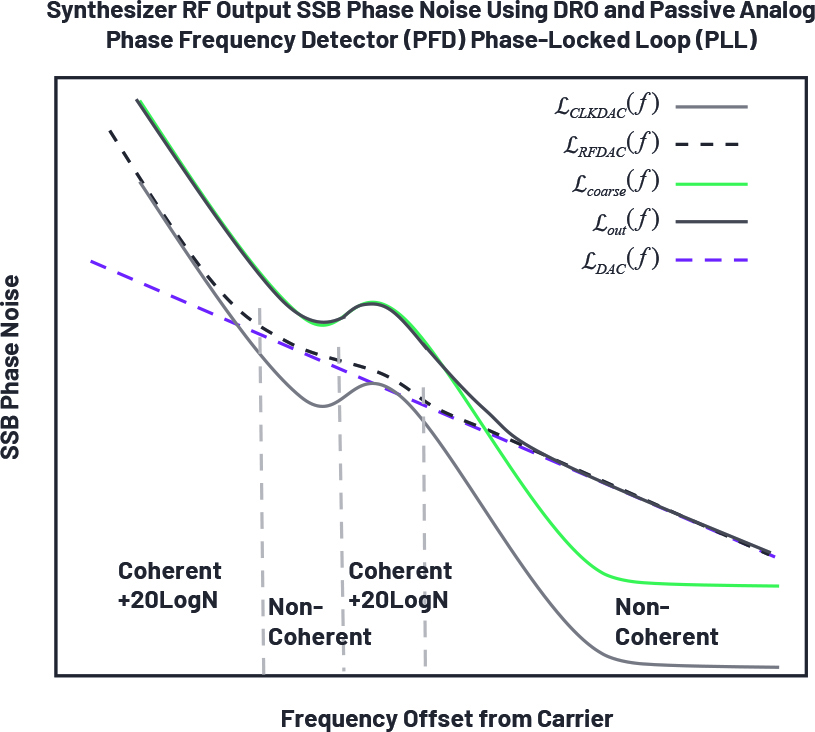

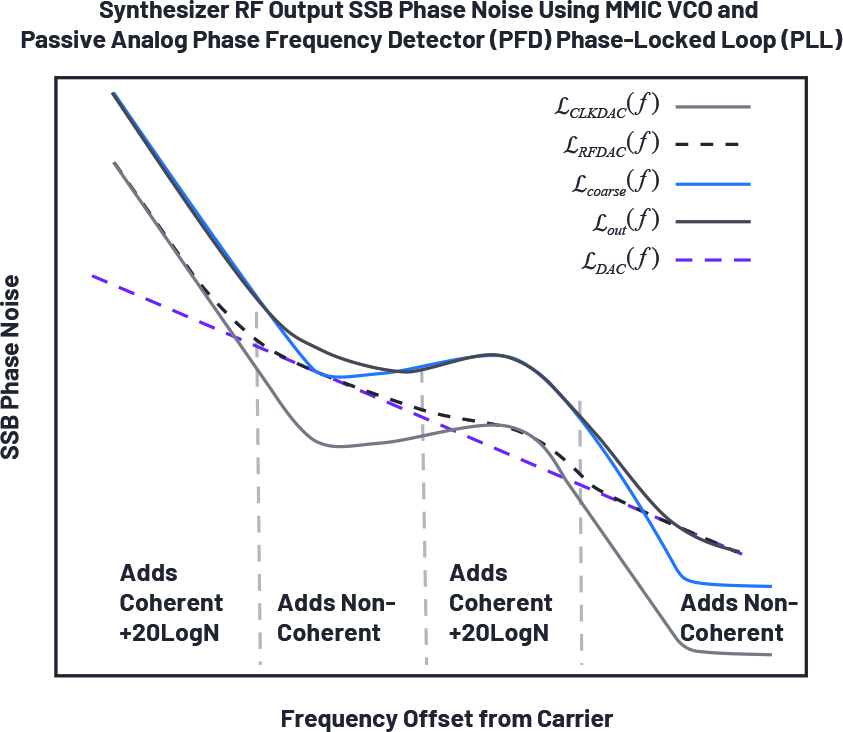

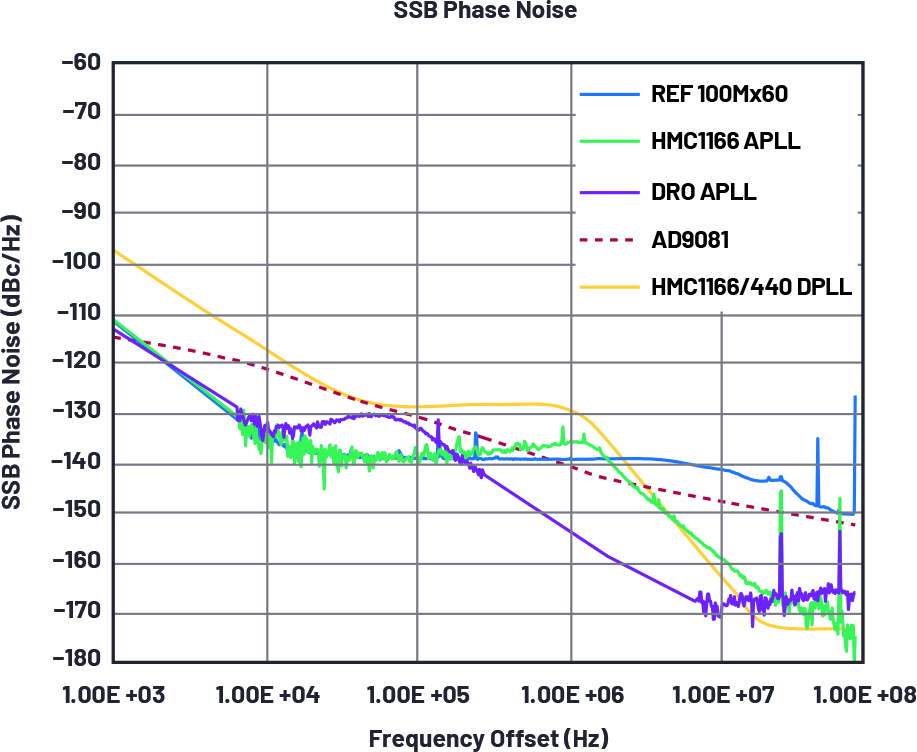

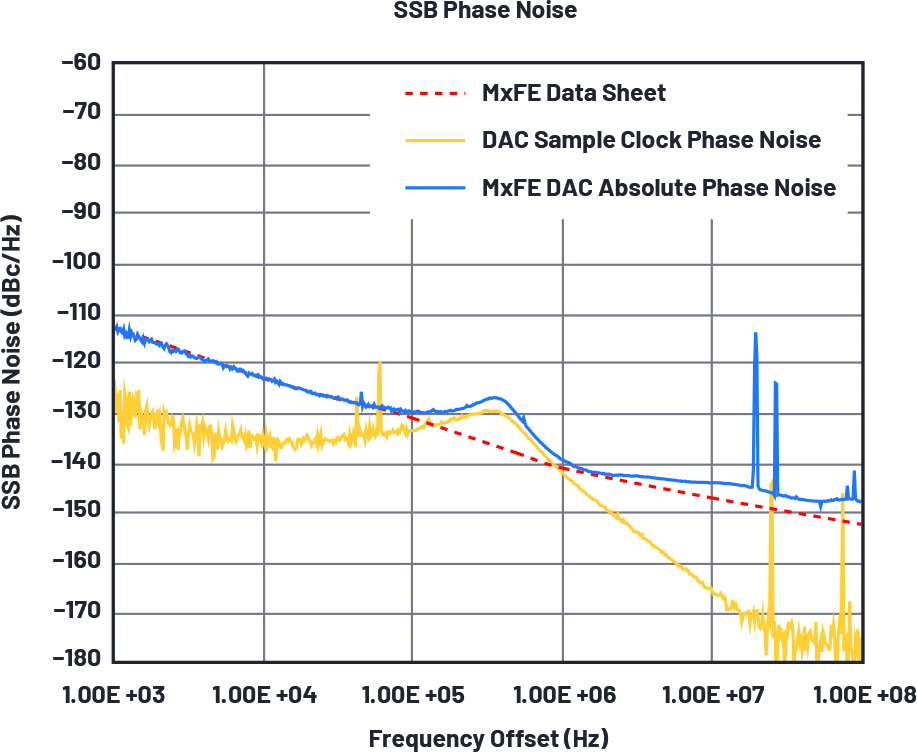

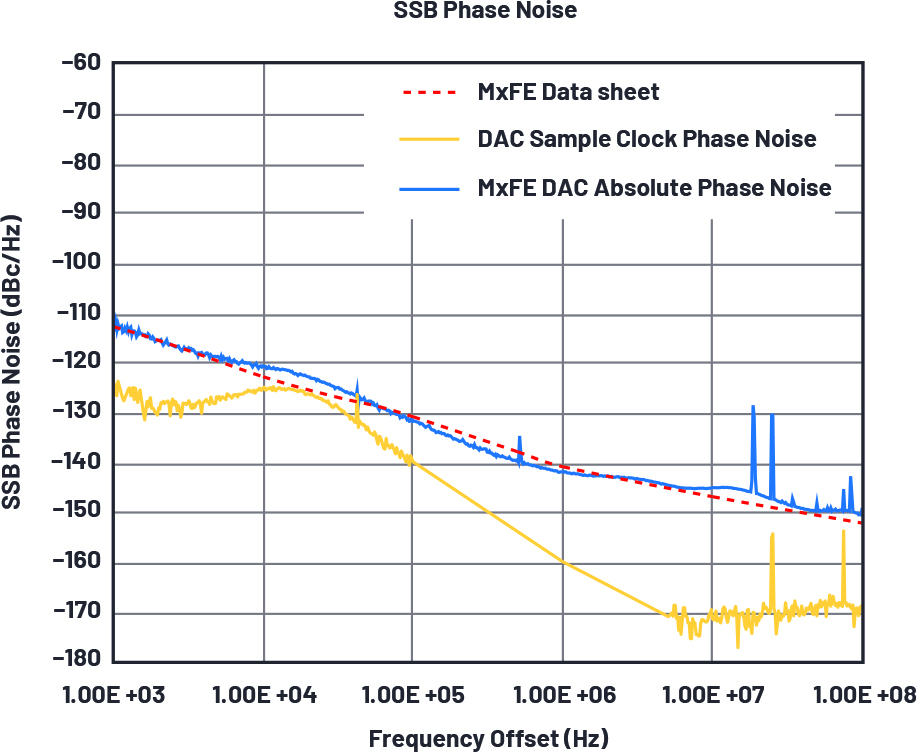

前掲の表1では、クロック信号源の3種類の実装方法についてまとめました。それぞれの実装によって得られるDACの出力信号の位相ノイズLRFDAC(f)を図7~図10に示しました(位相ノイズの測定結果を後ほど図18~図20として示します)。図7を見ると、高性能のDROとAPLLの組み合わせ(DRO APLL)では、狭い領域内でDACの残留ノイズが接近して生じています。ただ、DACのノイズよりは小さいので、それらはほぼ表には現れないと考えられます。結果として、従来のMMIC VCO DPLLを使用してサンプリング・クロックを供給する場合(図8)よりも、はるかに優れた性能が実現されています。MMIC VCO DPLLのノイズは、非常に広いオフセット範囲に対して支配的になります。そのため、DACの位相ノイズ性能が無駄になるとも言えます。ただ、そのSWaP-Cは最も優れていますし、使いやすいものであることは間違いありません。SWaP-Cと性能のバランスが最も良いのは、図9に示したMMIC VCO APLLかもしれません。DACの位相ノイズ性能は、重要なオフセット範囲で十分に維持されています。ただ、DROと比べた場合、MMIC VCOの位相ノイズは劣るので、オフセットが大きくなるにつれて性能が低下します。図10は、DACの付加位相ノイズに対して各クロック信号源の位相ノイズを重ね合わせたものです。

同じDROでも、製品によってSSB位相ノイズは大きく異なるということには注意が必要です。本稿の例では、ビー玉ほどの大きさで、SWaP-Cの小さいDROを選択しました。それ以外に、位相ノイズのカーブが完全にDACの残留ノイズより低くなる、より高性能なDROも存在します。ただ、DROの位相ノイズのレベルとSWaP-Cの間には、直接的な相関があります。つまり、たとえ性能が良くても、ビー玉よりはるかに大きく、価格が数千米ドルにも達することがあるということです。

図7. アナログPDでロックしたDROを使用した場合のDAC出力のSSB位相ノイズ

図8. デジタルPFDでロックしたMMIC VCOを使用した場合のDAC出力のSSB位相ノイズ

図9. アナログPDでロックしたMMIC VCOを使用した場合のDAC出力のSSB位相ノイズ

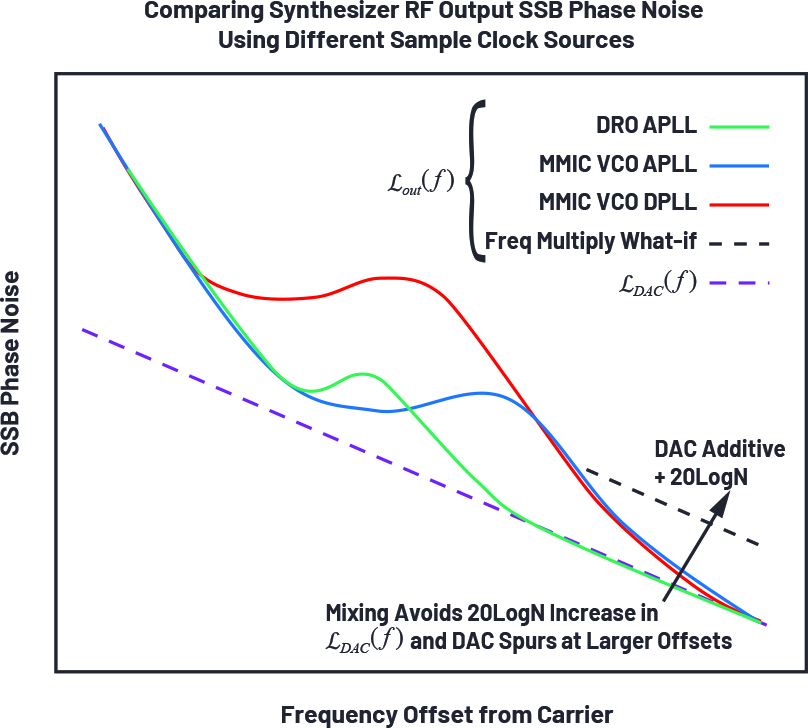

図10. 3種類の信号源の比較。それぞれを使用した場合のDAC出力のSSB位相ノイズを示しています。

マイクロ波シンセサイザの実装

ここまで、付加位相ノイズ性能に優れるDACにサンプリング・クロックを供給するための信号源について検討してきました。続いては、同調型の周波数合成器の実装について考察します。DACのサンプリング・クロックの周波数は、ナイキスト・ゾーン、瞬時帯域幅、データ・ペイロードといった多くの目標値に基づいて選択します。使用可能なサンプリング・クロックとその低調波、N次高調波、N分周波を基に、一連の固定周波数の信号を効率的に生成する方法については熟慮すべきです。そうした固定周波数の信号は、DACから出力される微調周波数のセットとミキシングした粗調周波数のセットとして生成します。

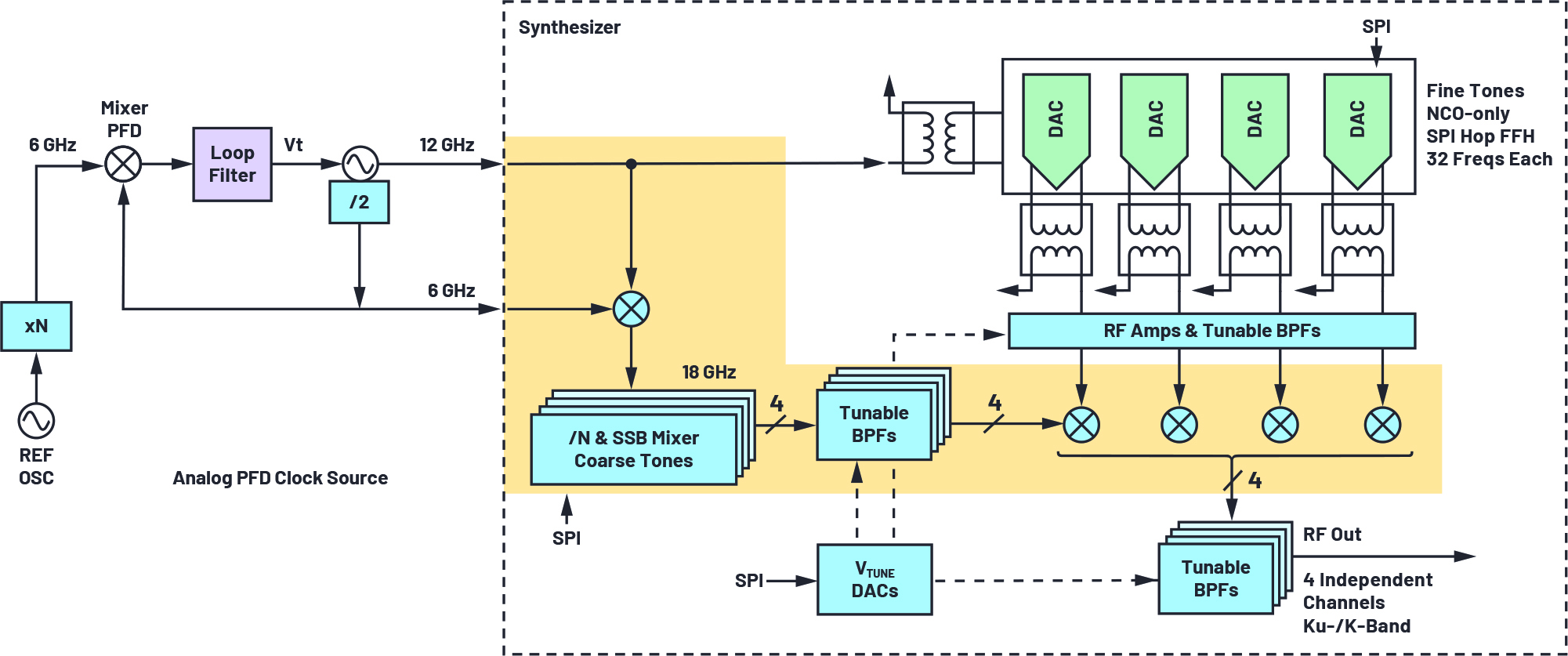

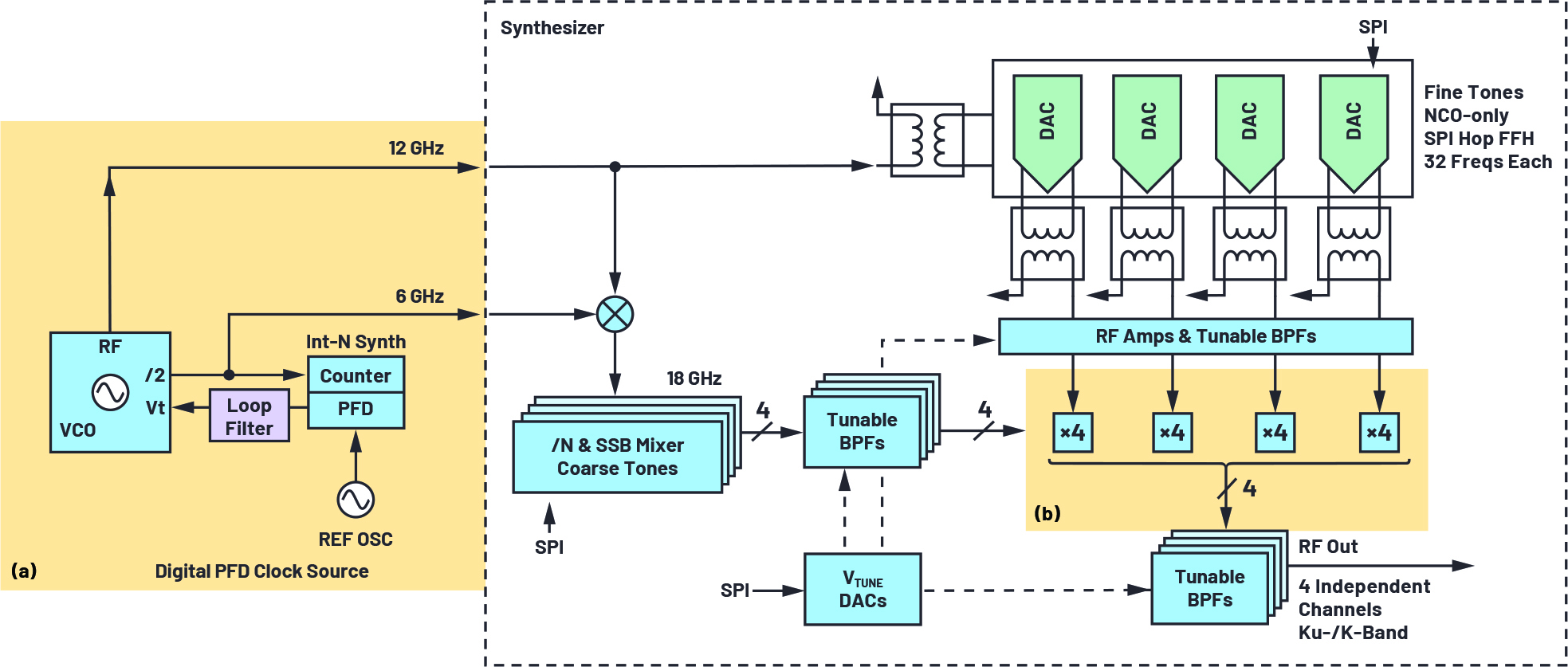

図11は、粗調/微調ミキシング方式を実現する回路のブロック図です。この例では、RF対応のDACを搭載するMxFE®「AD9081/AD9082」に対して、12GSPSのサンプリング・クロックを供給します。そのクロックは、VCOをベースとする信号源によって生成します。VCOからは、6GHz(RF/2)も出力することにします。これらの信号はDACへのクロック供給に必須であり、他の必要な信号を生成するためにも活用できます。そのため、これらの信号を粗調信号発生器の基準として使用するのは非常に理にかなっています。一連の粗調周波数は、SSBミキサー方式に向けて、プログラマブルな周波数分周器に18GHzを供給することによって生成します。これをDACの出力とミキシングすると、KuバンドとKバンドの大部分をカバーする周波数合成が可能になります。多くのミキシング・スプリアスとDACのスプリアスを減衰させるためには、チューナブルなバンドパス・フィルタ(BPF)が不可欠です。「ADV7125」のような高精度のDACにより、SPI(Serial Peripheral Interface)による制御信号を、チューナブルなフィルタを調整するための低ノイズのアナログ制御信号に変換します。

図11. DACベースの粗調/微調ミキサー・シンセサイザ。アナログPDをベースとする信号源を使用しています。

ここまでに説明したとおり、このミキシング方式は少し複雑です。より簡単な手法としては、ミキシングを行うのではなく、DACの出力を周波数逓倍するというものが考えられます。周波数逓倍はより容易な処理であり、SWaP-Cも抑えられるので魅力的な方法です。例えば、図11においてオレンジ色で網掛けをした機能ブロックは、図12(b)の逓倍器の機能ブロックで置き換えることができます。ただ、本稿では、この手法を主要な選択肢としては捉えていません。周波数逓倍には、20LogNで決まるDACのノイズ・フロアとDACのスプリアスが悪化するという問題があるからです。DACからのRF出力は、位相ノイズとスプリアスの面で優れた性質を備えています(通常、DACから発生する様々なスプリアスは、60dBcを十分に下回ります)。しかし、3GHz~6GHzのDACの出力をKuバンドの信号に変換するには、最低でも4逓倍しなければなりません。そうすると、DACのスプリアスと位相ノイズは12dB悪化します。それによって、DACのスプリアスとノイズが、目標とするレベルを外れてしまう可能性が高くなります。

図12. 図11の代替案。性能は低下します。(a)はデジタルPLL ICによってサンプリング・クロックを供給します。(b)は逓倍器ブロックです。

粗調/微調ミキサー方式では複雑さが増加します。しかし、DAC出力の逓倍を避けることができ、DACのスプリアスと位相ノイズは、アップコンバートされたRF出力を得るにあたり1:1で変換されます。12dB増加するのとは大きな差があるため、複雑さを許容する価値はあります。

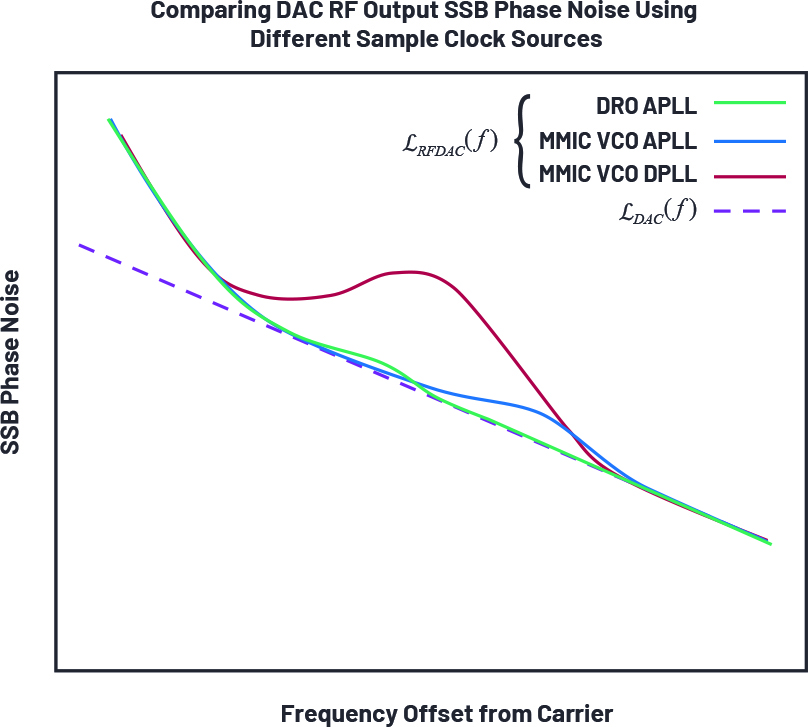

図13~図16をご覧ください。これらは、粗調と微調のSSB位相ノイズがどのように組み合わせられ、アップコンバートされたマイクロ波の周波数において最終的にどのようなSSB位相ノイズになるのかを表しています。また、位相ノイズの実測結果を図18~図20に示しました。周波数逓倍は、ある信号とそのコピーとをミキシングする処理だと言うことができます。同様に、様々な周波数のコヒーレントな信号をミキシングすると、位相ノイズには周波数逓倍の場合と同じように20LogNの影響が及びます。図13~図16では「コヒーレント」という注釈を付けたオフセット領域があります。それらの部分では、位相ノイズの面で、周波数逓倍方式に対し、ミキシングを使用することによるメリットは存在しないということです。灰色で示したサンプリング・クロックをより高い局部発振(LO)周波数にアップコンバートすると、位相ノイズのカーブ全体が20LogNの分だけ上方に移動します。粗調/微調ミキシングを利用する最大の動機は、位相ノイズのショルダがノイズ・フロアに接近するため、より大きなオフセット位置におけるメリットが得られることにあります。LOの粗調信号の位相ノイズは、そうしたオフセット位置におけるDACの付加ノイズよりもはるかに小さくなり、基本的に何の影響も生じません。単に、DACの位相ノイズが1:1で変換されてアップコンバートされたマイクロ波信号が得られるという状態になります。図16は、各実装方法による最終的なシンセサイザの位相ノイズを比較したものです。ミキシングによる方法では、離れたオフセット位置で周波数逓倍に対するメリットが得られることがわかります。

図13. アナログPDでロックしたDROを使用した場合のシンセサイザ出力のSSB位相ノイズ

図14. デジタルPFDでロックしたMMIC VCOを使用した場合のシンセサイザ出力のSSB位相ノイズ

図15. アナログPDでロックしたMMIC VCOを使用した場合のシンセサイザ出力のSSB位相ノイズ

図16. 3種類の信号源の比較。それぞれを使用した場合のシンセサイザ出力のSSB位相ノイズを示しています。

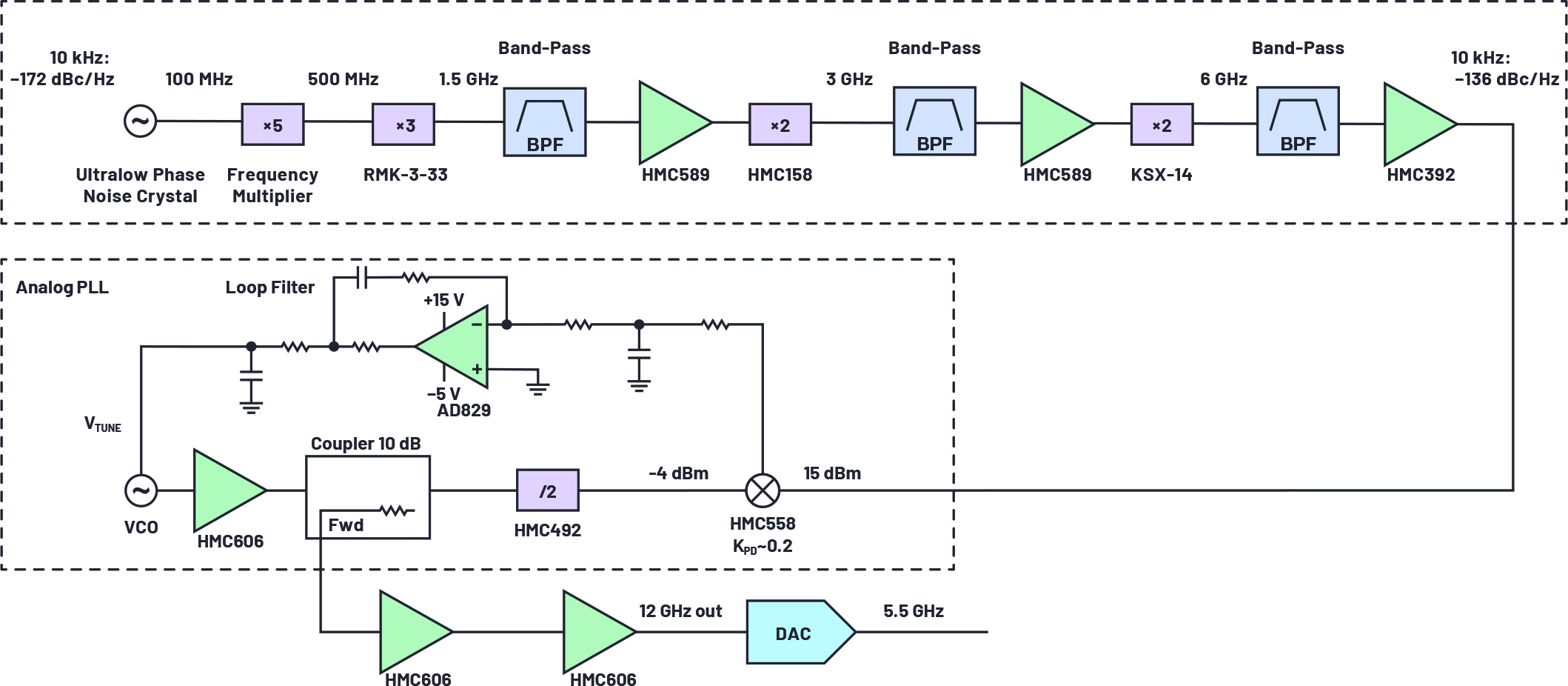

図17は、実測に使用した回路のブロック図です。このような構成により、SSB位相ノイズの実際の値を測定しました。この回路では、超低ノイズの水晶発振器で得た100MHzの信号を60逓倍します。その結果、6GHzのリファレンスについては、位相ノイズのノイズ・フロアが-137dBc/Hzになります(図18)。整合性を確認するために、100MHzの水晶発振信号のノイズ・フロアに逓倍回路の付加位相ノイズを加算すると-173dBcになります。つまり、理にかなっているということが確認できました。6GHzのリファレンス信号は、アナログPDとして使用するダブル・バランスド・ミキサー「HMC558」のLOポートに供給します(ミキサーのIFポートはDC結合する必要があることに注意してください)。オペアンプによるアクティブ・フィルタの値を計算するには、ミキサーのPD定数KPDの値が必要です。これは、機械的な遅延ラインと電圧計を使用し、実験によって測定/取得します。実測環境では、発振器の位置にDROとMMIC VCO「HMC1166」を配置し、それぞれを使用した場合の値を計測しました。両者ではKVCOが大きく異なるので、ループ・フィルタについてはそれぞれに応じた値を設定する必要があります。アンプについては、残留位相ノイズが付加されないように「HMC606」を使用することにしました。

図17. 実測用の回路

図18. SSB位相ノイズの測定結果(その1)。サンプリング・クロックの各実装、DACの付加ノイズ、リファレンスのノイズを比較しました。いずれも、DAC出力の測定結果である5.5GHzによって正規化しています。

先述したように、周波数逓倍されたリファレンスのノイズ・フロアは-137dBc/Hzというレベルです。それに基づき、PDの比較周波数として6GHzを選択しました。ループ内の位相ノイズは20Log10 (12/6GHz) = 6dB(N = 2に相当)だけ上昇します。反対側のレッグのオペアンプ、周波数分周器、アンプの残留ノイズは、このリファレンスのノイズ・フロアよりも十分に低いので、影響は生じません。一方、PDの比較周波数として3GHzを選択した場合、リファレンスのノイズ・フロアは-143dBc/Hz(6GHzの場合に対して6dBの改善)になります。一方、N = 4に相当する状態になることから、6GHzの場合と比べて6dBの劣化が生じます。つまり、周波数を変更しても、リファレンスの絶対位相ノイズが最終的な位相ノイズに及ぼす影響は増減しません。但し、ループ内の分周器、RFアンプ、オペアンプに対し、3GHzの条件における付加ノイズの影響が及ばないようにするためには、実質的に6dBの改善が必要になります。PDの比較周波数が低くなると、付加ノイズが支配的になるポイントに到達します。逆に、PDの比較周波数を12GHzに高めると、ループ内の周波数分周器の付加ノイズを除去することができます。そのため、その周波数を採用できる可能性があります。RFアンプの付加ノイズは周波数と共に増加しますが、12GHzでも対応できるかもしれません。その場合、KPDは12GHzの条件で再測定する必要があります。本稿では、PDの比較周波数が12GHzの場合についての評価は実施しませんでした。ただ、その構成でも問題のない性能が得られる可能性があります。

実際に実装を行う場合には、ロックを取得するための回路が必要になります。これについての検証は実施しませんでした。図17のVTUNEをプリチャージし、ロックが得られるようにVCOの周波数を十分にリファレンスに近づける必要があります。

ここで、図19をご覧ください。これは、HMC1166とAPLLを使用し、オペアンプ「AD829」で構成したアクティブ・ループ・フィルタを組み合わせた場合の結果です。これを見ると、非常に優れた位相ノイズ性能が得られていることがわかります。ここでは、比較の対象として、HMC1166(VCO)とHMC440(シンセサイザ)を使用し、PDの比較周波数を1GHzに設定した実装を用意しました。その結果、APLLを使用した場合に約15dBの改善が得られることを実証できました。最も重要なのは、位相ノイズに対してクロックが支配的になるオフセット範囲は200kHz~2MHzに限定されており、DACの付加位相ノイズによって最も厳しい条件が生じた場合の悪化レベルは約10dBであるということです。それに対し、HMC440を使用した実装では、より広い20kHz~2MHzの範囲でクロックが支配的になり、最悪の場合にはDACの付加位相ノイズによって17dBの悪化が生じます。オフセット位置が近ければ、VCO APLLはリファレンスの位相ノイズをなぞり、中間オフセットの位置にループ・フィルタからのわずかなピークが現れます。その500kHz近辺の領域について、更に反復を実施することで改善が得られる可能性があります。モデリングによって検討を行ったところ、VCOのK VCOを下げることにより、有望な結果が得られました。上記の例では、COTS(商用オフザシェルフ)のコンポーネントを使用しているので、低コストかつ、かなり容易に実証実験を行うことができます。

図19. SSB位相ノイズの測定結果(その2)。APLLでロックしたVCO(HMC1166)を使用した場合のDAC出力のSSB位相ノイズを測定しました。いずれも、DAC出力の測定結果である5.5GHzで正規化しています。

図20に示したのは、DROを使用した実装に関する測定結果です。この構成では極めて優れた性能が得られますが、SWaP-Cは大きくなります。DRO APLLの性能について振り返ると、DACの位相ノイズよりもノイズは小さく、無視できるレベルでした。DACの出力の位相ノイズは、クロックのピークがDACの位相ノイズの近くになる10kHzの領域で数dB上昇します。ループの帯域幅は、DROの非常に小さい位相ノイズへの最適な遷移ポイントを得るために、非常に狭く設定しています。DRO APLLにピークが生じる原因はオペアンプにあると考えられます。目標は数dBの範囲内で達成されたと言えるでしょう。MxFEデバイス(AD9081/AD9082)の位相ノイズ性能を最大限に活用したい場合に採用すべきなのは、12GHzを使用するDRO APLLであると考えられます。

図20. SSB位相ノイズの測定値(その3)。APLLでロックしたDROを使用した場合のDAC出力のSSB位相ノイズを測定しました。いずれも、DAC出力の測定結果である5.5GHzで正規化しています。

その他のメリット

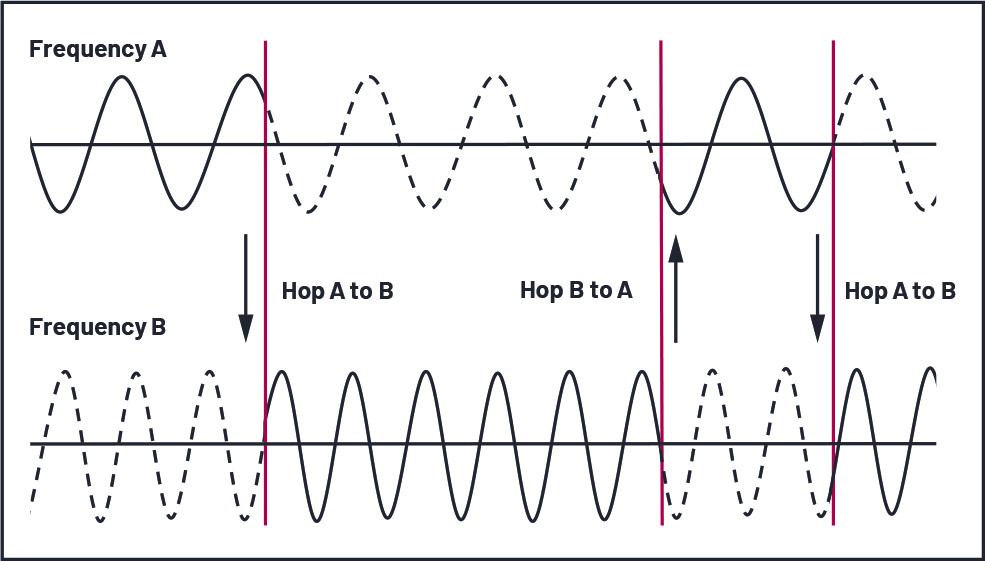

DACベースのミキサー・シンセサイザを使用した場合、位相ノイズ以外の面でのメリットも得られます。例えば、MxFEのDACをベースとした粗調/微調ミキサー・シンセサイザの場合、NCOオンリー・モードでは約300ナノ秒というアジャイルな高速周波数ホッピング(FFH:Fast Frequency Hopping)を実現できます。32個の独立したNCOの間をホッピングする際、周波数の位相コヒーレンシは図21に示すように維持されます。また、このシンセサイザの用途は、アジャイルな周波数合成に限定されるものではありません。例えば、MxFEのDACは、JESD204B/JESD204Cのデータリンクを介して任意の変調処理を実装できるだけの柔軟性を備えています。

図21. 周波数ホッピングにおける位相コヒーレンシ

まとめ

アナログ・デバイセズは、AD9081/AD9082以外にも「AD9162」、「AD9164」、「AD9172」、「AD9174」といった最新世代の高速DACを提供しています。本稿で紹介した手法を採用すれば、これらの製品の優れた性能を引き出し、位相ノイズを小さく抑えつつ、高速な周波数ホッピングを実現するRF/マイクロ波対応のアジャイルなシンセサイザを実装できます。しかも、それらの製品/手法を採用すれば、SWaP-Cに関するメリットを得ることも可能です。DAC用の固定周波数のサンプリング・クロックについては、現在主流になっている広帯域対応のVCO/PLLの能力を超えるレベルでSSB位相ノイズを非常に小さく抑えなければなりません。アナログPDを採用すれば、アクティブPFDをベースとするPLLシンセサイザと比べて、ループ内の位相ノイズ性能を10dB~20dB高めることができます。固定周波数のサンプリング・クロックを使用するシステムにおいて、最も厳しい位相ノイズの要件を満たすために推奨される実装方法はDRO APLLです。本稿では、DACをベースとする粗調/微調ミキサー・シンセサイザの例や、位相ノイズの測定結果、アプリケーション回路の例などを紹介しました。

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}