質問:

ホット・スワップ回路が発振してしまいます。データシートに記載されているように、MOSFETには10Ωのゲート抵抗を適用しました。それでも、回路の起動時にリンギングが発生します。何が問題なのでしょうか?

回答:

ホット・スワップ回路では、ハイサイドのスイッチとしてNチャンネルのMOSFETがよく使われます。その場合、回路が起動(スタートアップ)したときや電流制限が働いたときに発振が生じることがあります。これは目新しい問題ではありません。しかし、ホット・スワップ・コントローラ製品のデータシートを見ても、それに対する解決策が詳しく書かれていないことがよくあります。基本的な原理を理解することなく、安易な解決策としてゲートの入力部に値の小さい抵抗(ゲート抵抗)を追加するのは避けるべきです。そのような対処を図った結果、発振を起こしやすい基板レイアウトになってしまうことがあるからです。本稿では、まず寄生発振(Parasitic Oscillation)に関する理論について説明します。その上で、寄生発振に対する解決策を正しく適用するためのガイドを提供します。

はじめに

IC製品の中には、ハイサイドのNチャンネルMOSFET(以下、NFET)と組み合わせて使われるものがあります。例えば、ホット・スワップ・コントローラ、サージ・ストッパ、eFuse(電子ヒューズ)、理想ダイオード・コントローラなどがそれに該当します。その場合、回路をスタートアップする際や電圧/電流のレギュレーションを行う際に発振が発生する可能性があります。それらのIC製品のデータシートを見ると、この問題について簡単に触れられていることが多いはずです。また、その解決策として、値の小さいゲート抵抗を追加する方法が推奨されているケースも少なくありません。しかし、発振の根本的な原因を理解することなく、ゲート抵抗を追加するのは避けるべきです。基板レイアウトにおいて、ゲート抵抗が不適切な場所に配置されていると、回路が発振しやすくなるからです。そこで本稿では、寄生発振が発生する原因について詳しく説明します。その理論を理解すれば、基板の無駄な修正を避けられるでしょう。

そもそも、NFETのゲートの入力抵抗は理想的には無限大に見えるはずです。そのため、ゲート抵抗を追加で挿入しても意味がないように感じられるかもしれません。実際、既存のゲート抵抗の必要性に疑問を感じ、何の影響もないと判断して取り除いてしまったという方もいらっしゃるでしょう。しかし、10Ωのゲート抵抗は、ゲートのノードで生じるリンギングを抑制するための予防策として有用です。ゲートのノードには、配線パターンを起点とするタンク回路の構成要素が存在しています。例えば、プリント基板の長い配線パターンには寄生インダクタンスが存在します。また、近くのグラウンド・プレーンに対する分布容量も形成されます。それにより、高周波の信号に対してはグラウンドへのパスが生じることになります。安全動作領域(SOA:Safe Operating Area)が高くなるように最適化されたNFET(パワーMOSFET)の場合、そのゲート容量の値は数nFのレベルになります。電流処理能力を高めるために並列のNFETを追加すると、その値は更に大きくなります。加えて、NFETのVGSをクランプするためにツェナー・ダイオードが使われるケースもあります。同ダイオードも、寄生容量が形成される原因になります(とはいえ、NFETのCISSが支配的です)。

図1は、アナログ・デバイセズが提供するPowerPath™コントローラ製品の一般的な使い方を示したものです。図中には、寄生素子の成分も描いてあります。

図1. PowerPathコントローラの一般的な使用方法

図2は、図1の回路を回転させて描き直したものです。これを見ると、コルピッツ発振回路(図3)に似た回路が形成されていることがわかります。コルピッツ発振回路はゲインを備えるタンク回路であり、持続的な発振動作を得るために使用されます。NFETを使用するPowerPathコントローラ回路は、これと同様の構造を備えているということです。

図2. 図1の回路を回転させて描き直したもの

図3. コルピッツ発振回路

図3のコルピッツ発振回路では、バッファを使用することで、容量分圧器を介して正帰還をかけています。PowerPathコントローラ回路では、NFETによってそれと同様の効果が生じます。ソース・フォロワ(ドレイン共通)の構成によってACバッファとして機能し、ドレイン電流が多くなると性能が向上します。容量分圧器の最上部の信号が分圧器の中間点に注入されると、分圧器の最上部の電圧が上昇します(このプロセスが繰り返されます)。

NFETが十分にエンハンスされていない状況では、発振が生じる可能性があります。具体的には、以下のようなケースです。

- 初期のスタートアップにあたって、ゲートの電圧が上昇し、出力コンデンサが充電されるとき

- 電流がレギュレートされているとき(コントローラがアクティブ電流制限の機能を使用している場合)

- 電圧がレギュレートされているとき(サージ・ストッパなどで見られる)

筆者は、NFETによってコルピッツ発振回路のトポロジが形成されるという概念を検証することにしました。そのために、NFETを駆動するICは使用しない状態の基本的な回路を作製しました(図4)。この回路では、NFETのCGS(図4では部品としては示していません)とC2によって分圧器が形成されます。

図4. 検証用の回路。NFETによってコルピッツ発振回路のトポロジが形成されることを確認します。

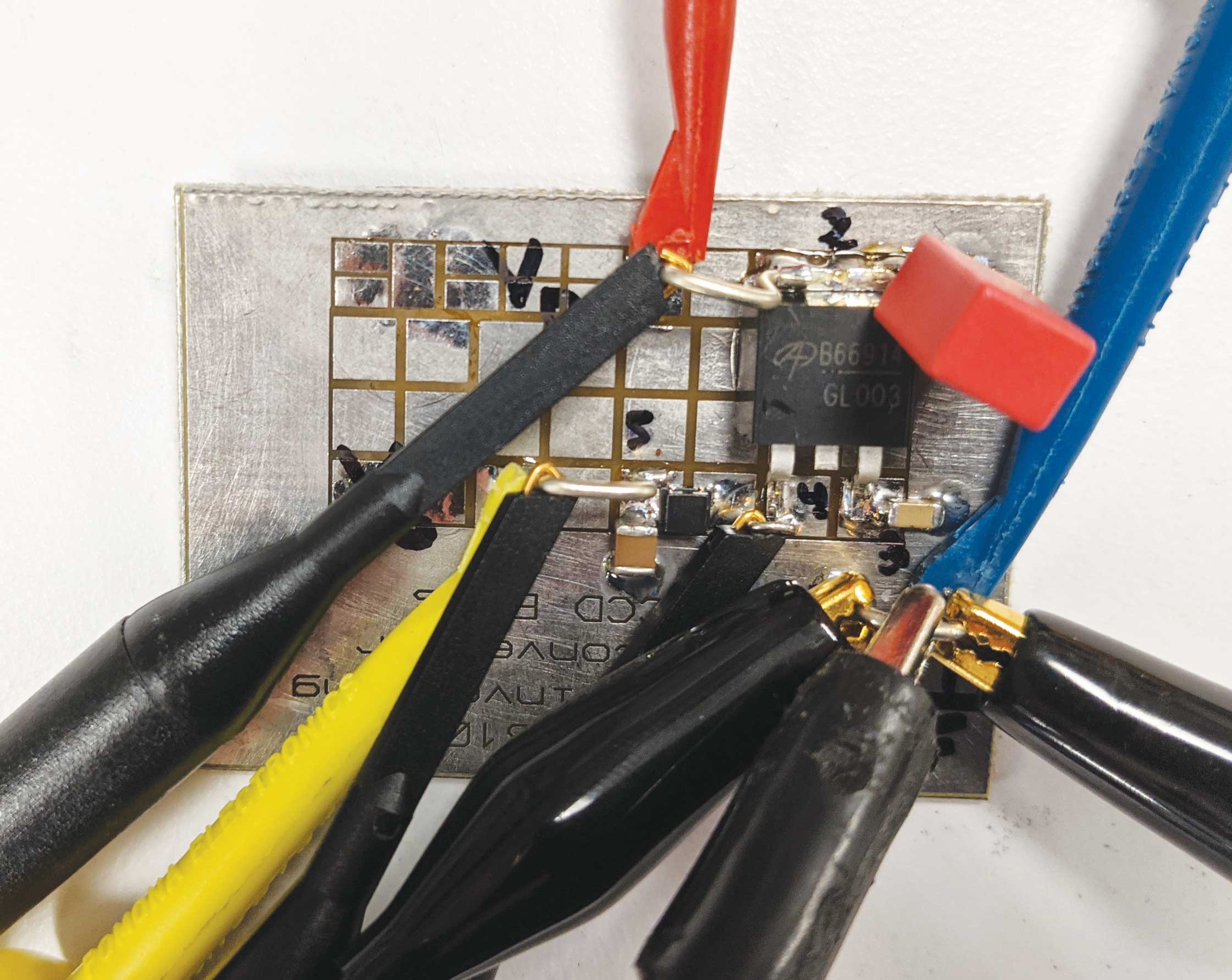

図5. 図4の回路のプロトタイプ

図5に、この回路の外観を示しました。これを使用して評価を実施したところ、図6のように発振が確認されました。この結果は、ハイサイドのNFETによってコルピッツ発振回路のトポロジが形成されるということを裏づけています。

図6. DC電圧を印加したことにより発生した発振

次に、ホット・スワップ・コントローラも存在する状態について考えます。その場合、何によって発振が誘発されるのかを確認してみましょう。ここでは、図5のボードに変更を加え、容量性の負荷を駆動するようにします(図7)。スタートアップの際、ゲートの電圧は設定されたdV/dtで上昇し、それに出力が追従します。IINRUSH = CLOAD×dV/dtという式から、出力コンデンサに対する突入電流はdV/dtによって決まることがわかります。NFETのトランスコンダクタンスgmを増大させるために、突入電流は3Aという比較的大きい値に設定することにします。この回路に対する設定や動作についてまとめると、以下のようになります。

- UV機能とOV機能はディスエーブルに設定します。

- CTRACEは配線パターンの寄生容量を表します。図7の回路では、CTRACE として10nF のセラミック・コンデンサを使用しています。

- LTRACE は配線パターンの寄生インダクタンスを表します。150nH のインダクタを、ホット・スワップ・コントローラ「LTC4260」のGATE ピンとNFET のゲートの間に追加しています。

- 2mΩのセンス抵抗により、帰還電流は10Aに制限されます。

- ゲートに付加した68nFのコンデンサにより、スタートアップの時間は数十ミリ秒に延びます。その期間はNFET が発振しやすくなります。

- 負荷として追加した15mFのコンデンサにより、スタートアップ時に数A の突入電流が引き込まれます。それにより、NFETのgm が増大します。

- 負荷として追加した12Ωの抵抗により、NFETのgmに対応する電流が更に供給されます。

図7. ホット・スワップ・コントローラを含む検証用の回路

図8に、図7の回路によって得られた結果を示しました。この波形を見ると、ゲートの電圧がNFETのスレッショルド電圧まで上昇すると、GATEのノードとOUTのノードにリンギングが発生することがわかります。このリンギングは、GATEのノードの信号が突然ステップすることに起因して生じています。その結果、突入電流にオーバーシュートが発生しています。最終的に、このリンギングは収束しています。

図8. スタートアップ時に発振が減衰する様子

過渡的なリンギングから持続的な発振に強制的に移行させるには、NFETのゲインを高める必要があります。VINを12Vから18Vに上げることで、負荷電流とgmが増加します。それにより正帰還される信号が増幅され、発振が持続するようになります(図9)。

図9. VINを高めた結果得られる持続的な発振

以上で、問題が発生する状況を再現することができました。続いては、よく知られている解決策を適用することにしましょう。つまり、10Ωのゲート抵抗をインダクタと直列に接続する形で追加します(図10)。それにより発振を効果的に抑えることができ、きれいなスタートアップ波形が得られます(図11)。

図10. ゲート抵抗を追加した検証用の回路

図11. ゲート抵抗を追加した後のスタートアップ波形。発振は生じていません。

最後に図12をご覧ください。この回路は、NFETによって形成されるコルピッツ発振回路の部分に変更を加えたものです。スイッチSWを追加し、ゲート抵抗RGATEの有無を切り替えられるようにしています。このようにすれば、ゲート抵抗による発振の減衰効果を観察できます。ゲート抵抗の値を0Ωから10Ωに切り替えると、図13に示すように発振が減衰します。

図12. ゲート抵抗の有無を切り替えられるようにした検証用の回路

図13. ゲート抵抗を追加することにより発振が停止する様子

まとめ

本稿では、NFETに関連する寄生成分によって発振が生じる回路を取り上げ、その発生原理について説明しました。また、実験用の回路を構成し、コルピッツ発振回路のモデルの検証を実施しました。更に、実験用の回路で発振の問題を再現し、よく知られた解決策によってその問題を解消できることを確認しました。重要なのは、10Ωのゲート抵抗をNFETのゲート・ピンのできるだけ近くに配置することです。それにより、NFETの入力容量と配線パターンの寄生インダクタンスを分離します。このようにすれば、ゲートのリンギングや発振の可能性を排除できます。表面実装型の抵抗を1個追加するだけなので、コストの増加は最小限に抑えられます。それだけでなく、トラブルシューティングや基板の再設計に時間を費やす必要もなくなります。