AD9083

新規設計に推奨16チャンネル、125MHz帯域幅、JESD204B A/Dコンバータ

- 製品モデル

- 2

- 1Ku当たりの価格

- 最低価格:$326.33

製品の詳細

- 動作電源電圧:1.0V~1.8V

- アナログ入力帯域幅:125MHz

- 2GSPSのサンプル・レート

- 100MHzの帯域幅でのノイズ・スペクトル密度:−145dBFS/Hz、2.0GSPSエンコード

- 100MHzの帯域幅、2.0GSPSエンコードでのS/N比:66dBFS

- 15.625MHzの帯域幅、2.0GSPSエンコードでのS/N比:82dBFS

- 100MHzの帯域幅、2.0GSPSエンコードでのSFDR:60dBc

- 15.625MHzの帯域幅、2.0GSPSエンコードでのSFDR:80dBc

- 大信号ディザ

- 2.0GSPSでのチャンネルあたりの全電力:90mW(デフォルト設定値)、チャンネルあたりの最小電力:35mW

- 柔軟な入力範囲:0.5Vp-p~2Vp-p差動

- 2.0GSPSエンコードでのチャンネル・クロストーク:90dB

- デジタル・プロセッサ

- CICデシメーション・フィルタ

- プログラマブルDDC

- データ・ゲート

- JESD204Bサブクラス1エンコード出力

- 最大16Gbps/レーンをサポート

- 柔軟なサンプル・データ処理

- 柔軟なJESD204Bレーン構成

- シリアル・ポート制御

AD9083は、16チャンネル、125MHz帯域幅、連続時間Σ-Δ(CTSD)ADCです。低消費電力、小型、使いやすさを考慮して設計された、オンチップ、プログラマブル、単極アンチエイリアシング(折返し誤差防止)・フィルタおよび終端抵抗を備えたデバイスです。

16個のADCコアは、1次CTSD変調器アーキテクチャを備え、バックグラウンド非直線性補正ロジックと自己キャンセリング・ディザが組み込まれています。各ADCの入力は広帯域幅になっており、サポートされている多様な入力範囲から選択できます。また、電圧リファレンスを内蔵しているので設計が容易になります。

アナログ入力とクロック信号は差動入力です。各ADCには、信号処理タイルがあり、Σ-Δ ADCに含まれる帯域外形状のノイズをフィルタし、サンプル・レートを低下させます。各タイルには、カスケード積分器コーム(CIC)フィルタ、有限入力応答(FIR)デシメーション・フィルタ(Jブロックによるデシメーション)を備えた直交デジタル・ダウンコンバータ(DDC)、またはデータ・ゲート・アプリケーション用の平均化デシメーション・フィルタを備えた最大3つの直交DDCチャンネルが内蔵されています。

サブクラス1 JESD204Bに基づく高速シリアル出力は、DDCの構成と受信ロジック・デバイスの許容レーン・レートに応じて、多様なレーン構成(最大4つ)にすることができます。複数デバイスの同期は、SYSREF±、TRIG±、およびSYNCINB±入力ピンを通じてサポートされています。

AD9083には必要に応じて大幅な省電力を可能にする柔軟なパワーダウン・オプションがあります。これらの機能はすべて、1.8V対応の3線式シリアル・ポート・インターフェース(SPI)を使ってプログラムできます。

AD9083は鉛フリーの100ボールCSP_BGAパッケージで提供され、−40ºC~+85ºCの工業用温度範囲で仕様規定されています。

この製品は米国の特許によって保護されています。

アプリケーション

- ミリ波イメージング

- 電子ビームフォーミングおよびフェーズド・アレイ

- マルチチャンネル広帯域レシーバー

- 電子支援手段

製品のハイライト

- 連続時間、Σ-Δ A/Dコンバータ(ADC)は、低消費電力で最小限のフィルタ処理により、最大125MHzの信号帯域幅をサポートします。

- 内蔵されたデジタル処理ブロックが、データ・ペイロードを低減し、全体的なシステム・コストを削減します。

- 設定可能なJESD204Bインターフェースが、プリント回路基板(PCB)の複雑さを軽減します。

- 柔軟なパワーダウン・オプションが用意されています。

- 特定のシステム条件を満たすように製品の各種特性と機能をSPIインターフェースで制御できます。

- 小型の9mm × 9mm、100ボールCSP_BGAパッケージ、シンプルなインターフェース、および内蔵されたデジタル処理により、PCBスペースを節約できます。

ドキュメント

データシート 2

ユーザ・ガイド 1

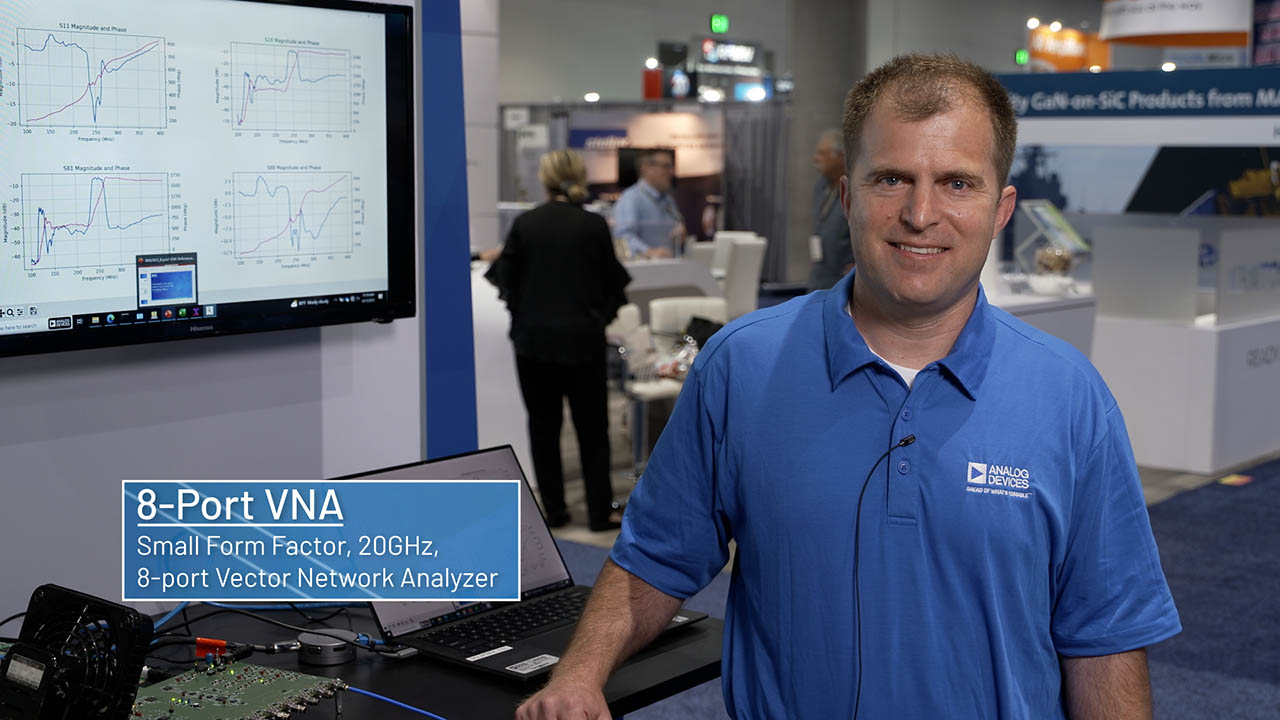

ビデオ 1

製品選択ガイド 1

デバイス・ドライバ 2

Analog Dialogue 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD9083BBCZ | 100-Ball CSPBGA (9mm x 9mm x 1.346m) | ||

| AD9083BBCZ-RL7 | 100-Ball CSPBGA (9mm x 9mm x 1.346m) |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

デバイス・ドライバ 3

- AD9083 GitHub no-OS Driver Source Code

- AD9083 GitHub Linux Driver Source Code

APIデバイス・ドライバ 1

デバイスのアプリケーション・プログラミング・インターフェース(API)のC言語ドライバは、参照用コードとして提供されており、ユーザーが、高度な関数呼び出しを使用して製品を迅速に設定できるようにします。このライブラリは、アプリケーションとハードウェアの間で抽象化レイヤとして機能します。APIはC言語のC99で開発されており、プロセッサとオペレーティング・システムに依存しない統合を保証しています。プラットフォーム固有のコード・ベースをAPI HAL層に統合することで、このアプリケーション層のコードを組込みシステムに移植することができます。

このソフトウェア・パッケージをリクエストするには、MyAnalogアカウントでサイン・インした状態でソフトウェアのリクエスト・フォームにアクセスし、対象ハードウェアの項目で「High Speed Data Converters(高速データ・コンバータ)」を選択し、ご希望のAPI製品パッケージを選択してください。さらに、Apollo MxFE™専用に2つのソフトウェア・パッケージが利用可能です。PyApp/ACE用評価パッケージがあり、さまざまなユースケースに対応したFPGAのバイナリ・ファイルが用意されています。ソフトウェアが提供された時点で、メール通知が送信されます。

評価用ソフトウェア 1

JESD204x Frame Mapping Table Generator

The JESD204x Frame Mapping Table Generator tool consists of two Windows executables that will allow the user to input any valid combination of JESD204x parameters (L, M, F, S, NP) in order to output a .csv file that illustrates the frame mapping of the JESD204x mode in table format. There is an executable that allows the user to input a single JESD204x mode and another, that allows the user to input the parameters for multiple JESD204x modes in a specified .csv format in order to output a .csv file that illustrates the frame mapping of each of the JESD204x modes that were input into separate tables.

必要なソフトウェア/ドライバが見つかりませんか?

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| µModule 降圧レギュレータ 1 | ||

| LTM8074 | 新規設計に推奨 | 40 VIN、1.2 A Silent Switcher ®(サイレント・スイッチャ) µモジュール・レギュレータ |

| クロック生成デバイス 1 | ||

| AD9528 | 新規設計に推奨 |

クロック・ジェネレータ、14 LVDS / HSTL出力、JESD204B対応 |

| マイクロ波およびmmWaveレシーバー 1 | ||

| ADAR2004 | 新規設計に推奨 | 10GHz~40GHz、4 × LO乗算器/フィルタ搭載4チャンネルRxミキサー |

| マイクロ波とミリ波のTx/Rx 1 | ||

| ADF5904 | 新規設計に推奨 |

レシーバ・ダウンコンバータ、4チャンネル、24GHz |

ツールおよびシミュレーション

ADC Companion Transport Layer RTL Code Generator Tool

This command line executable tool generates a Verilog module which implements the JESD204 receive transport layer. The user specifies in a configuration file one or more modes to be supported by the transport layer module. These modes are defined as a set of JESD204 parameter values: L, M, F, S, N', and CF. The transport layer converts JESD204 lane data output from a JESD204 link layer IP to a data bus with a fixed width, containing interleaved virtual converter samples. Both JESD204B and JESD204C link layers are supported.

ツールを開くAD9083 AMI Download

ツールを開く

LTspice®は、無料で提供される強力で高速な回路シミュレータと回路図入力、波形ビューワに改善を加え、アナログ回路のシミュレーションを容易にするためのモデルを搭載しています。