質問:

高速ADCには、なぜ数多くの電源領域が存在するのです か?

回答:

A/Dコンバータ(ADC)は、サンプル・レートや対応帯域幅の面で著しい進化を遂げてきました。今日では、無線周波数に対応するADC(RF ADC)も数多く製品化されています。また、より多くのデジタル処理機能も集積されるようになりました。結果として、電源についてはより複雑さが増しています。今日の高速ADCでは、何種類もの電源電圧が使われ、数多くの電源領域が存在します。その理由とは何なのでしょうか。

その理由について理解するには、ADCがたどってきた歴史を振り返る必要があります。ADCが文字どおりの意味で「アナログ信号をデジタル・データに変換するためのもの」だった時代には、サンプル・レートは数十MHz程度でした。また、IC内にはデジタル領域は存在しないか、存在したとしても非常に小規模でした。当時のADCでは、デジタル領域は、別のICにA/D変換後のデータを引き渡す処理を担っていました。別のICというのは、主にASICかFPGAでした。基本的には、それらのICに実装されたデータ受信用のロジック回路にデジタル・データを引き渡す処理だけを行っていたということです。そのようなADCの製造には、現在のように微細化が進む前のプロセス・ノードが使われていました。すなわち、180nm程度のプロセス・ノードです。当時のADCでは、単一の電源電圧(1.8 V)を使用し、わずか2つの電源領域(アナログ回路用のAVDD領域とデジタル回路用のDVDD領域)に分けるだけで、十分な性能が得ることができていました。

プロセス技術の進化に伴い、トランジスタのサイズは飛躍的に縮小しました。単位面積当たりに集積できるトランジスタの数が大幅に増加したということです。言い換えれば、同じ面積でより多くの機能を実現できるようになるということです。ただし、アナログ回路については、微細化によってメリットだけがもたらされるというわけではありません。ADCの設計/製造に新しいプロセスを採用した場合でも、一世代前と同等(またはそれ以上)の性能が求められるのは当然のことです。ADCの設計では、以下の事柄を念頭に置いた多面的なアプローチが求められるようになりました。

- サンプル・レートとアナログ帯域幅の向上

- 前世代と同等かそれ以上の性能の達成

- デジタル・データを受信するロジックICの負担の軽減するために、ADCにより多くのデジタル処理機能を集積

以下では、上記の内容がADCの設計に与える課題について詳しく説明します。

高速化の実現

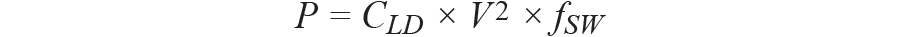

CMOS技術において、高速化(帯域幅の拡大)を図るための最も一般的な方法は、(トランジスタのサイズの)微細化を進めることです。より微細なCMOSトランジスタを使用すれば、寄生容量の値が低下してトランジスタの速度が向上します。トランジスタが高速になれば、帯域幅も広げられます。ただ、デジタル回路の消費電力は、スイッチング速度に比例して増加します。一方で、その消費電力は電源電圧の2乗に比例します。この関係は次の式で表されます。

各変数の意味は以下のとおりです。

P: 消費電力

CLD: 負荷容量

V: 電源電圧

fSW: スイッチング周波数

微細化を進める場合、電源電圧を下げることで、個々のトランジスタにおける周波数当たりの消費電力を前世代と同等レベルに維持しつつ、より高速な回路を実装できるようになります。例えば、「AD9680」と「AD9695」は、それぞれ65nmと28nmのCMOS技術で設計/製造されています。両製品は、ほぼ同一のアーキテクチャを採用し、ほぼ同一の回路で実現されています。ここで、サンプル・レートが1.25GSPSのAD9680の消費電力は3.7W、同1.3GSPSのAD9695の消費電力は1.6Wです。これは、28nmプロセスでは消費電力が65nmプロセスの約半分になるということを表しています。つまり、28nmプロセスと65nmプロセスで同じ回路を実現した場合、28nmプロセスの方が同じ消費電力で2倍の速度を実現できるということを意味します。これを大いに活用した例としては「AD9208」が挙げられます。

問題はヘッドルーム

より広い帯域幅でのサンプリングに対応するには、微細化を進める必要があります。ただ、ノイズや直線性といったADCとしての性能についても、従来どおりの水準を維持しなければなりません。このことは、アナログ回路の設計に対して従来とは異なる課題をもたらします。上述したように、微細化を進める際には電源電圧も低く設定されます。そうすると、アナログ回路のヘッドルームが大幅に縮小してしまいます。この制約の下で、同等のノイズや直線性を維持しつつ、高い周波数で動作するアナログ回路を実現しなければなりません。このような制約を回避するために、複数の電源電圧を使用して、ノイズや直線性の要件を満たすように回路が設計されるようになったのです。AD9208の場合、高速のスイッチングが必要な回路では、電源電圧として0.975Vが使用されます。そうした回路の例としては、コンパレータやそれに関連する回路、デジタル出力回路、ドライバ出力回路が挙げられます。一方で、リファレンス回路やバイアス回路には、1.9Vの電源電圧が使用されます。高い周波数で動作させるために大きなヘッドルームが必要になる入力バッファでは、2.5Vの電源電圧が使用されます。なお、このバッファは電源電圧が1.9Vであっても動作します。ただし、その場合は直線性が劣化します。他方、デジタル回路で最も重要なパラメータは速度です。デジタル回路にはヘッドルームは不要です。そのため、デジタル回路は最も低い電源電圧で動作させます。それによって、スイッチング速度と消費電力に関するCMOSのメリットを生かすということです。最新世代のADCでは、最も低い電源電圧は0.975Vとなっています。表1は、世代の異なる3種のADCの仕様をまとめたものです。

| 品番 | サンプル・レート〔MSPS〕 | プロセス・ノード〔nm〕 | 電源電圧〔V〕 | 電源領域 |

| AD9467 | 250 | 180 | 1.8, 3.3 | AVDD1, AVDD2, AVDD3, DRVDD |

| AD9625 | 2500 | 65 | 1.3, 2.5 | AVDD1, AVDD2, DRVDD1, DRVDD2, DVDD1, DVDD2, DVDDIO, SPI_VDDIO |

| AD9208 | 3000 | 28 | 0.975, 1.9, 2.5 | AVDD1, AVDD2, AVDD3, AVDD1_SR, DVDD, DRVDD1, DRVDD2, SPIVDD |

絶縁が鍵に

ディープサブミクロン・プロセスへの移行が進み、高速スイッチング回路がさらに進化したことから、ADCにはより多くのデジタル機能が盛り込まれるようになりました。「AD9467」とAD9208を例にとると、前者は180nmのBiCMOSプロセス、後者は28nmのCMOSプロセスを採用しています。ノイズ密度は、AD9467が約-157dBFS/Hzで、AD9208が約-152dBFS/Hzです。データシートを参照し、(チャンネル当たりの)総消費電力を分解能とサンプル・レートで割ると、AD9467の消費電力は約330μW/ビット/MSPSとなります。それに対し、AD9208はわずか4 0 μ W /ビット/MSPSです。AD9208は、AD9467よりもサンプル・レートがはるかに高く(前者は3GSPS、後者は250MSPS)、入力帯域幅がはるかに広く(前者は9GHz、後者は0.9GHz) 、はるかに多くのデジタル機能を搭載しています。それにもかかわらず、AD9208は、1ビット/1MSPS当たりの消費電力がAD9467の約1/8に抑えられているのです。なお、1ビット/1MSPS当たりの消費電力というのは、標準的な評価指標ではありません。ここでは、ADCの設計/製造に微細プロセスを採用することのメリットを示すためにこの指標を用いています。非常に高い密度で集積された超高速回路には、様々なブロック間でカップリングやチャタリングが生じるリスクが伴います。絶縁性を高めるには、カップリングを引き起こす様々なメカニズムについて検討した上で設計を行う必要があります。最も影響が明白なメカニズムは、電源領域の共有に起因するものです。AD9208を例にとると、一部のアナログ回路とデジタル回路で0.975Vという同じ電源電圧が使用されます。それらの回路をできるだけ離して電源領域を分割すれば、デジタル回路でチャタリングが生じる可能性を最小限に抑えることができます。なお、チップ内では、電源もグラウンドも明確に分割されています。この電源領域間の絶縁を維持するようにパッケージも設計されます。その結果、パッケージ内には、多くの電源電圧と電源領域が存在することになります。表2は、AD9208の電源領域とグラウンド領域についてまとめたものです。

| 領域 | 電源電圧〔V〕 | 説明 |

| AVDD1 | 0.975 | アナログ電源 |

| AVDD1_SR | 0.975 | SYSREF用のアナログ電源 |

| AVDD2 | 1.9 | アナログ電源 |

| AVDD3 | 2.5 | アナログ電源 |

| DVDD | 0.975 | デジタル電源 |

| DRVDD1 | 0.975 | デジタル・ドライバ用の電源 |

| DRVDD2 | 1.9 | デジタル・ドライバ用の電源 |

| SPIVDD | 1.9 | SPI用のデジタル電源 |

| AGND | — | AVDD1、AVDD1_SR、AVDD2、AVDD3用のアナログ・グラウンド・リターン |

| AGND1 | — | クロック領域のグラウンド基準 |

| AGND2 | — | SYSREF± 用のグラウンド基準 |

| AGND3 | — | 絶縁グラウンド。チップ上のアナログ領域とデジタル領域の間のバリアです。 |

| DGND | — | DVDD、SPIVDD用のデジタル・グラウンド・リターン |

| DRGND | — | DRVDD1、DRVDD2用のデジタル・グラウンド・リターン(デジタル・ドライバに対応) |

図1 は、AD9208のピン配置図です。それぞれがどの電源領域に対応するのかわかるように、色分けして示しています。

このピン配置図が、システム設計者を大いに困惑させる要因になるのかもしれません。データシートを一見した段階では、システムの性能を最適化するために、これらの領域を個々に処理しなければならないように感じられるのではないでしょうか。

このトンネルに出口はないのか?

実際には、それほど悲惨な状況にはなりません。データシートは、システム設計者に対して複数の繊細な領域が存在することを認識するよう注意を促しているだけです。その結果、電源供給回路(PDN: Power Delivery Network)が慎重に設計され、適切にパーティショニングが行われれば問題はありません。同じ電源電圧が使われる電源領域とグラウンド領域の多くは結合可能なので、PDNの設計は簡素化されます。言い換えれば、BOM( 部品表)とレイアウトも簡素化されるということです。図2と図3は、AD9208用のPDNの設計例です。システム設計における制約に応じた2つの例を示しています。

レイアウトの分割と適切なフィルタリングを組み合わせることで、PDNとBOMの複雑さを緩和しつつ、ADCの性能を引き出せるように複数の領域に対応する設計を完成させることができます。各グラウンド領域にケルビン接続を適用することで、絶縁性能を向上させることも可能です。ネットリストの観点からは、グラウンドのネットは1つしかありません。ただ、基板上で複数のグラウンド領域に対応する適切なパーティショニングを行えば、適切に絶縁を実現することができます。AD9208の評価用ボード「AD9208-3000EBZ」では、パーティショニングされた複数のグラウンドを9層目でケルビン接続しています。図4は、同評価ボードのプリント回路基板の断面図を示したものです。10層の基板を使って各グラウンドの接続を実現しています。

つまり、お先真っ暗というわけではないのですね?

もちろんです。AD9208のデータシートに示されているすべての領域を、システムの基板上で分割しなければならないというわけではありません。ADC用のPDNを最適化する上では、システムとADCの性能目標を把握することが非常に重要です。不要なグラウンド・ループを減らすことを念頭に置き、基板上で適切なパーティショニングを行ってください。そのことが、異なる領域間で生じるクロストークを最小限に抑えるための鍵になります。絶縁に関する要件に留意しつつ、可能であれば電源領域を共有することが、PDNとBOMの簡素化につながります。