要約

フェーズ・ロックド・ループ(PLL)は、最新の通信システムの基本となるビルディング・ブロックです。一般に、PLLは無線レシーバ/トランスミッタの局部発振器(LO)に使用されます。また、クロック信号分配やノイズ除去にも用いられる他、高いサンプリング・レートのアナログtoデジタル変換やデジタルtoアナログ変換用のクロック源としても盛んに使用されるようになっています。

PLLのノイズ性能は世代を経るごとに改善されています。よって電源ノイズの及ぼす影響がますます顕著になっており、場合によってはPLLのノイズ性能を制限することさえあります。

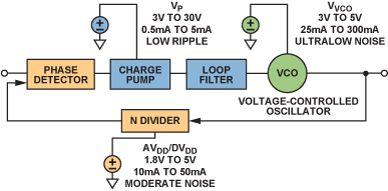

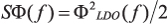

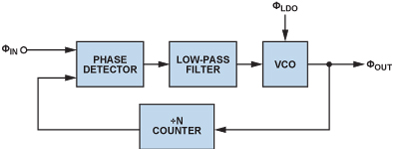

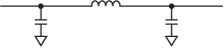

この記事では、図1に示す基本的なPLL方式に基づいて、各ビルディング・ブロックのパワーマネジメント条件を検討してみます。

PLLでは、帰還制御ループが電圧制御発振器(VCO)を駆動し、発振周波数(または位相)を正確に基準周波数の倍数にします。PLLの数学的な解析については、Best 著の“Phase-Locked Loops”1など、多くの優れた参考文献があります。また、ループ伝達関数と計算を理解するには、アナログ・デバイセズのADIsimPLL™などのシミュレーション・ツールが役に立ちます。それでは、PLLのビルディング・ブロックを順番に見ていきましょう。

VCOとVCOプッシング

電圧制御発振器は、位相検出器からの誤差電圧を出力周波数に変換します。その「ゲイン」はKVCOとされ、一般にMHz/Vで指定されます。VCOの周波数を調整するには、電圧制御型可変容量ダイオード(バラクタ)がよく用いられます。VCOのゲインは、一般に十分な周波数範囲に対応できる大きさがありますが、位相ノイズを低下できるほどではありません。これは、バラクタのノイズがKVCOによって増幅されて出力位相ノイズの一因となるためです。

マルチバンド集積VCOは、ADF4350を代表とする集積VCO付き周波数シンセサイザなどで使用されていますが、その登場によってKVCOと周波数範囲とのトレードオフが解消しました。これによってPLL設計者は、インテリジェントな帯域切り替えルーチン付きの中程度ゲインVCOを複数内蔵したICを使用し、設定された出力周波数に応じて適切な帯域を選択することができるようになりました。周波数帯のこのような分割によって、全体的に広いレンジと低ノイズが実現します。

電源の変動は、入力電圧の変化から出力周波数の変化(KVCO)への必要な変換だけでなく、出力周波数の変化に望ましくない成分を生じさせることがあります。電源の変動に対するVCOの感度は、VCOプッシング(Kpushing)と言われ、通常は必要なKVCOの数分の1です。たとえば、一般的なKpushing はKVCOの5%~ 20%です。したがって、高ゲインVCOではプッシング効果が大きくなり、VCO電源のノイズ寄与分が重要になります。

VCOプッシングを測定するには、VTUNEピンにDCチューニング電圧を印加し、電源電圧を変動させ、周波数の変化を測定します。プッシング係数は周波数の変化と電圧の変化の比であり、ADF4350 PLLを使用した測定値を表1に示します。

表1. ADF4350のVCOプッシング測定| VCO Band (MHz) |

Vtune (V) |

f1 (MHz) at VVCO = 3 V |

f2 (MHz) at VVCO = 3.3 V |

Kpushing = Δf/ΔV (MHz/V) |

| 2200 | 2.5 | 2233.446 | 2233.061 | 1.28 |

| 3300 | 2.5 | 3331.112 | 3331.799 | 2.3 |

| 4400 | 2.5 | 4462.577 | 4464.242 | 5.55 |

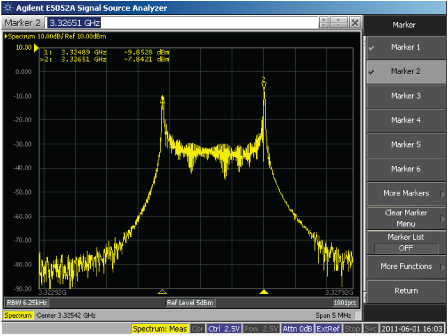

もう1つの方法は、参考文献2に述べられていますが、低周波数の矩形波を電源にDC結合しながら、VCOスペクトルの両側の周波数偏移変調(FSK)した変調ピークを観察するものです(図2)。ピーク間の周波数偏差を矩形波の振幅で割ると、VCOプッシング値が得られます。この方法はDC入力電圧の変化に伴う熱への影響を除外するため、静的なDCテストに比べて正確な測定値が得られます。図2は、3.3GHz でのADF4350 VCO出力のスペクトル・アナライザのプロットです(3.3Vの公称電源電圧に10KHz、0.6V p-pの矩形波を使用)。結果として得られる偏差は3326.51MHz-3324.89MHz=1.62MHzとなり、1.62MHz/0.6V、つまり2.7MHz/Vのプッシング値となります。これは、表1の2.3MHz/Vという静的な測定値に対応します。

電源の変調に対するADF4350 VCO応答のスペクトル・アナライザのプロット

PLLシステムでは、高いVCOプッシング値は、VCO電源ノイズの逓倍率が大きくなることを意味します。VCO位相ノイズへの影響を最小限に抑えるには、低ノイズの電源が必要になります。

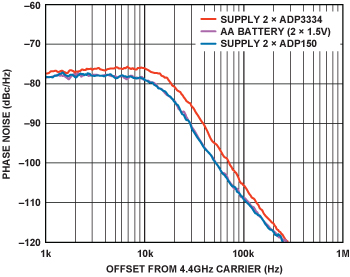

参考文献3と4からは、さまざまな低ドロップアウト・レギュレータ(LDO)がPLL位相ノイズにどのような影響を与えるかについて好例が得られます。たとえば、ADF4350を作動させるLDOとしてADP3334とADP150の比較が行われました。ADP3334 LDOの積分RMSノイズは、10Hz から100KHzの4ディケードで27μVです。これに対して、ADF4350評価用ボードで使用するLDOのADP150では、9μVになります。図3は、測定されたPLL位相ノイズ・スペクトル密度の差を示しています。これは、VCOプッシングが最大(表1)であった4.4GHz のVCO周波数で測定したものであり、つまり最悪時の結果を示しています。ADP150レギュレータのノイズは十分に低く、VCOノイズへの影響はほとんどありませんでした。なお、2本の(「ノイズのない」と言われる)単3電池で測定を繰り返して、これを確認することができました。

4.4GHzにおけるADF4350の位相ノイズの比較

図3は、ADF4350にとって低ノイズ電源が重要であることを示しています。しかし、電源やLDOのノイズ条件はどのように指定すればよいでしょうか?

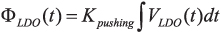

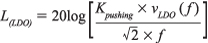

VCOノイズの場合と同様に、LDOの位相ノイズ寄与分は付加成分ΦLDO(t) としてモデル化できます(図4を参照)。VCOの過剰位相式を再利用すると、次式が得られます。

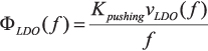

あるいは、周波数領域では次式になります。

ここで、vLDO(f) はLDOの電圧ノイズ・スペクトル密度です。

1Hz 帯域幅におけるシングル・サイドバンド電力スペクトル密度SΦ(f) は、次式で与えられます。

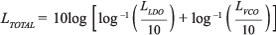

これをdB単位で表すと、電源ノイズの位相ノイズ寄与分を計算する式は、次のようになります。

|

(1) |

ここで、L(LDO)は、オフセットfにおけるVCO位相ノイズ(dBc/Hz単位)に対するレギュレータのノイズ寄与分です。Kpushing は、VCOのプッシング係数です(Hz/V単位)。vLDO(f) は、任意の周波数オフセットにおけるノイズ・スペクトル密度です(V/√Hz 単位)。

フリーランのVCOでは、合計ノイズはLLDOとVCOノイズとの2乗和の平方根(rss: root-sum-square)です。したがって、dB単位で表すと次のようになります。

たとえば、100KHzオフセットにおいて測定された位相ノイズが-116dBc/Hz でプッシング値が10MHz/VのVCOを考えてみましょう。100KHzにおいてVCOのノイズ性能を低下させないために、電源に必要なノイズ・スペクトル密度はいくらになるでしょうか?電源ノイズとVCOノイズは2乗和の平方根として加算されるため、電源ノイズはVCOノイズより少なくとも6dB小さくしてその寄与分を最小限に抑える必要があります。したがって、LLDOは-122dBc/Hz未満でなければなりません。式1を使用すると、次のようになります。

vLDO(f) の値を求めると、次のようになります。

vLDO(f)= 11.2 nV/√Hz at 100-kHz offset

所定のオフセットでのLDOノイズ・スペクトル密度は、一般にLDOデータシートの代表的性能曲線から読み取ることができます。

VCOが負帰還PLLで接続されている場合、LDOノイズ(LLDO)に対しては、VCOノイズと同様、PLLループ・フィルタによって高周波成分のみが取り出されます。したがって、上の式は、PLLループ帯域幅より大きな周波数オフセットにのみ当てはまります。PLLのループ帯域幅の範囲内では、PLLはLDOノイズのトラッキングとフィルタリングによってその寄与分を減らすことができます。

LDOフィルタリング

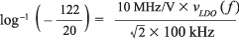

LDOノイズを改善するには、一般に2つの選択肢があります。ノイズの少ないLDOを使用するか、LDOの出力にポストフィルタリングを行うかです。フィルタなしのノイズ条件が手頃なLDOの能力を上回る場合は、フィルタリングを選ぶとよいでしょう。帯域外LDOノイズを20dB減らすには、通常は簡単なLCを用いたπ型フィルタで十分です(図5)。

部品の選択には注意が必要です。フェライト・コア付きの代表的なインダクタはマイクロヘンリーのレンジになるため、その飽和電流(ISAT)を考慮しなければなりません。飽和電流は、インダクタンスが10%下がるDC電流レベルとして、インダクタのデータシートに指定されています。VCOが消費する電流はISATを下回る必要があります。フィルタ両端でIRドロップを生じさせる実効直列抵抗(ESR)も考慮しなければなりません。300mA DCを消費するマイクロ波VCOの場合、IRドロップを100mV未満にするためには0.33Ω未満のESRを持つインダクタが必要です。さらに、フィルタ応答を減衰させ、LDO安定性を改善するには、低いけれどもゼロではないESRが望ましいものとなります。実用的な方法としては、寄生ESRがきわめて低いコンデンサを選択し、専用の直列抵抗を追加すると良いでしょう。NI Multisim™などのダウンロード可能なコンポーネント・エバリュエータを使用すれば、SPICEで簡単にシミュレートすることができます。

チャージ・ポンプとフィルタ

チャージ・ポンプは位相検出器の誤差電圧を電流パルスに変換し、PLLループ・フィルタはその電流パルスを積分し、平滑化します。チャージ・ポンプは、一般にその電源電圧(VP)を最大0.5V下回る値で動作することができます。たとえば、チャージ・ポンプの最大電源電圧が5.5Vである場合、最大5Vの出力電圧でしか動作できません。VCOがこれより高いチューニング電圧を必要とする場合、一般にはアクティブ・フィルタが必要です。実際のPLLに関する役に立つ情報とリファレンス設計については、実用回路CN-01745を参照してください。高電圧に対処する方法については「高電圧VCOを用いた高性能フェーズ・ロックド・ループの設計」6(Analog Dialogue、Volume 43、Number 4 (2009 英文))を参照してください。アクティブ・フィルタに代わるもう1つの方法は、ADF4150HVなど、高電圧向けに設計されたチャージ・ポンプ付きのPLLを使用することです。ADF4150HVは30Vという高いチャージ・ポンプ電圧で動作できるため、多くの場合アクティブ・フィルタが不要です。

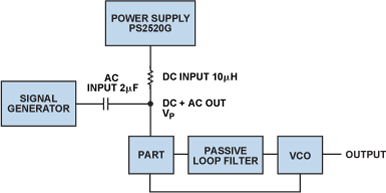

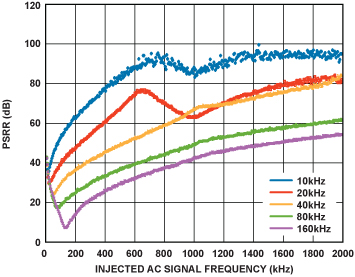

チャージ・ポンプの消費電流が低いため、ブースト・コンバータを使用して、低い電源電圧から高いチャージ・ポンプ電圧を生成するとよいと思われるかもしれません。しかし、この種のDC/DCコンバータに付随するスイッチング周波数リップルによって、VCOの出力に望ましくないスプリアス・トーンが生成されることがあります。高いPLLスプリアスによって、トランスミッタのエミッション・マスク・テストが失敗したり、レシーバ・システムの感度や帯域外ブロッキング性能が低下する可能性があります。コンバータ・リップルの仕様の指針とするため、図6の測定セットアップを使用して、様々なPLLループ帯域幅において電源電圧変動除去比の周波数特性に関する測定を行いました。

17.4mV(-22dBm)のリップル信号を電源電圧にAC結合し、周波数をスイープしました。各周波数でスプリアス・レベルを測定し、-22dBmの入力とスプリアス出力レベルとの差(dB単位)としてPSRを計算しました。チャージ・ポンプ電源に0.1μFと1nFのデカップリング・コンデンサを配置してAC結合された信号を若干減衰させたため、各周波数ポイントにおいてリップル信号が17.4mVとなるようにジェネレータの信号出力レベルを調整しました。結果を図7に示します。

最初は、PLLループ帯域幅の範囲内で周波数が増加するにつれて、電源電圧変動除去比が悪化します。周波数がPLLループ帯域幅に近づくと、リップル周波数はリファレンス・ノイズと同様に減衰し、PSRが改善します。このプロットから、スイッチング・スプリアスを最小限に抑えるためには、理想的には1MHzを超える高いスイッチング周波数を持つブースト・コンバータが望ましいことがわかります。また、可能ならば、PLLループ帯域幅を最小限に抑えるとよいでしょう。

1.3MHz のスイッチング速度を持つADP1613は、適切なブースト・コンバータの好例です。PLLループ帯域幅を10KHzに設定すれば、約90dBのPSRが可能であり、80KHz のループ帯域幅で、PSRは50dBになります。PLLのスプリアス・レベル条件から始めて、逆算することによって、ブースト・コンバータ出力において必要なリップル・レベルを決定することができます。たとえば、PLLのスプリアスが-80dBm未満でなければならず、PSRが50dBである場合、チャージ・ポンプ電源への入力でのリップル電圧は-30dBm未満、つまり20mVp-p未満とする必要があります。チャージ・ポンプ電源ピンの近くに十分なデカップリング容量が配置されていれば、このレベルのリップル電圧はリップル・フィルタによって簡単に実現できます。たとえば、100nFのデカップリング・コンデンサにより、1.3MHzで20dBを上回るリップル減衰が得られます。適切な電圧定格を持つコンデンサを使用するよう注意してください。たとえば、ブースト・コンバータが18Vの電源電圧を生成する場合、20V以上の定格を持つコンデンサを使用してください。

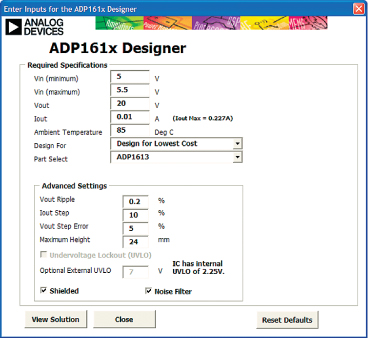

Excel ベースの設計ツールADP161xを使用すれば、ブースト・コンバータとリップル・フィルタの設計が簡単にできます。図8は、5V入力、20V出力の設計のユーザ入力画面の例です。コンバータ段の出力での電圧リップルを最小限に抑えるため、ノイズ・フィルタのオプションが選択されており、VOUTリップル・フィールドは最小値に設定されています。高圧チャージ・ポンプの消費電流は最大2mAであるため、余裕をみてIOUTには10mAが入力されています。この設計は、20KHzのPLLループ帯域幅を用いてADF4150HV評価用ボードでテストしました。図7からは、約70dBのPSRが予想されます。優れたPSRによって、ノイズ・フィルタを省略した場合でも、このセットアップのVCO出力には目立ったスイッチング・スプリアスは現れませんでした(<-110dBm)。

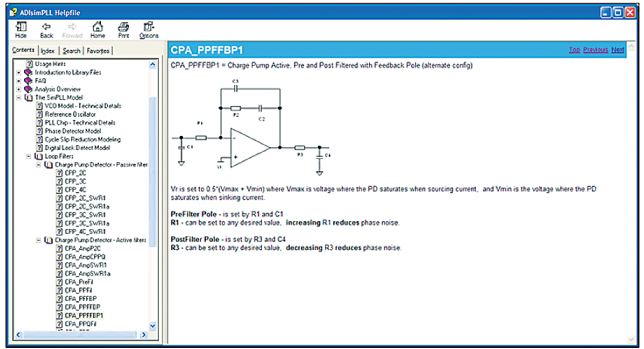

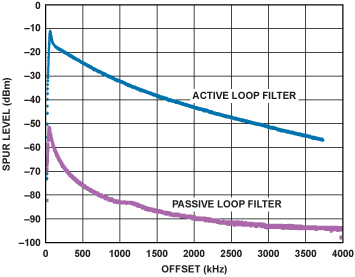

最後の実験では、高いVCOチューニング電圧の生成に現在最もよく使用されている設計であるアクティブ・フィルタのPSRと高圧チャージ・ポンプのPSRを比較しました。測定を行うため、図6の測定セットアップのように、ADF4150HVのチャージ・ポンプ電源(VP)には、パッシブ・ループ・フィルタを用いて1V p-pの振幅を持つAC信号を注入しました。ループ・フィルタは、パッシブ・フィルタの代わりに、同じ帯域幅のアクティブ・フィルタを用いて同じ測定を繰り返しました。使用したアクティブ・フィルタは、ADIsimPLL(図9)に示すタイプCPA_PPFFBP1です。

公正な比較を行うために、チャージ・ポンプとオペアンプの電源ピンでのデカップリングは同じとし、10μF、10nF、10pFのコンデンサを並列接続しました。測定結果を図10に示します。アクティブ・フィルタに比べると、高電圧チャージ・ポンプのスイッチング・スプリアス・レベルは、40dB~ 45dBの減少を示しています。高電圧チャージ・ポンプのスプリアス・レベルが改善された理由は、アクティブ・フィルタから見たループ・フィルタ減衰量が小さいことによって部分的に説明できます。アクティブ・フィルタでは最初の極の後に注入リップルがありますが、パッシブ・フィルタでは入力側にあります。

最後に付記しておきますが、図1に示す3番目の電源レール(デバイダ電源、AVDD/DVDD)は、VCOやチャージ・ポンプ電源に比べて電源条件が厳しくありません。これは、PLL(AVDD)のRF部が一般に安定したバンド・ギャップ基準のバイアス電圧を持つバイポーラECLロジック段であり、電源電圧の影響を比較的受けにくいからです。また、デジタルCMOSブロック(DVDD)は、その特性によって電源ノイズの影響を受けにくいものです。したがって、このレールに対しては電圧と電流の条件を満たす中程度の性能を持つLDOを選び、すべての電源ピンの近くで十分なデカップリングを施すことをお勧めします。一般には、100nFと10pFの並列接続で十分です。

結論

主要なPLLブロックに対するパワーマネジメント条件を論じ、VCO電源とチャージ・ポンプ電源の仕様を求めました。アナログ・デバイセズでは、リファレンス回路やソリューションを含め、パワーマネジメントICやPLL IC向けに複数のデザインイン・サポート・ツールを用意しており、ADIsimPLLやADIsimPowerなどのシミュレーション・ツールも提供しています。電源ノイズとリップルがPLL性能に与える影響を理解していれば、パワーマネジメント・ブロックの仕様を逆算して求めることにより、最高の性能を持つPLL設計を実現できます。

参考資料

1Best, Roland E. Phase Locked Loops: Design, Simulation, and Applications. 6th edition. 2007. McGraw-Hill. ISBN 9780071493758.

2Colin, Dennis. Externally Induced VCO Phase Noise. Micronetics, Inc. Reprint: Microwave Journal. Feb 2002.

3http://www.radio-electronics.com/analysis/rf-technology-design/2010-11/integrated-plls-vcos-02.php.

4回路ノート CN-0147、「位相ノイズ低減のための、フラクショナルN PLLと電圧制御発振器(VCO)にローノイズLDOレギュレータを使った電源供給の検討」Analog Devices. 2010.

5Circuit Note CN-0174, Low Noise, 12 GHz, Microwave Fractional-N Phase-Locked Loop (PLL) Using an Active Loop Filter and RF Prescaler. Analog Devices. 2010.

6Harney, Austin「高電圧VCOを用いた高性能フェーズ・ロックド・ループの設計」Analog Dialogue, 43-12. 2009.