はじめに

MP3プレーヤ、パーソナル・メディア・プレーヤ、デジタル・カメラなど、民生用のポータブル・アプリケーションで高性能と低消費電力を実現することは、設計者にとって昔から大きな課題です。こうしたバッテリ駆動のシステムでは通常、組み込み型のデジタル・シグナル・プロセッサ(DSP)を使用して、マルチメディア・アプリケーションを扱うときは最大限の処理能力を発揮するようにし、スリープ・モードのときは消費電力が最小になるようにします。ポータブル向けのバッテリ駆動製品では、バッテリ寿命が最も重要であり、製品が成功するかどうかは電力システムの効率性に直接関わっているといってもよいほどです。

このようなシステムの主要部品となるステップダウンDC/DCスイッチング・レギュレータは、4.5Vなどの高い電圧電源から1V程度の低い電源電圧を効率的に生成します。レギュレータとして一定の電圧を維持しながら、入力側の電源や負荷電流の変動に速やかに応答する必要があります。ここでは、優れたレギュレーション、高効率、高速応答を可能にするアーキテクチャについて説明します。

スイッチング・レギュレータの構造

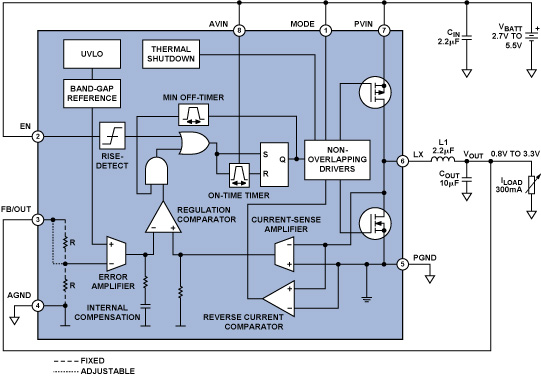

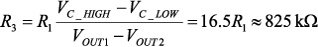

図1 は、アナログ・デバイセズの低デューティ・サイクル、3MHz、同期式ステップダウン・コンバータADP2102を使用した代表的なアプリケーション回路です。このデバイスには、複数の固定出力の電圧オプションや抵抗プログラマブルの電圧オプションがあります。ここでは、接続は固定電圧構成とし、5.5V入力電圧から0.8Vの安定化した出力電圧を生成し、300mA負荷を駆動します。抵抗プログラマブル・アプリケーションの例は後述します。

ここで回路の動作を簡単に説明しましょう。DC出力電圧の一部を誤差アンプの内部リファレンスと比較し、さらにこの出力を電流検出アンプの出力と比較してワンショットを駆動し、VOUT/VINの比に基づき一定の期間オンになります。ワンショットは、ハイサイドゲート・トランジスタをオンにし、インダクタL1の電流が上昇します。ワンショットがタイムアウトすると、トランジスタがオフになり電流が下降します。ミニマム・オフタイマと最小電流値(「谷」)によってインターバルが定められ、その後、ワンショットが再びパルス出力されます。内部のワンショット・タイマは、安定状態で一定の周波数を維持するために入力電圧フィードフォワードを用います。

この発振は約3MHzで無期限に継続しますが、入力電圧と負荷の過渡変化に応答するため必要に応じて外れ、これによって設定した値で出力電圧を維持し、出力負荷が必要とする値で平均インダクタ電流を維持します。

上述した方法は比較的新しいものです。これまで長い間、DC/DC変換の主な方法といえば、定周波ピーク電流による方法でした。ステップダウンDC/DCコンバータに実装するときは、「立下がりエッジ変調」ともいわれます。この方法の説明、および上述のオン時間が一定の谷電流モード・コンバータと比較した場合の長所と短所の評価については、後半にある「ステップダウンDC/DCコンバータにおける一定オン時間の谷電流モード制御方式の利点」を参照してください。

ADP2102には、低電圧ロックアウト、ソフト・スタート、サーマル・シャットダウン、短絡保護、±1%の帰還精度があります。また、上述のアーキテクチャにより、メイン・スイッチのオン時間を60ns以下にすることができます。

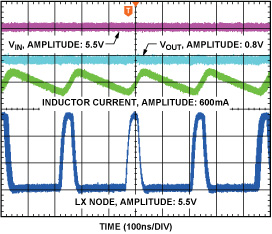

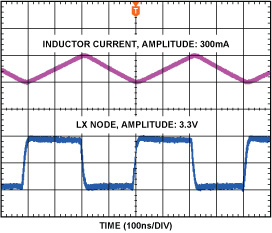

図2は、さまざまな条件下での代表的な波形です。図2aは、ILOAD=600mAでのVIN=5.5VからVOUT=0.8Vへの大きな電圧変換を伴う低デューティサイクルを示しています。グラフから読み取れるように、オン時間の最小値は3MHzのスイッチング周波数で45nsです。

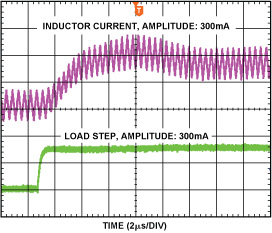

図2bは、負荷電流と負荷電流の300mAステップ増加に応じたインダクタ電流を示しています。

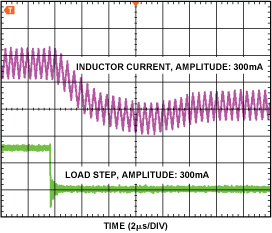

図2cは、負荷電流と負荷電流の300mAステップ減少に応じたインダクタ電流を示しています。

図2dは、ADP2102が50%のデューティ・サイクルで動作するときに低調波発振がないことを示しています。低調波発振は、ピーク電流モード制御を使用する部品で問題となるものですが、このデバイスでは、デューティ・サイクルの値が50%近傍にある状態でもこのような低調波発振は起きません。

DSP アプリケーションにおける動的な電圧レギュレーション

DSPを用いるポータブル・アプリケーションでは、通常スイッチング・コンバータがDSPのコア電圧とI/O電圧を提供します。どちらの電源もバッテリ・アプリケーション用に設計された高効率DC/DCコンバータが必要です。コア電圧を供給するレギュレータは、プロセッサのクロック速度に基づいて、あるいはソフトウェアの指示に従って動的に電圧を変更しなければなりません。大きさも全体的に小さいことが重要です。

ここでは、Blackfin®プロセッサの内部レギュレータを外部の高効率レギュレータに置き換えることによって、バッテリ駆動のアプリケーションでシステムの電力効率が向上することについて説明します。

ダイナミック・パワーマネジメント

プロセッサの消費電力は、動作電圧(VCORE)の2乗に比例し、動作周波数(FSW)に対して直線的に比例します。このため、周波数を低くすれば動的な消費電力が直線的に低下しますが、コア電圧を低減すれば動的な消費電力が大幅に低下します。

電力が重要なアプリケーションでは、DSPが単に動作の監視や外部トリガの待機状態にあるだけの場合に、電源電圧を変えずにクロック周波数のみを変更するという方法が有効です。ただし、高性能バッテリ駆動のアプリケーションでは、周波数の変更のみでは十分な電力節約にはなりません。Blackfinプロセッサなどの高度なパワーマネジメント機能を備えたDSPは、周波数の変更と共にコア電圧を変更できるため、それぞれの状況でバッテリの負荷を最適化することができます。

BlackfinプロセッサADSP-BF53xシリーズの動的電圧レギュレーションは、内部電圧コントローラと外部MOSFETによって行います。この方法の利点は、DSPサブシステムに単電圧(VDDEXT)を利用できると同時に、DSPの必要なコア電圧(VDDINT)はMOSFETから得られることです。内部レジスタによって安定化コア電圧をソフトウェアで制御できるため、MIPSだけでなく、最終的には消費電力を調整して最適なバッテリ寿命を実現できます。

この内部Blackfinレギュレータによる方法を完全に実装するには、外部MOSFET、ショットキー・ダイオード、大型インダクタ、複数の出力コンデンサが必要です。これでは、比較的大きなPCボード面積を使用するわりには、効率が低くて高価なソリューションになります。内蔵レギュレータに必要な大型インダクタとコンデンサを使用すれば、ポータブル・デバイスをできるだけ小さくしたい消費者の要望と矛盾し、システム設計者が苦しむことになります。内蔵のレギュレータ・コントローラが比較的効率が低い(一般に50 ~ 75%)ということもあり、この方法はポータブル向けの高性能バッテリ駆動アプリケーションに最適とはいえません。

外部レギュレーション

Blackfinによる統合方式に備わった効率は、最新DC/DCスイッチング・コンバータを設計することで90%以上に高めることができます。外部レギュレータを使用すれば、外付け部品のサイズも小さくなります。

ダイナミック電圧スケーリング(DVS)制御には、スイッチド抵抗(DACを使用して実装できる場合もある)からパルス幅変調(PWM)(内部方式と同じレベルの精細度を実現できる)まで、さまざまな方法があります。どの方法を使用する場合も、ソフトウェア制御によってレギュレーションのレベルを変更する能力が求められます。このレギュレーション制御の方法は内部レギュレータ方式に固有のものですが、外付け方式で追加する必要があります。

ここでは、プロセッサが低いクロック速度で動作するときに、ADP2102同期式DC/DCコンバータを使用してコア電圧の値を1.2 ~ 1.0Vに動的に変化させることにより、DSPのコア電圧を調整する2つの方法を説明します。

ADP2102高速同期スイッチング・コンバータは、2.7 ~ 5.5Vのバッテリ電圧で駆動すると、コア電圧を0.8Vまで低く調整できます。一定オン時間制御、電流モード制御および3MHzスイッチング周波数により、優れた過渡応答、高効率、高品質のライン、および負荷のレギュレーションが実現します。高スイッチング周波数により、超小型の多層インダクタやセラミック・コンデンサを使用できます。省スペースの3mm×3mm LFCSPパッケージですが、ADP2102には3、4個程度の外付け部品しか必要ありません。全機能がそろっているばかりでなく、低電圧ロックアウト、短絡保護、サーマル・シャットダウンなどの安全機能も備えています。

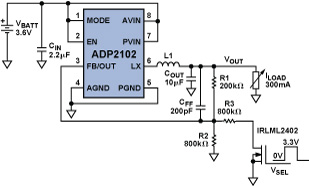

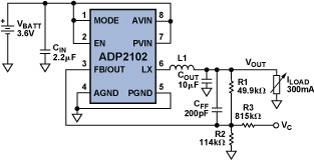

図3は、DVSを実装した回路です。ADSP-BF533 EZ-KIT Lite®評価ボードの3.3Vシステム電源がADP2102降圧コンバータを駆動し、外部抵抗分圧器R1およびR2を使用して出力電圧が1.2Vに設定されます。DSPのGPIOピンを使用して、必要なコア電圧を選択します。帰還抵抗を変更することでコア電圧を1.2 ~ 1.0Vの間で調整します。NチャンネルMOSFETは、抵抗R3をR2と並列に挿入することで分圧器を修正しています。IRLML2402の0.25ΩRDSon は、R3 と比較すると小さい値です。3.3VのGPIO電圧を使用して、MOSFETゲートを駆動します。さらに優れた過渡性能と負荷レギュレーションの改善のためには、フィードフォワード・コンデンサCFF が必要です。

2レベル・スイッチングの一般的なアプリケーションの条件は、以下のとおりです。

- DSP コア電圧 (VOUT1) = 1.2 V

- DSP コア電圧 (VOUT2) = 1.0 V

- 入力電圧 = 3.3 V

- 出力電流 = 300 mA

値の大きな抵抗器を使用して、抵抗分圧器全体の電力損失を最小限に抑えます。また、フィードフォワード・コンデンサがスイッチング中のゲートとドレイン間の容量の影響を低減します。この遷移中に生じるオーバーシュートやアンダーシュートは、より小さな値の帰還抵抗とより大きな値のフィードフォワード・コンデンサを使用することによって最小化することができますが、その場合は余分に電力を消費することになります。

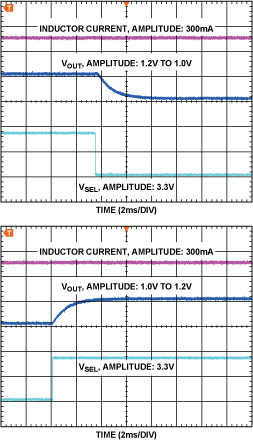

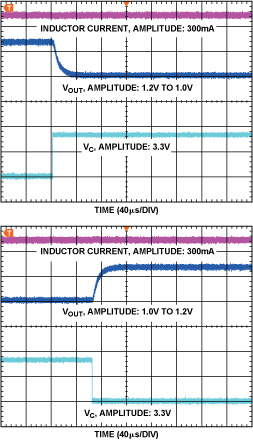

図4に、出力電流IOUT、出力電圧VOUT、制御電圧VSELを示します。VSELのローレベルで出力電圧が1.0Vになり、VSELのハイレベルで1.2Vに調整されます。

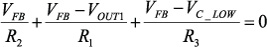

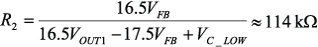

DVS 用に2 種類の電圧を生成するためのもっと簡単な方法は、抵抗を追加して制御電圧VC によってフィードバック回路に電流を投入することです。制御電圧のデューティ・サイクルを調整することによって平均DCレベルが変化します。このようにして、単一の制御電圧と抵抗を使用して出力電圧を調整できます。以下の式によって、抵抗R2とR3 の値、および制御電圧振幅レベルVC_LOW とVC_HIGH の値を計算します。

|

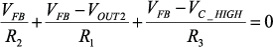

(1) | |

|

(2) |

VOUT1=1.2V、VOUT2 =1.0V、VFB=0.8V、VC_LOW=3.3V、VC_HIGH=0V、R1=49.9kΩ、R2、R3から、次のように計算できます。

|

(3) | |

|

(4) |

この方法では遷移がより滑らかになります。容量性負荷を駆動できる制御信号源しか使用できないMOSFETスイッチング方式と異なり、この方法では抵抗負荷を駆動できる制御電圧ならどれでも使用でき、任意の出力電圧の組み合わせや出力負荷電流に調整できます。したがって、必要に応じてコア電圧を調整することでDSPの電力消費を低減できます。図5に、上述の方法を実装した図を示します。図6は、この電流投入方式を使用した2出力電圧間の遷移を示しています。

参考文献

- ADP2102 データシート、アナログ・デバイセズwww.analog.com/jp

- Hariman, GeorgeおよびChris Richardson『Control Methods Solve Low Duty-Cycle Dilemmas』Power Electronics Technology 2006年9月

- Ridley, R.B.『A new continuous-time model for current-mode control with constant frequency, constant on-time and constant off-time in CCM and DCM』IEEE Power Electron. Spec. Conf. Record. 1990年、382 ~ 389ページ

- Rossetti, NazzarenoおよびSeth R. Sanders『Valley Design Techniques Outperform Peak Current Mode Approach for CPU Supplies』Power Electronics Technology 2001年7月

ステップダウンDC/DC コンバータにおける

一定オン時間の谷電流モード制御方式の利点

一定周波数ピーク電流制御方式は、外側電圧ループと内側電流ループの2 つのループを使用して、高い入力電圧から低い出力電圧を生成します。制御信号と出力間にわずかな位相シフトが存在するだけなので簡単に補償できます。

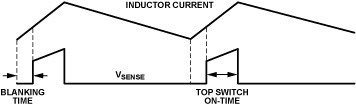

NMOSメイン・スイッチを通るインダクタ電流は、一般にメイン・スイッチがオンのときにスイッチの両端での電圧降下を監視するか、入力とメイン・スイッチのドレイン間に配置された直列抵抗の両端での電圧降下を監視することによって測定します。いずれの場合も、インダクタの電流検出中にスイッチ・ノード上の寄生成分によってリンギング動作が生じるため、ブランキング時間をおいてからインダクタ電流を測定する必要があります。このため、低デューティ・サイクルの動作中では、メイン・スイッチがオン状態に利用できる時間が少なくなります。図Aは、インダクタ電流とメイン・スイッチ両端の電流検出信号を示しています。この信号はブランキング時間とオン時間で構成されています。

ブランキング時間によって決まります。

低デューティ・サイクル動作中、すなわち出力が入力と比べてはるかに小さいときに、メイン・スイッチのターンオンは常に内部クロックで制御されており、帰還ループに依存しません。したがって、最小オン時間が存在し、そのために高いスイッチング周波数での動作が制限されます。また、セトリング時間の制約のため、パルス幅が十分でないために電流の検出ができません。ブランキング時間がメイン・スイッチのオン時間の大部分を占めるため、電流検出用の時間がほとんどありません。携帯電話やメディア・プレーヤなどのポータブル・アプリケーションでは、DSPコアのために0.9V程度の出力電圧が必要です。インダクタのサイズを最小にし、ソリューション全体のサイズを小さくするには、高スイッチング周波数が望ましいのですが、この制御方式を使用すると、高いスイッチング周波数を使用して高い入力電圧から低いデューティサイクル電圧を生成することが難しくなります。

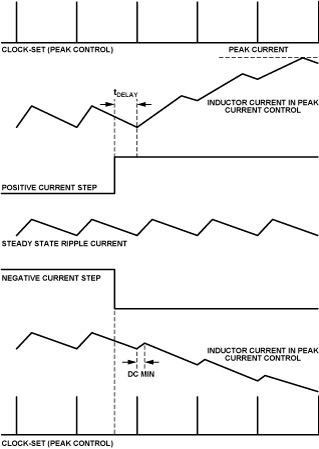

立ち下がり変調制御の2番目の制約は、過渡応答が不十分なことにあります。図Bは、負荷電流の正と負の変化に応じた代表的な波形を示します。ポータブル・アプリケーションでは、出力コンデンサのサイズとコストを最小にしながら高速過渡応答を実現しなければなりません。正の負荷電流ステップが出力で生じるケースでは、出力応答を1クロック周期分の遅延が生じます。一方、負の負荷電流ステップのケースは、電流制御ループの速度に従って、コンバータがハイサイドのオン時間を最小幅に設定します。このため、負の負荷過渡応答のときには最小の遅延応答が不可能であり、激しいオーバーシュートやアンダーシュートの過渡現象が発生します。これを抑制するには、別途、出力に容量を追加する必要があります。

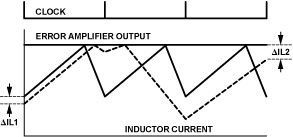

固定周波数で動作するピーク電流制御コンバータの3番目の制約は、50%を超えるデューティ・サイクルでの不安定性(図C)により低調波発振が生じ、平均出力電流が減少し、出力電流リップルが増大することです。50%を超えるデューティ・サイクルでは、インダクタ電流の増加(ΔIL1)は時間とともに大きくなる傾向があり、I2(ΔIL2)がさらに増大することになります。この問題を解決するには、スロープ補償やランプ補償が必要になり、設計が一層複雑になります。一般には、インダクタ電流検出信号に外部ランプを追加します。

固定周波数ピーク電流制御コンバータの不安定性の問題

これらの問題は、「立ち上がりエッジ変調」といわれる一定のオン時間の谷電流モード制御方式によって解決できます。この方法では、メイン・スイッチのオン時間が設計で固定されており、オフ時間は谷電流検出信号によって変調され、スイッチング周期がオン時間とオフ時間を足した値になるように調整されます。このアーキテクチャでは、メイン・スイッチに最小オン時間を設けることによって高周波動作が簡単になり、高い入力電圧から簡単に低電圧出力を生成できます。

低電圧のDC/DC降圧コンバータでは、メイン・スイッチは10%の時間だけオンですが、同期スイッチは残りの90%の時間オンになります。このため、ローサイド・スイッチ電流のサンプリングと処理のほうがメイン・スイッチ電流よりも簡単にできます。

インダクタ・ピーク電流を検出してメイン・スイッチ電流を求める代わりに、メイン・スイッチのオフ時間中にインダクタの谷をサンプリングします。谷電流検出はオン時間一定のトポロジーと組み合わせることでループ遅延を低減し、高速の過渡応答を実現できます。

Ray Ridley(「参考文献」の3)は、外部ランプが電流信号のダウンスロープに等しい、一定周波数制御の電流ループ・ゲインが、オン時間一定システムの電流ループ・ゲインと同一であることを証明しました。したがって、ループ・ゲインはオン時間一定の制御のデューティ・サイクルに対して不変であり、これによってすべての条件下で安定性が保証されます。これに対し、一定周波数ピーク電流制御では、ループ・ゲインがデューティ・サイクルに従って増加するため、外部ランプ時間が不足している場合に不安定な状態を引き起こす可能性があります。

オン時間が一定でオフ時間が可変のコンバータは、デューティ・サイクルが50%を超える固定周波数動作に伴う不安定性の問題を解決し、スロープ補償も必要ありません。負荷電流が増大しても、サイクル開始前とサイクル終了時の外乱は同じであるため、コンバータはデューティ・サイクルに無関係に安定した状態を保ちます。このアーキテクチャには固定されたクロックがないため、スロープ補償は不要です。

オン時間が一定の谷電流制御の大きな利点の1つは、降圧コンバータの短絡電流を制限できることです。降圧コンバータの出力が短絡し、ハイサイド・スイッチがオンになると、出力電圧は0になり、インダクタ両端の電圧はVINに等しくなります。インダクタ電流はtONの間に急速に上昇します。インダクタ放電時間tOFFはVOUT/Lで決まるため増大します。ここで、VOUT は事実上、短絡回路になります。ハイサイド・スイッチは、電流が所定の谷電流限界値まで低下するまでオンになりません。したがって、短絡状態では、この制御方式は一定の最大電流しか通しません。.