LTC2263-12

製造中12ビット、25Msps低消費電力デュアルADC

- 製品モデル

- 4

- 1Ku当たりの価格

- 最低価格:$18.37

製品の詳細

- 2チャネル同時サンプリングADC

- SNR:71dB

- SFDR:90dB

- 低消費電力:167mW/112mW/94mW(合計)

- 83mW/56mW/47mW(チャネル当たり)

- 単一1.8V 電源

- シリアルLVDS出力:チャネル当たり1ビットまたは2ビット

- 選択可能な入力範囲:1VP-P~2VP-P

- 800MHzのフルパワー帯域幅S/H

- シャットダウン・モードとナップ・モード

- 設定用のシリアルSPIポート

- ピン互換の14ビットおよび12ビット・バージョン

- 40ピン(6mm×6mm)QFNパッケージ

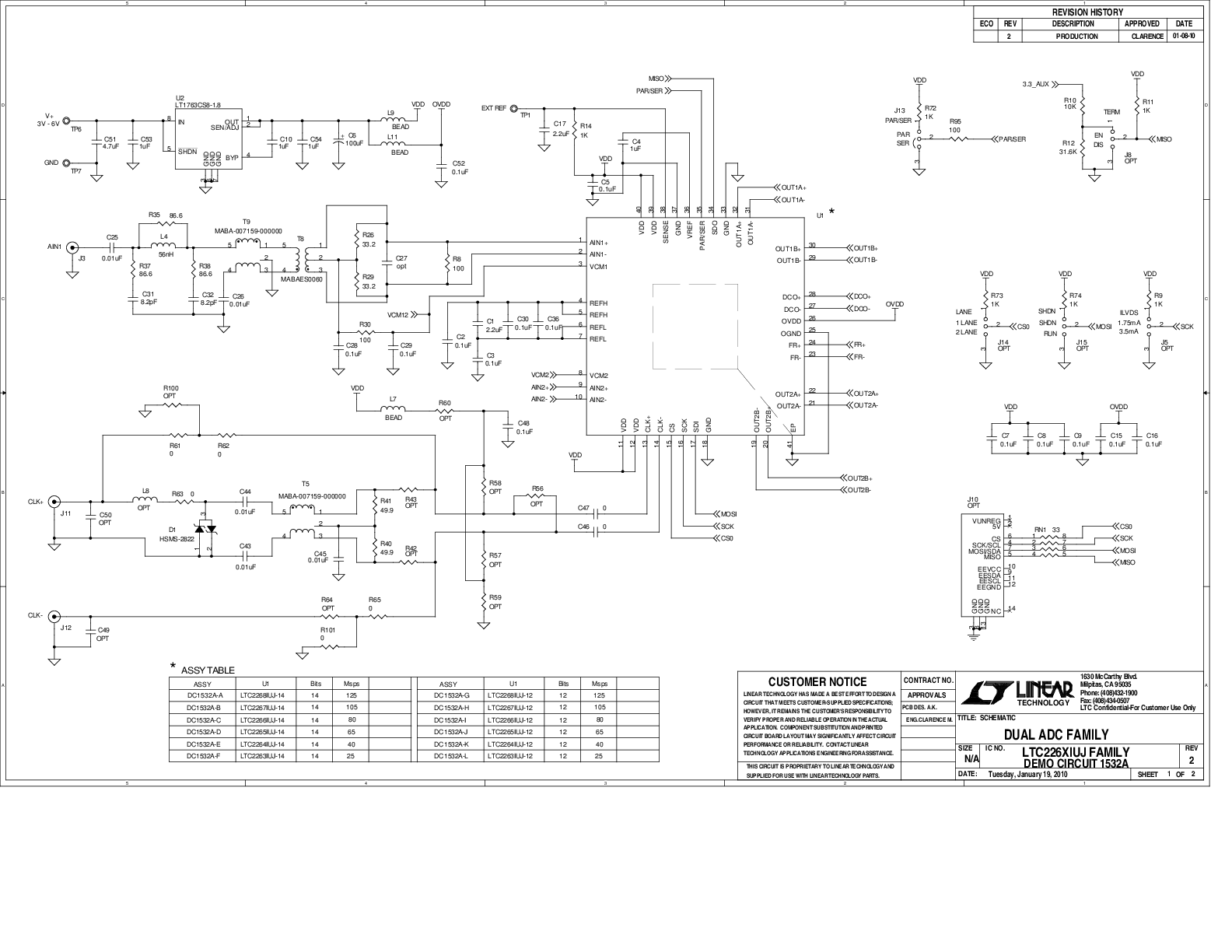

LTC2265-12/LTC2264-12/LTC2263-12は、広いダイナミック・レンジの高周波信号をデジタル化する2チャネル同時サンプリ ング12ビットA/Dコンバータです。SNRが71dB、SFDRが90dBという優れたAC特性を備えているため、要求の厳しい通信アプリケーションに 最適です。ジッタがわずか0.15psRMSなので、優れたノイズ性能を維持しながらIF周波数をアンダーサンプリングできます。

DC仕様では、±0.3LSB(標準)のINLと±0.1LSB(標準)のDNL、全温度範囲でミッシング・コードがないことが規定されています。遷移ノイズは0.3LSBRMSと低く抑えられています。

デジタル出力はシリアルLVDSなので、データ・ライン数を最小限に抑えることができます。各チャネルは一度に2ビット(2レーン・モード)または一度に 1ビット(1レーン・モード)を出力します。LVDSドライバはオプションの内部終端を備え、出力レベルを調整できるので、クリーンなシグナルインテグリ ティを確保します。

ENC+およびENC-入力は、正弦波、PECL、LVDS、TTLまたはCMOSの入力信号を使って差動またはシングルエンドで ドライブ可能です。また、内蔵のクロック・デューティサイクル・スタビライザにより、広範なクロック・デューティ・サイクルにおいてフルスピードで高性能 を達成できます。

| Bits | |

| LTC2263-12 | 12 |

| LTC2263-14 | 14 |

アプリケーション

- 通信

- セルラー基地局

- ソフトウェア無線

- 携帯型医療用画像処理

- マルチチャネル・データ収集

- 非破壊試験

ドキュメント

データシート 2

信頼性データ 1

ユーザ・ガイド 1

技術記事 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| LTC2263CUJ-12#PBF | 40-Lead QFN (6mm x 6mm x 0.75mm w/ EP) | ||

| LTC2263CUJ-12#TRPBF | 40-Lead QFN (6mm x 6mm x 0.75mm w/ EP) | ||

| LTC2263IUJ-12#PBF | 40-Lead QFN (6mm x 6mm x 0.75mm w/ EP) | ||

| LTC2263IUJ-12#TRPBF | 40-Lead QFN (6mm x 6mm x 0.75mm w/ EP) |

これは最新改訂バージョンのデータシートです。

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| インテジャー N PLL 1 | ||

| LTC6946 | 最終販売 | ノイズとスプリアスを極めて低く抑えたVCO内蔵の0.37GHz~5.7GHz整数分周方式シンセサイザ |