AD9142

新規設計には非推奨D/Aコンバータ、16ビット、1600MSPS、デュアル、TxDAC+

- 製品モデル

- 1

- 1Ku当たりの価格

- 価格は未定

Viewing:

製品の詳細

- 非常に小さな固有の遅延変動:

DACの2クロック・サイクル未満 - 独自の低スプリアス、低ひずみ設計:

6キャリアGSM ACLR=79dBc@200MHz IF、

SFDR>85dBc(帯域幅=300MHz)@ZIF - 柔軟な16ビットLVDSインターフェース:ワードとバイト負荷をサポート

- マルチ・チップの同期:

固定遅延とデータ生成遅延の補正

- 選択可能なインターポーレイション・フィルタ:2x、4x、8x、

低消費アーキテクチャ、fS/4の消費電力をセービングするコース・ミキサー - 入力信号のパワー検出:

ダウンストリームのアナログ回路保護のための緊急停止 - FIFOエラー検出

- 詳細はデータシートをご参照ください。

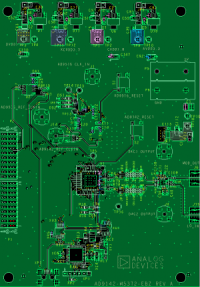

AD9124はデュアル、16ビット、高ダイナミックレンジのD/Aコンバータ(DAC)で最大のナイキスト周波数でマルチキャリアの発生が可能な1600MSPSのサンプルレートを提供します。AD9142 TXDAC+®は、ダイレクト・コンバージョン伝送アプリケーションに最適化されており、コンプレックス・デジタル変調、入力信号のパワー検出、およびゲイン、位相およびオフセット補正機能が含まれています。DAC出力は、アナログ・デバイセズのADL537x F-MODシリーズのようなアナログ直交変調器とシームレスにインターフェースできるように最適化されています。3線のシリアル・ポート・インターフェースは、多くの内部パラメータのプログラミング / リードバックに使われます。出力フルスケール電流は、9mA~33mAの範囲にわたってプログラムすることができます。AD9142は72ピンLFCSPパッケージを採用しています。

製品のハイライト

- 斬新な低スプリアスと低歪の設計技術は、ベースバンドから高中間周波数までの広帯域信号の高品質な合成を提供します。

- 非常に小さな固有の遅延変動は、システム内のソフトとハードウェア設計の両者を簡素化します。これによって、多くのアプリケーション用でのマルチ・チップの同期を容易にすることができます。

- 新しい低消費のアーキテクチャは、30%ほど電力効率(mW / MHz / チャンネル)を改善します。

- 入力信号のパワーおよびFIFOエラー検出は、ダウンストリームのアナログ回路保護の設計を簡素化します。

- プログラマブルな伝送可能な機能によって、電力の消費とウェークアップ時間の間のバランス設計を簡素化します。

アプリケーション

- ワイヤレス通信:3G / 4G、MC-GSMベースステーション、

ワイドバンド・リピータ、ソフトウェア無線 - ワイドバンド通信:ポイントtoポイント、LMDS / MMDS

- ダイバーシティ / MIMO送信

- 計測機器

- 自動テスト装置

ドキュメント

データシート 2

アプリケーション・ノート 1

技術記事 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD9142BCPZRL | 72-Lead Lead Frame Chip Scale Package |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

4 30, 2021 - 21_0053 Discontinuance of AD9142 |

||

| AD9142BCPZRL | 製造中止 | |

これは最新改訂バージョンのデータシートです。