概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- Allegro Layout Files

- Assembly Files

- Software Links

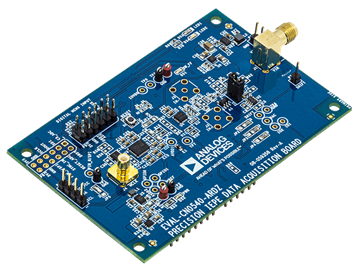

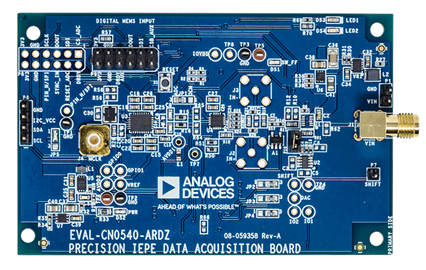

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0540-ARDZ ($176.55) IEPE Compatible, DC Coupled, Single Channel CbM Data Acquisition Measurement System

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

FPGA/HDL

機能と利点

- IEPE対応のデータ・アクイジション・システム

- 圧電センサーおよびMEMSセンサー

- 54kHzのアナログ入力帯域幅

- Arduinoフォーム・ファクタ互換

参考資料

-

CN0540 User Guide2020/09/14WIKI

-

ラピッド・プロトタイピングを実現するためのソリューション2024/04/15PDF4 M

-

CN0540: IEPE センサー用 24 ビットデータ・アクイジション・システム2020/09/14PDF888K

-

CN0549 状態基準保全 (CbM) 開発プラットフォーム2024/12/12

CN0549 状態基準保全 (CbM) 開発プラットフォーム2024/12/12 -

Easily Connect Sensors with ADI's Robust Industrial Signal Chains2024/12/12

Easily Connect Sensors with ADI's Robust Industrial Signal Chains2024/12/12 -

CN0549 - CbM Development Platform2024/12/12

-

堅牢性の高い産業用のシグナル・チェーン、センサーの接続がより容易に2024/12/12

堅牢性の高い産業用のシグナル・チェーン、センサーの接続がより容易に2024/12/12

-

状態基準保全システムには、なぜMEMS加速度センサーが最適なのか?2021/02/01

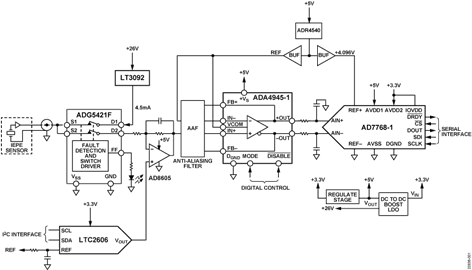

回路機能とその特長

図 1 に示すリファレンス設計は、高分解能、広帯域幅、高ダイナミック・レンジを特長とし、IC 圧電(ICP®)/集積化電子圧電型(IEPE)センサーとインターフェース接続する、IEPE 対応インターフェースのデータ・アクイジション(DAQ)システムです。最も一般的な IEPE センサーは、通常、振動測定アプリケーションで使用されますが、温度、歪み、衝撃、変位などのパラメータを測定する IEPE センサーも数多くあります。

この回路ノートでは、このソリューションを特に状態基準保全の領域で振動を扱うアプリケーションに適用する例に焦点を置いていますが、計測器や工業用オートメーションにおける広範なアプリケーションも、同様の方法で IEPE センサーを使用し、同様のシグナル・チェーンによって処理されています。

状態基準保全では、とりわけ、機械の状態の変化を予測する手助けとしてセンサー情報を使用しています。機械の状態を追跡する方法は数多くありますが、中でも振動解析は最も一般的に使用される手段です。振動解析データの時間変動を追跡することで、誤動作や故障をその原因と共に予測することができます。

工業環境での振動センシングには、堅牢で信頼性の高いセンシング手法が求められるため、更なる課題が伴います。機械の状態を知ることで、効率や生産性を高め、より安全な作業環境を作ることができます。

市販の圧電センサーとインターフェース接続するソリューションの大半は AC 結合で、DC やサブヘルツの計測機能がありません。このCN-0540 リファレンス設計は、DC およびサブヘルツの精度が実現できる DC 結合ソリューションです。

周波数ドメイン(DC~50kHz)の IEPE 振動センサーからの全データ・セットを調べ、その高速フーリエ変換(FFT)スペクトルに見られる高調波の位置、振幅、数を使用することで、機械の故障のタイプや原因をより正確に予測できます。

データ・アクイジション・ボードは Arduino 互換のフォーム・ファクタで、ほとんどの Arduino 互換開発ボードと直接インターフェース接続し、そこから給電できます。

回路説明

図 1 に示す回路は、IEPE センサー用のセンサーからビットまで(データ・アクイジション)のシグナル・チェーンで、電流源、D/A コンバータ(DAC)を使用したレベル・シフトおよび減衰段、3 次アンチエイリアシング・フィルタ、A/D コンバータ(ADC)ドライバ、完全差動 Σ-Δ ADC からなっています。

プログラマブル電流源は一定電流で圧電型加速度センサーを駆動します。出力電流は外部抵抗を使用して設定が可能で、その設定値はセンサーやケーブルのタイプにもよりますが、通常2mA~20mA です。

DAC のバッファ付き増幅出力は、レベル・シフト・オペアンプと共に、入力信号を 2.5Vのコモンモード電圧(VCOM)付近にシフトさせ、アンチエイリアシング・フィルタの入力と完全差動アンプ(FDA)の入力とのバランスを取ります。FDA レールの2 つめの入力は、電圧リファレンスによって VCOMである 2.5V に設定されて入力ヘッドルーム条件を確実に満たし、出力は、ADC を駆動するのに最適な完全差動となります。

アンチエイリアシング・フィルタはシグナル・チェーンの帯域幅を 54kHz に設定します。圧電型加速度センサーは 20kHz という広い帯域幅を持っていますが、位相遅延を考慮してこれより広い帯域幅のシグナル・チェーンが選択されているため、3 軸測定での位相マッチング性能が向上しています。(ADC のデジタル・フィルタでは更なる帯域幅制限が発生しますが、位相遅延は既知で確定的です。)

ICP/IEPE 加速度センサー

すべての IEPE 振動センサーは、オフセット電圧、ノイズ・レベル、帯域幅、感度が異なっていても同じ原理を用いて動作するため、この CN-0540リファレンス設計は、どの IEPE振動センサーにもインターフェース接続できます。IEPE の出力信号は ACと DCの両方の電圧を伴い、振動に依存するAC電圧は 7V~13Vの電圧レベルに DC シフトしています。この DC レベルはセンサーごとに異なり、またどのセンサーに対しても、時間、温度、励起電流に関するドリフト成分があります。

IEPE センサーは、センサーの振幅を完全にカバーできるだけの高い電圧範囲を持つ電流源で給電する必要があります。IEPE センサーの代表的な励起電圧は 24V です。シグナル・チェーンの入力では最大 10V p-p の信号振幅を最大13Vのオフセット電圧で受け取ることができます。この DCオフセットは DC オフセット補正信号を印加することで除去でき、動作の頻度を任意の低さにすることができます。

図 2 に ICP 加速度センサーのブロック図を示します。このセンサーは、定電流源から給電されており、DC 結合されたシグナル・チェーンに接続しています。センサーの最大帯域幅は励起電流に比例し、ケーブル容量に反比例します。定電流のレベルを選択する場合には、このセンサーとケーブルのタイプに必要な最大電圧を考慮する必要があり、次式を用いて定めることができます。

ここで、

fMAXはセンサーの最大周波数(Hz)、

ICは定電流値(mA)、

1mA はセンサーの電力条件、

C はケーブル容量(pF)、

V はセンサーからの最大ピーク電圧出力(V)です。

なお、式1において、1mAがセンサーに供給される総電流(IC)から差し引かれています。約 1mA はセンサー自体に給電されるもので、その他の電流はケーブルを駆動するために使われます。この数値はセンサーごとに異なります。

例えば、このリファレンス設計では、PCB Piezotronics 製 ICP 加速度センサーのモデル 333B52 を使用して試験を行っています。試験条件は、最大ピーク出力 10V、容量 29pF/ft のケーブル長10ft、励起電流 2.5mAです。式 1を適用すると、センサーの最大帯域幅の理論値は 82.3kHz となります。ケーブルも選択した電流レベルもセンサー性能の制限要因にはなりません。

定電流源

定電流源(CCS)を設計するとき、およびノイズ性能を検討するときには注意が必要です。シグナル・チェーンの入力インピーダンスを駆動する際には、電流ノイズが電圧ノイズに変換されるため、電流ノイズを低く抑えることが必須です。

図 3 は、2 端子の電流源を示したもので、抵抗 RSETと ROUTによって出力電流が 2.5mA に設定され、コンデンサ CSETによって電流ノイズの帯域幅が制限されています。LT3092 に内蔵された10µAのリファレンス電流源は、RSETの電圧を VSETに維持します。VSETは ROUTにミラーされ、式 2 に従って出力電流が定まります。

なお、実際の IOUT電流は式 2 で与えられる出力電流より 10µA だけ大きくなります。これは、SET 端子から流出する内部リファレンス電流が原因です。

データシートでは RSET を 20kΩ に設定し RSET での電圧低下を200mV とするよう推奨しています。これによりオフセット電圧の影響を抑制できます。(オフセット電圧の影響は VSET が小さいほど大きくなります。)抵抗が生成する電流ホワイト・ノイズは式 3 から求まります。

T は絶対温度(ケルビン)、

k は、ボルツマン定数(J/K)、

R は抵抗です。

抵抗の電流ノイズは抵抗値の逆数の平方根に比例し、RSET の値を推奨値である 20kΩ から 120kΩ に増加すると(出力電流を同じレベルに維持するため)これに比例して ROUT も増加する必要があるため、全体的なノイズ電流は低下します。RSET の電流ノイズと LT3092の内部電流リファレンスの電流ノイズを低減するために、コンデンサ CSETを RSETに並列接続することが推奨されます。コンデンサ CSETは、LT3092 から生じる電流ノイズをバイパスします。

図3に示す定電流源に対し LT spiceシミュレーションを実行し、各素子の値や配置依存性を最適化しました。2 つの出力を直列接続し合計 26V に設定した Keysight E3631 ベンチトップ電源を模し、20MHzの帯域幅内に0.7mV rms の電圧ノイズと 224nA rmsの電流ノイズを持つ非理想電圧源をモデル化しました。

表 1 に、素子の値を様々に組み合わせた場合の実効値ノイズを示します。実効値ノイズのシミュレーションは、1mHz~100kHz の帯域幅について行っています。CCOMP は、ハイパス・フィルタのように作用し、電圧源のノイズを出力に通過させます。RSET と ROUT を増加すると電流ノイズは減少しますが、抵抗での電圧低下も増大するため、許容可能な信号振幅が減少します。

| RMS Noise (nA) | RSET (kΩ) | ROUT (Ω) | CSET | CCOMP | |

| 158.8 | 20 | 80.6 | None1 | None1 | |

| 1273.5 | 20 | 80.6 | None1 | 100 nF | |

| 202.7 | 20 | 80.6 | None1 | 10 nF | |

| 15.5 | 20 | 80.6 | 100 nF | None1 | |

| 14.5 | 20 | 80.6 | 10 μF | None1 | |

| 3.1 | 120 | 470 | 10 μF | None1 | |

| 1 No Component Required. | |||||

インダクタンスの大きな長いケーブルを使用する場合は、安定性が問題となる可能性があります。誘導性負荷の補償についての詳細は、LT3092 のデータシートを参照してください。

電流源から供給される使用可能なセンサー励起電圧を計算するには、次式を使用します。

VDDは定電流源の供給電圧、

LT3092DROPは IC 自体のドロップアウト電圧(通常、最大 10mAの負荷電流時に 1.2V)です。

RSET × 10µA は、出力電流レベルを決める抵抗のドロップアウト電圧で、内部の 10µA の電流はこの抵抗を流れます。

この場合、使用できる励起電圧は 23.6V です。

電圧レベル・シフタ

電圧レベル・シフタは、最大 13V のセンサー・オフセット電圧と最大10V p-pの信号振幅を許容し、市販の大半の圧電センサーに適応できます。オペアンプを使用した反転電圧レベル・シフタ回路が選択されているため、FDA 段の入力条件に対応できるよう入力電圧を低下させるには、正のシフト電圧が必要です。

図 4 に、オペアンプを使用した反転レベル電圧レベル・シフタを示します。シフト電圧は次式を用いて計算します。

電圧シフタで生成される電圧VOUTは、できるだけVCOM(2.5V)に近い値となるように設定し、次段の FDA の入力とバランスを取ります。RF/RIN 比(オペアンプの減衰)は次の制約条件を満たす必要があります。

- シフト用オペアンプの電源電圧:5V

- シフト電圧の範囲:0V~5V

- オペアンプの安定性

- ADC のフルスケール・レンジ:±4.096V

- 入力信号の振幅:10V p-p

- 入力 DC オフセット電圧:13V

減衰として0.3という値は、妥当な選択です。次段のゲインが小さいことで、ADC の入力振幅を最大限にすることができ、S/N比(SNR)が増大します。レベル・シフタの出力では信号とノイズのどちらも増幅されるため、レベル・シフタの出力ノイズを最小化することが重要である点に注意してください。

CN-0540 では、入力インピーダンスと入力ノイズの間で一定の妥協が行われており、測定誤差が生じないよう、入力ノイズ・レベルを低く、入力抵抗を高くしています。圧電センサーは一般的に低インピーダンス出力(数百 Ω)のセンサーであり、比較的低入力インピーダンスのシグナル・チェーン(数十 kΩ)でも生成される誤差は 1%未満です。妥協点として、最終的にRIN = 50kΩ という入力インピーダンスが選択されています。

次式を用いると、入力を短絡したレベル・シフタ・ブロックの電圧ノイズを計算できます。

ここで、抵抗からのノイズの寄与は次式で計算できます。

k はボルツマン定数、

T は絶対温度(ケルビン)、

R は抵抗(Ω)です。

RIN を除くすべての寄与分は、平方する前にノイズ・ゲインを乗じる必要があります。反転オペアンプ構成のノイズ・ゲインは、非反転構成の場合と同じです。

ここで、NG は回路のノイズ・ゲインです。

電圧レベル・シフタ・ブロックでの単極RCフィルタによって、ノイズは制限されます。電圧レベル・シフタで発生するノイズの実効値を計算するには、次式を用います。

DC バイアス補償技術

IEPE 加速度センサーにはそれぞれ、一定量の除去すべき DC バイアス電圧があります。この電圧は何ら有用な情報を伝達しないためです。シグナル・チェーンで DC 結合が用いられている場合、DC バイアス電圧を打ち消すよう入力電圧を DC シフトできます。それによりADCはDCオフセットのない入力電圧のAC成分のみを認識できます。DC 測定の精度を確保し、測定のダイナミック・レンジを最大限にするためには、DC シフトが正確であることが重要です。

式 5 のシフト電圧を用いると正確なシフト電圧を求めることができます。この手法に従うと、各ボードやセンサーごとに、様々な温度で多数の測定を行うことが必要です。それによって測定の精度が確保されます。

ここでは、より正確で信頼度が高く、自動化された別の方法が用いられています。すなわち、CN-0540ではカスタマイズした逐次比較アルゴリズムを用いています。標準的な逐次比較モデルは、DACからADCへの制御ループを使用して未知の電圧レベルの最終位置を推定しているため、このカスタム逐次比較では、DACからADCへのループを使用してADCの入力での平均電圧をできるだけ0に近い値に設定しようとします。言い換えると、主な目標は、FDAの両方の入力を同じ電圧レベル、すなわち、VCOM = 2.5Vに設定することです。

| Iteration | DAC Code | Next Move | Mean Voltage (mV) |

| 1 | 32,767 | Up | +4095.99 |

| 2 | 49,151 | Up | +1812.92 |

| 3 | 57,343 | Down | -339.57 |

| 4 | 53,247 | Up | +735.69 |

| ... | ... | ... | ... |

| 15 | 56,049 | Down | -0.366 |

| 16 | 56,048 | Final | -0.097 |

表 2 に、逐次比較アルゴリズムを使用した入力バイアス電圧補償のプロセスを示します。16ビットの DACを選択したため、繰返し(イテレーション)は 16 回行っています。プロセスの最初の段階では、DAC はハーフスケール出力に設定されています。DAC が新しい値に設定されるたび、平均電圧を測定します。平均電圧が正の場合は、1 ビットの重みが現在の DAC 出力に加えられます。負の場合は、1 ビットの重みが現在の DAC 出力から差し引かれます。このプロセスが反転しているのは、入力オペアンプが反転構成であるためです。

式 11 は、ビットの重み付けが加えられた場合や差し引かれた場合を示しています。215 − 1 は、初期のハーフスケール値で、その後に 2 つのアップと 1 つのダウンが続いています。つまり、14番目と13番目のビットが加わり、12番目のビットが差し引かれています。

圧電センサー自体は、センサーの内部構造に起因して、かなりの量の電圧ノイズを発生します。センサーに電力が供給されると、センサーは常に周囲のノイズの影響を受けるため、電圧ノイズは機械的な環境イベントからの変換により更に増加することになります。圧電センサーの DC バイアス電圧のみを差し引き、ノイズの大部分を(ランダムか周期的かを問わず)除去するため、この DC バイアス補償プロセスにおいて多数の平均化処理が行われています。

レベル・シフト DAC

レベル・シフトを行うために、27 の選択可能な I2C アドレスを持つ 16ビット電圧出力 DAC(LTC2606)を選択しました。このDAC は 4.096V のリファレンスを ADC と共有します。シフト用オペアンプの非反転入力にプリセットされた 0V~5V のシフト電圧範囲をすべてカバーし、DAC の出力電圧ノイズを低減するために、外部バッファが追加されています。バッファはサレンキー構造で、カットオフ周波数が 100Hz、ゲインが 1.22 です。出力ゲインのある DAC の LSB は、

ここで、2.667 は FDA のゲイン、1.3 はシフト用オペアンプのゲインです。このオペアンプは変動する信号が非反転入力に入力されたときに非反転オペアンプのように動作し、実際のゲインは 1 + (RF/RIN)です。式 13 を計算すると、センサーを適切なレベルにシフトさせたことによる DC 誤差の理論上の最大値が求まります。

表 2 は、ADCが変換する DACの 1LSBは、約 264µVであることを示しています。最後の 2 つの ADC の読み取り値を見ると、差はわずか 1LSB で 269µV となっています。

図 5 は、実効値ノイズがシグナル・チェーンの入力に印加された入力バイアス電圧のみに応じて変化する様子を示しています。入力バイアスが変化するたびに、DAC は入力を適切なレベルにシフトし、オフセット誤差が確実に小さくなるようにします。シグナル・チェーンの実効値ノイズは DC バイアスと共に増加します。電圧出力レベルが高くなると、DC バイアスをもたらすDC キャリブレータがより多くのノイズを発生するためです。

図 5 から予想されるように、ダイナミック・レンジは、入力バイアス電圧の増加に伴う実効値ノイズの増加に応答します(図6 参照)。

図 7 は、入力信号の周波数が 1kHz、振幅が 1V p-p の場合の、システムと入力バイアス電圧の直線性を示すものです。この図から、入力バイアス電圧は直線性には大きな影響を与えることはなく、全高調波歪み(THD)は安定していることがわかります。

図 8 に、ADC の入力にプリセットされたオフセット電圧誤差と温度の関係を示します。オフセット誤差は、入力電圧を一定(10V)にし、この温度範囲で入力バイアス電圧補償を実行することで求まります。25ºC でオフセット誤差が 0V となるよう設定しました。

図 1 に示すように、出力電圧が 2.5V の電圧リファレンス・チップ(ADR441A)を用い、安定した VCOM を確保しています。このリファレンス IC は温度ドリフトが大きく、−25ºC~+85ºCの範囲で 2.75mV です。この変化に(FDA の)ゲイン 2.667 が乗じられ、ADC が検出する合計温度ドリフトは 7.33mV になりますが、これはその後の DAC で補償されます。

入力電圧または VCOM が変化するごとに(VCOM は温度ドリフトによってのみ変化します)、DAC はこの変化を逆方向に補償します。この場合、VCOM だけが変化し、入力バイアスは一定です。ADR441A は、図 8 に見られるような、ADR441A の電圧ドリフト曲線とは逆の形状を持つ電圧ドリフトで効果を発揮します。仕様規定された温度範囲内でのコードの総変化量は 32LSB です。

DAC バッファ

DAC の内部バッファは電圧ノイズを制限するもので、フィルタ処理が必要です。また、DAC は ADC と 4.096V のリファレンスを共有するため、0V~5V の電圧を供給できるよう DAC 出力を増幅する必要もあります。

図 9 は、ロー・パス・サレンキー・フィルタ構造を使用し、出力ゲインのあるレベル・シフト DAC を示します。フィルタのカットオフ周波数は、次式を用いて約 100Hz という低い値に設定されています。

DAC シフト・ブロックのノイズ性能を、バッファがある場合とない場合で比較しました。なお、この測定で用いたシグナル・チェーンは、入力短絡時のノイズが 12.3µV rms、ダイナミック・レンジが 108.2dB です。実効値ノイズは、64kHzの帯域幅で測定しました。

表 3 に、出力電圧が DAC コードに応じて変化する様子を示します。DAC出力は、ゼロ・スケールから、1/4スケール、ハーフスケール、3/4 スケールまで設定されています。最も厳しいシナリオで、DAC シフト・ブロックのノイズの寄与分はわずか 1.3µVrms です。

| DAC Code | Without Buffer | With Buffer | ||

| Noise | Dynamic Range | Noise | Dynamic Range | |

| 0x0000 | 12.71 μV rms | 107.3 dB | 13.1 μV rms | 107.5 dB |

| 0x3FFF | 24.52 μV rms | 101.9 dB | 13.4 μV rms | 107.2 dB |

| 0x7FFF | 25.21 μV rms | 101.1 dB | 13.6 μV rms | 107.5 dB |

| 0x9FFF | 26.39 μV rms | 101.2 dB | 13.6 μV rms | 107.3 dB |

アンチエイリアシング・フィルタと FDA

アンチエイリアシング・フィルタと FDA は、シングルエンド信号から差動信号への変換を行う差動多段フィードバック・ローパス構造を採用しています。アンチエイリアシング・フィルタのカットオフ周波数は 54kHz に設定されています。これは大部分の圧電型加速度センサーの帯域幅より広い値です。このフィルタは 2.3MHzで−80dBのストップバンド除去性能を持っています。

この段のゲインは 2.667 に設定されており、入力振幅を ADC の入力において±VREF範囲に近付くよう増幅して SNR を向上させます。広帯域ノイズも FDA によって増幅されますが、この悪化は信号ゲインによる改善に比較すると大きなものではありません。アンチエイリアシング・フィルタが広帯域ノイズを抑制するためです。

A/D 変換

DC~204kHz の帯域幅での精度が優れ、低消費電力、108.5dB(代表値)のダイナミック・レンジ、−120dB の THD といった特長を持つことから、高精度 1 チャンネル 24 ビットの Σ-Δ ADCである AD7768-1 を選択しました。

ADCの出力データ・レートを計算するには、式17を用います。

MCLK はマスタ・クロック、

MCLKDIVはマスタ・クロック分周器係数、

FILTEROSRは選択したデジタル・フィルタのオーバーサンプリング比(OSR)です。

クロック分周器とフィルタの OSR はレジスタ設定値で、SPI バスを介して変更できます。FIR(有限インパルス応答)フィルタと SINC5 フィルタの OSR は AD7768-1 のレジスタ・マップで厳密に設定されます。次式を用いて 12 ビット SINC3 デシメーション・レート・レジスタに指定値を書き込むことで、SINC3 フィルタを独自の OSR に設定し出力データ・レートを変更することができます。

このリファレンス設計のデフォルト設定値は、以下に示すように、ADC 測定帯域幅が 32kHz の場合に対して最適化されています。

- 電力モード:低消費電力モード

- MCLK 分周器:16

- フィルタ・タイプ:FIR

- フィルタ・デシメーション・レシオ:32

- 入力プリチャージ・バッファ:イネーブル

- リファレンス・バッファ:プリチャージ・イネーブル

- VCM ピン出力: (AVDD1 − AVSS)/2

- 変換長:24 ビット

- 変換モード:連続

- チェックサム:チェックサムなし

- データ読出しモード:連続

- ステータス・ビット:ディスエーブル

- DRDY 信号:イネーブル

低消費電力が求められるアプリケーションを対象にする場合は、両バッファをオフにします。ただし、バッファをオンに維持しておくと、全体的な THD と SNR は改善します。

| ADC Power Mode | MCLK Ratio | Filter Type | Filter Decimation Rate | ODR (kSPS) | -3 dB Bandwidth (kHz) | RMS Noise (μV) |

| Fast | 2 | FIR | 32 | 256 | 110.8 | 10.98 |

| Medium | 4 | FIR | 32 | 128 | 55.4 | 10.94 |

| Medium | 8 | FIR | 64 | 64 | 27.7 | 7.37 |

| Low | 16 | FIR | 32 | 32 | 13.9 | 10.84 |

| Low | 16 | FIR | 1024 | 1 | 0.43 | 1.76 |

| Condition | MCLK/161 | MCLK/81 | |||

| Dynamic Range (dB) | Noise (μV rms) | Dynamic Range (dB) | Noise (μV rms) | ||

| DC-Coupled, CCS Enabled | |||||

| Shorted Input | 105.9 | 23.8 | 104.6 | 24.2 | |

| 1 kΩ at Input | 100.8 | 33.2 | 98.4 | 39.2 | |

| DC-Coupled, CCS Enabled | |||||

| Shorted Input | 105.7 | 21.3 | 105.4 | 22.1 | |

| 1 kΩ at Input | 105.9 | 22.2 | 105.2 | 22.1 | |

| 1 Low ripple FIR filter bandwidth = 0.433 x ODR. | |||||

シグナル・チェーン性能の測定結果

このシグナル・チェーン設計では、中程度の帯域幅から広帯域幅の範囲の振動センシングを対象にしており、高次の高調波や1kHz を超える周波数成分が重要となります。設計においては、システム帯域幅、直線性、実現可能なノイズ性能の間でトレードオフが必要となります。高いインピーダンスを選択した方が、信号精度(直線性)を維持できます。それによってこの設計では最大ノイズ性能制限が設定されます。信号の帯域幅も広く設定した方が、高周波数でのシステム応答が維持できます。低ノイズ・ソリューションは、帯域幅を狭くして広帯域ノイズをより多く除去するようにした設計で実現できます。

CN-0540 ではアナログ入力の帯域幅を 54kHz に設定していますが、実際の信号帯域幅は ADC の構成設定値によって決まります。

ノイズ

シグナル・チェーン全体のノイズ性能は、いくつかの異なる状況で測定されます。

表 5 は、センサーを接続しない場合と 1kΩ の負荷抵抗を接続した場合でのシグナル・チェーンの代表的なノイズ性能を詳しく示したものです。シグナル・チェーンの入力に 1kΩ の抵抗を接続した場合の結果は、定電流源がノイズ性能に影響することを示しています。電流ノイズは電圧ノイズに変換され、1kΩ の抵抗によって増幅されてシステム・ノイズを増大させます。

図 10 は、入力短絡時のシステムの代表的な FFT プロットを示したものです。また、図 11 は、入力短絡時の DC 結合ソリューションのダイナミック・レンジと温度の関係を示したものです。

センサーのノイズの寄与

データ・アクイジション・システムの設計者の目標は、通常、センサーの出力信号をできる限り正確に取得することです。このことは、現実には、システム性能の設定はセンサーの特性によって決まる、ということを意味します。センサーのノイズ性能は、測定システム全体の主要制限要因の 1 つであることが多く、このことを理解しておくと設計の性能条件を設定しやすくなります。

この設計では、1kHz より広い帯域幅で振動データを提供するセンサーに対応することを目的としています。このようなセンサーは、回転運動または往復運動をするプラント設備の予防的メンテナンスのための状態基準保全を目標にした、データ・アクイジション・システムで使用されています。

表 6 に、振動センサーの選択例の一部について、性能レベルと帯域幅をまとめます。センサーを選択する際の主な考慮事項は、多くの場合、帯域幅、範囲、ノイズ・スペクトル密度(NSD)、消費電力です。

ADXL1002 センサーおよび ADXL1004 センサーは、消費電力と帯域幅が重要となる広範な振動アプリケーションに最適な、低消費電力デバイスです。これらの加速度センサーは、モノのインターネット(IoT)でのマシン・モニタリングなど、連続モニタリング・アプリケーションに適しています。

| Sensor | Range (±g) | Output Range Peak-to-Peak (V) | Linearity (±%FSR) | NSD (μg/√Hz) | Flat Bandwidth (kHz) | Noise at Flat Bandwidth (μg rms) |

Dynamic Range at Flat Bandwidth (dB) |

| ADXL1002 | 50 | 4 | 0.1 | 25 | 11 | 2622 | 82.60 |

| ADXL1004 | 500 | 4 | 0.25 | 125 | 24 | 19365 | 85.23 |

| PCB 621B40 | 500 | 10 | 1 | 10 | 30 | 1732 | 104.95 |

| PCB 352C04 | 500 | 10 | 1 | 4 | 10 | 400 | 118.93 |

| PCB 333B52 | 5 | 10 | 1 | 0.4 | 3 | 22 | 98.50 |

高周波数での低ノイズ性能と感度が重要な要素となるような、高い感度と帯域幅が要求されるアプリケーションでは、圧電センサーは依然として最も使用に適したセンサーです。AD7768-1は帯域幅が広く低ノイズの性能を持っているため、このシグナル・チェーンは、10kHz を超える広い帯域幅範囲での代表的なセンサーの性能レベルに対応できるようになっています。

CN-0540 の場合、システム帯域幅は 54kHz に設定されており、シグナル・チェーンのノイズ性能は、この帯域幅にわたって100dB を超えるダイナミック・レンジを実現できるセンサーを対象としています。例えば、PCB Piezotronics の Model 621B40 加速度センサーで、このデバイスは、30kHz でほぼ 105dB を実現します。

この回路を応用すると、抵抗値と各段のゲインを増加し、AD7768-1 のオーバーサンプリング・モードを高くすることで、ダイナミック・レンジがより高く帯域幅がより狭いセンサーに使用できます。詳細な解析は本稿の範囲を超えますが、オーバーサンプリングを使用した場合のダイナミック・レンジと帯域幅のトレードオフの詳細については、AD7768-1 のデータシートに記載されています。

直線性

センサー計測システムの直線性は、センサーの出力に変動があっても測定結果は変わらないという信頼を与えるうえで重要です。センサーの出力バイアス電圧や信号振幅が変化しても、計測システムの精度が変動することがあってはなりません。理想的には、この精度は計測システムの温度が変化しても維持される必要があります。

CN-0540 はできる限り直線性が高く、しかも温度に対してその直線性が維持されるよう設計されているため、シグナル・チェーン測定でのキャリブレーションの必要性は低減します。DC 入力電圧変動に対するシステムの非直線性は、INL 誤差として表れます。サイン波入力に対するシステムの非直線性は、THD 誤差として表れます。

図 12 および図 13 に示すデータは、幅広い入力電圧範囲にわたって DC 直線性(INL)が±10ppm以内であり、INLと THDは共に広い温度範囲にわたり比較的平坦であることを示しています。

AC 結合ソリューションとDC 結合ソリューションの比較

CN-0540 は、DC 結合のアプリケーションで使用される状況を対象としています。この場合、信号の DC 成分が保存されるか、システムの応答が 1Hz 以下の周波数まで維持される必要があります。そのため、システムは IEPE センサーの大きな DC バイアスを処理できるよう設計されています。

ただし、システムによっては、DC までの応答を必要としない場合もあり、そのような状況では AC 結合の入力チャンネルが使用できます。

この 2 つのソリューションの主な違いは、シグナル・チェーンの複雑さと DC および低周波数での精度です。AC 結合ソリューションの方が複雑さは軽減しますが、低周波数での精度がありません。

カップリング・コンデンサを入力抵抗と直列に挿入することで、この設計を AC 結合設計に適応させることができます。詳細については、設計サポート・パッケージにある回路図ファイルを参照してください。

カップリング・コンデンサを挿入することは、入力応答を、極周波数が通常 10Hz よりかなり低い値に選択されるハイパス応答に変化させる効果があります。このフィルタは DC バイアス電流をブロックするだけでなく、1/f ノイズの一部も除去します。AC 結合システムのダイナミック・レンジは DC 結合システムより高くなるように見えますが、これは低周波数ノイズが除去されたために過ぎません。このトレードオフは、低周波数振動測定データに対する感度を低下させることの代償として生じます。

DC 結合ソリューションでは、DAC 出力のため、また、シグナル・チェーンの入力にハイパス・フィルタがないため、ノイズが高くなることも予想されます。図 14 は、ハイパス・カットオフ周波数を 1Hzとした AC結合の場合の、CN-0540の応答を示します。測定は、シグナル・チェーンの入力を短絡し、イネーブルされた定電流源を使用して行いました。DC 結合の測定に従い、ADC は低消費電力モード、MCLK/16、FIR フィルタのデシメーションは 32 に設定しています。

AC 結合ソリューションを実行する場合、最高性能を発揮するには適切なタイプのコンデンサを選択する必要があります。一般的にセラミック・コンデンサは、圧電効果によるノイズ発生の影響と、電圧係数(印加電圧に対する比誘電率の変化)および誘電吸収による非直線性の影響を受けます。タンタル・コンデンサは、妥当な性能を備え、数百 µF にまでおよぶ幅広い範囲の値のものが製造されています。AC 結合の場合でのタンタル・コンデンサは、DC 結合システムと同レベルの THD 性能を実現しますが、これが可能なのは 10Hz より高い周波数の場合に限ります。より低周波数の振動を正確に測定するには、DC 結合の方が適しています。

システム電力

CN-0540 は、シグナル・チェーンすべてを 3.3V 単電源レールから給電できる、最適な電力ソリューションを備えています。

電力ソリューション

図 15 は、CN-0540 の電力セクションを簡略化したブロック図です。マイクロコントローラとの互換性やArduinoスタイルの接続ができるその他の開発ボードとの互換性を維持するため、このボードの電力ソリューションは、通常Arduino互換ボードで提供される 3.3V 単電源で駆動できるよう設計されています。

システムの安定性を確保するため、マイクロコントローラ・ボードは、3.3V 電源を通じて少なくとも 250mAを振動モニタリング・ボードに供給できる必要があります。これは、マイクロコントローラ・ボード自体がこの電源から供給を受ける電源電流以外の部分です。

CN-0540 評価用ボードの定常状態の動作では 250mA は必要ではありませんが、最初のパワーアップ・フェーズの間、最大 30ms間、200mA 以上の突入電流が発生する可能性があります。マイクロコントローラ・ボードがこの電流に耐えられない場合、マイクロコントローラ・ボードがリセットされる可能性があります。予期せぬリセットが発生した場合は、マイクロコントローラ・ボードの電流出力仕様を確認してください。

電力セクションは、3.3V ドメイン、5V ドメイン、26V ドメインの 3 つの電圧ドメインで構成されています。また、IEPE センサー用に 2.5mA 電流源も含まれています。

Arduino 互換ボードでは CN-0540 が直接使用する IOREF 電源を備えているため、電力ソリューションは不要です。IOREF は、AD7768-1(IOVDD)にデジタル・インターフェース電源を提供し、16.384MHz のマスタ・クロック源に電力を供給します。

CN-0540 は、1.8V という低電圧までの IOREF 電圧と互換性があり、そのため、CN-0540 ボードは、低ロジック・レベルのマイクロコントローラ・ボードとインターフェース接続できます。

提供する電力ソリューション回路の目的は、CN-0540 ボードが、マイクロコントローラ・ボードに通常備わっている低電圧単電源で駆動でき、この 1 つの電源から必要な電圧レールを生成することができるようにすることです。CN-0540 では、3.3V 入力電源レールをそのまま直接使用して、AD7768-1(AVDD2 電源)にデジタル・インターフェース・ロジック電源を供給すると共に、電圧を 5V から 26V に昇圧する DC/DC 段にも電力を供給しています。

最初の DC/DC 段では 3.3V から 7V に昇圧し、次に LTC3459 デバイスと ADP7118 デバイスを組み合わせて 5V にレギュレーションして、AD7768-1、LTC2606、ADR4540 リファレンスおよび関連のアンプ段が必要とする、ノイズのない電源レールを提供しています。

次の DC/DC 段では、3.3V から 28V に昇圧し、LT3494 デバイスと LT3008デバイスを組み合わせてこれを26Vにレギュレーションしています。このノイズのない 26V レールは、IEPE センサーに最大 26V で 2.5mA を供給する LT3092 電流源の電源として、必要となります。

電力測定

電力測定は、3.3V 電源レールおよび IOREF 電源レールから直接行われます。そのため、電力測定には、電力ソリューションの部品自体の寄与も含まれます。

26V レールへの電流は定電流源を使用するため一定で、ADC 設定には無関係です。

システムの残りの部分の消費電力は、ADC の別の動作モードで測定しました。1kΩ の負荷抵抗をシグナル・チェーンの入力に配置することで、定電流源からの電流経路が可能となり、AD8605 の入力での DC バイアスを維持できます。

消費電力

ADC のレジスタ設定のうち、消費電力に影響する最も重要なものは以下のとおりです。

- 消費電力モード

- MCLK 分周器

- MCLK 周波数

- フィルタ・タイプ

- フィルタのデシメーション・レシオ

- VCM ピン出力分圧器

- アナログ入力プリチャージ・バッファ

- リファレンス・バッファ

- 汎用入出力(GPIO)

システムのデフォルト設定

狭帯域幅測定用システムのデフォルト設定では、ADC は次のように設定されています。

- MCLK 分周器:MCLK/16

- 電力モード:低消費電力モード

- FIR フィルタ:32 を超えるデシメーション・レート

- VCM ピン出力:(AVSS − AVDD)/2

- リファレンス(REF)バッファ:プリチャージ・オン

- アナログ入力(AIN)バッファ:プリチャージ・オン

- MCLK 周波数 = 16.384MHz

- FDA はイネーブル、低消費電力モード

- DAC バッファはイネーブル

- DAC 出力:ハーフスケール

このシステムのデフォルト設定は、このリファレンス設計に含まれているほとんどの測定で用いられています。

| ADC Power Mode | ADC Data Rate (kSPS) | 3.3 V Rail (mA) | IOREF (mA) | Total Current (mA) | |

| Fast1 | 256 | 74 | 9 | 83 | |

| Median2 | 128 | 58 | 4 | 62 | |

| Low2 | 32 | 50 | 1 | 51 | |

| 1 FDA in full power mode. | |||||

| 2 FDA in low power mode. | |||||

AD7768-1 のアナログ入力バッファとリファレンス入力バッファは、プリチャージ・モードに設定され、ADA4945-1 FDA は低消費電力モードに設定されています。FDA は、通常消費電力モードの方が帯域幅が広く、直線性能も優れていますが、この設計で対象とする帯域幅は 50kHz 未満であるため、低消費電力モードで十分です。AD7768-1 の内部プリチャージ・バッファをイネーブルすることで、システムの消費電力が大幅に増加することなく、直線性とノイズ性能を向上できます。AD7768ファミリでのドライバ・アンプのマッチングと入力バッファ・オプションの使用についての詳細は、アプリケーション・ノート AN-1384を参照してください。

バリエーション回路

より多チャンネルのシステムでは、AD7768-1 に代わり、マルチチャンネルの AD7768 および AD7768-4 が適しています。これらのデバイスは、ADC のノイズと直線性は AD7768-1 と同等ですが、単一チップで最大 8 チャンネルを同時に使用できる利点があります。そのため、マルチチャンネルの IEPE DAQ 設計を容易に実行できる可能性があります。

振動や状態監視のシグナル・チェーンに対して検討すべき ADCとしてはこの他に、AD4000、AD4002、AD7380 があります。

ADA4610-1 は、初段のシグナル・コンディショニングでの使用やレベル・シフトに適していますが、適切な動作のためには高い電源電圧が必要です。ADA4807-1 と ADA4940-1 は、ADC の入力アンチエイリアシング・フィルタおよびドライバ段での代替デバイスです。

ADAQ7980/ADAQ7988 は、最も重要なパッシブ・コンポーネントの他 ADC と ADC ドライバ段をシステム・イン・パッケージ(SiP)設計で集積した、16 ビットの ADC µModule®データ・アクイジション・システムです。これらのデバイスは、実装のサイズや簡便さが重要となるような場合に推奨されます。

このように様々なオプションがあるため、性能(ノイズや直線性)、ソリューション・サイズ、コストに基づき、シグナル・チェーン・コンポーネントを選択することができます。

回路の評価とテスト

以下のセクションでは、CN-0540 回路設計のテスト手順と結果の収集について概説します。ハードウェアとソフトウェアのセットアップの詳細については、CN-0540 ユーザ・ガイドを参照してください。

必要な装置

以下の装置類が必要になります。

- EVAL-CN0540-ARDZ リファレンス設計ボード

- Terasic DE10-Nano FPGA

- CN-0540 リファレンス・ソフトウェアを伴う FPGA Linuxイメージ

- High-Definition Multimedia Interface(HDMI®)ポートを備えたモニタ

- HDMI - HDMI ケーブル

- USB ドングル付きのワイヤレス・キーボードおよびマウス

- USB On-the-Go(OTG)ケーブル(micro USB - USB)

- 高精度 AC 電源(AP2700、Brüel & Kjær、または同等のサイン波発生器など)

- Bayonet Neill–Concelman(BNC)端子および Subminiature Version A(SMA)端子付きの同軸ケーブル

開始にあたって

基本的なテスト・セットアップには EVAL-CN0540-ARDZ ボードをサポートされる FPGA キャリア・ボードに差し込む必要があります。キャリア・ボードは、EVAL-CN0540-ARDZボードへの給電、組み込み Linux イメージの実行、データの取得、データの表示を行う必要があります。Terasic DE10-Nano および類似の Arduino 互換FPGAキャリア・ボードをサポートするソフトウェアは、アナログ・デバイセズの Web サイトから入手できます。

ボードの基本機能をテストするには、高精度高品質のサイン波発生器または任意波形発生器を、EVAL-CN0540-ARDZボードのアナログ入力コネクタに接続します。

手順は次のとおりです。

- 図 18に示すように、EVAL-CN0540-ARDZ 評価用ボードをArduino ヘッダに差し込んで、キャリア・ボード(Terasic DE10-Nano)にマウントします。

18. Terasic DE10-Nano Carrier Board にマウントされたEVAL-CN0540-ARDZ -

図 19. CN-0540 アナログ入力コネクタに接続された同軸ケーブルを示す拡大図 - アナログ・デバイセズの FPGA Linux イメージを microSDカードに読み込みます。

- CN-0540 とキャリア・ボードの両方に対して適切なファイルを使用するよう microSD カードを設定します。

- Terasic DE10-Nano からモニタに HDMI ケーブルを接続します。

- USB OTG ケーブルを Terasic DE10-Nano の micro USB ポートに接続し、ワイヤレス・マウス/キーボード用の USB ドングルを挿入します。

- 用意した電源を使用してバレル・ジャックを DE10-Nano に接続し、Terasic DE10-Nano の電源スイッチをオンにします。

- サイン波発生器または任意波形発生器を次のようにオンします。

- 信号タイプをサイン波に設定します。

- レベルを 1kHz で 1V p-p に設定します。

- 出力をイネーブルにします。

- ソフトウェアを実行し、その結果出力される ADC データおよび FFT データを取得します。

図 20 と図 21 の 2 つのプロットは、キャリア・カードを手順 1 から手順 9 に説明したように設定した場合に予想される代表的な取得データを示したものです。図20は、ADCキャプチャ・データの時間領域の表示で、サンプル数全域にわたって予想された振幅が示されています。

図 21 は、同じデータを周波数領域の FFT プロットとして処理し表示したものです。

ハードウェアとソフトウェアのセットアップの詳細については、CN-0540 ユーザ・ガイドを参照してください。

圧電型加速度センサーの結果

妥当なノイズ測定を実現するためには、圧電型加速度センサーはアクティブな振動台を使用して周囲の振動を打ち消して安定化させるか、重量のある物体に固定し周囲からの振動の影響を軽減する必要があります。圧電型加速度センサーをシグナル・チェーンの入力に直接接続する場合は、重量物に固定する方法を採用しました。使用した加速度センサーは、PCB Piezotronicsの Model 333B52 センサー(3kHz)です。

図 22 に、センサーが接続されている間に取得した FFT の相対的な性能プロットです。システムのノイズはセンサー信号が支配的となっています。

I2C は、Philips Semiconductors 社(現在の NXP Semiconductors 社)が独自に開発した通信プロトコルです。