AD9681

推荐新设计使用8通道、14位、125 MSPS串行LVDS 1.8 V模数转换器

- 产品模型

- 2

产品详情

- 低功耗,8个ADC通道集成到一个封装中,每通道110 mW(125 MSPS,功率选项可调整)

- SNR:74 dBFS(至奈奎斯特频率);SFDR:90 dBc(至奈奎斯特频率)

- DNL:±0.8 LSB(典型值);INL:±1.2 LSB(典型值)

- 70 MHz、−1 dBFS最差情况下的邻道串扰:-83 dB(典型值)

- 串行LVDS(ANSI-644,默认)

- 低功耗,减少信号选项(类似于IEEE 1596.3)

- 数据时钟输出和帧时钟输出

- 650 MHz全功率模拟带宽

- 2 V p-p输入电压范围

- 1.8 V电源供电

- 串行端口控制

- 灵活的位定向

- 生成内置及用户自定义数字测试码

- 可编程时钟与数据对准

- 关断和待机模式

AD9681是一款8通道、14位、125 MSPS模数转换器(ADC),内置片内采样保持电路,专门针对低成本、低功耗、小尺寸和易用性而设计。该产品的转换速率最高可达125 MSPS,具有杰出的动态性能与低功耗特性,适合比较重视小封装尺寸的应用。

该ADC要求采用1.8 V单电源供电以及LVPECL/CMOS/LVDS兼容型采样速率时钟信号,以便充分发挥其工作性能。无需外部基准电压源或驱动器件即可满足许多应用需求。

AD9681会自动倍乘采样速率时钟,以便产生合适的LVDS串行数据速率。它提供数据时钟输出(DCO±1、DCO±2),用于在输出端捕获数据,以及帧时钟输出(FCO±1、FCO±2)用于发送新输出字节信号。支持独立关断各通道;禁用所有通道时,器件典型功耗低于2 mW。

该ADC内置多种功能特性,可使器件的灵活性达到较佳、系统成本较低,例如可编程时钟与数据对准、生成可编程数字测试码等。可获得的数字测试码包括内置固定码和伪随机码,以及通过串行端口接口(SPI)输入的用户自定义测试码。

AD9681采用符合RoHS标准的144引脚CSP-BGA封装。额定温度范围为−40°C至+85°C工业温度范围。该产品受美国专利保护。

产品特色

- 小尺寸。一个小型10 mm × 10 mm封装中集成8个ADC。

- 低功耗。器件每通道消耗110 mW (125 MSPS),功率选项可调整

- 易于使用。数据时钟输出(DCO±1、DCO±2)工作频率高达500 MHz,支持双倍数据速率(DDR)操作。

- 使用灵活。SPI控制提供丰富灵活的特性,可满足各种特定系统的需求。

应用

- 医疗成像

- 通信接收机

- 多通道数据采集

参考资料

数据手册 1

用户手册 1

技术文章 1

ADI 始终高度重视提供符合最高质量和可靠性水平的产品。我们通过将质量和可靠性检查纳入产品和工艺设计的各个范围以及制造过程来实现这一目标。出货产品的“零缺陷”始终是我们的目标。查看我们的质量和可靠性计划和认证以了解更多信息。

| 产品型号 | 引脚/封装图-中文版 | 文档 | CAD 符号,脚注和 3D模型 |

|---|---|---|---|

| AD9681BBCZ-125 | 144-Ball CSPBGA (10mm x 10mm x 1.7mm) | ||

| AD9681BBCZRL7-125 | 144-Ball CSPBGA (10mm x 10mm x 1.7mm) |

这是最新版本的数据手册

软件资源

找不到您所需的软件或驱动?

申请驱动/软件硬件生态系统

工具及仿真模型

设计工具 2

AD9681 Simulink ADIsimADC Model

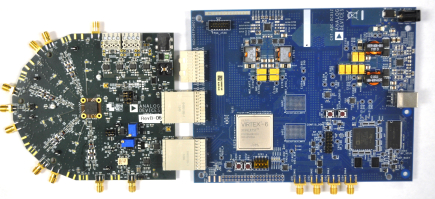

打开工具评估套件

最新评论

需要发起讨论吗? 没有关于 AD9681的相关讨论?是否需要发起讨论?

在EngineerZone®上发起讨论