JESD204B サブクラス (パート2): サブクラス 1 対サブクラス2 システムの考慮事項

Read other articles in this series.

「JESD204B サブクラス (パート1): JESD204B サブクラスとデターミニスティック・レーテンシーの紹介」では、JESD204Bサブクラスとデターミニスティック・レーテンシーの概要およびサブクラス0 システムでのマルチチップ同期に対するアプリケーション層ソリューションに関する詳細を説明しました。シリーズのパート2 では、サブクラス 1 とサブクラス 2 の違いを詳しく説明します。特に、デターミニスティック・レーテンシーに関係するタイミング条件を満たす課題、サブクラス 2 でのデバイス・クロック速度制限、サブクラスが与えられたシステム・アプリケーションに対して最適になるガイドラインについて説明します。

サブクラス 1

サブクラス 1 システムでは、デターミニスティック・レーテンシーの精度はデバイス・クロックとSYSREF の間のタイミング関係およびシステム内でのこれらの信号の分配スキューに依存します。SYSREF に対するセットアップ・タイム条件とホールド・タイム条件(TSU とTHOLD)の他に、アプリケーションのデターミニスティック・レーテンシーの不確定性に対する耐性が、SYSREF とデバイス・クロックに対するアプリケーションの分配スキュー要求を決める時に重要になります。

精度良くSYSREF を取り込む

JESD204B インターフェースを採用するコンバータは、非常に高い周波数でデータをサンプルします。システム内の位相ノイズを小さくするため、これらのコンバータではサンプリング周波数かそれ以上のリファレンス・クロック(JESD204 デバイス・クロックと同じ)を使用することが一般的です。多くの場合、このクロックはGHz 範囲です。これらの速度で、セットアップ・タイム条件とホールド・タイム条件を満たすことは非常に難しくなります。システム設計を容易にするため、SYSREF および/またはデバイス・クロックの位相オフセットをJESD204B システムに含まれる各デバイスに対してプログラマブルにすることが必要になります。

サブクラス 2 に対するサブクラス 1 の利点の1 つは、ソース同期クロックを使用していることです。サブクラス 2 システムではシステム同期クロックを使うため、ソース同期クロックの場合より早く周波数制限に遭遇します。これは、特定のサブクラス 1 とサブクラス 2 のタイミング例を調べることで明確になってきます。

デターミニスティック・レーテンシーの不確定性

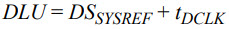

デターミニスティック・レーテンシーの不確定性(DLU)はJESD204B システム内のLMFC スキューであり、システム内でのSYSREF の最も早い取り込みと最も遅い取り込みとの間の差で決定されます。図 1 に、SYSREF 取り込みに対するセットアップ・タイム条件とホールド・タイム条件が満たされないときにシステム内の各デバイスで発生するワーストケースDLU を示します1。これは、システム内のデバイス・クロックの分配スキューが制御されていない場合に発生し、最大1 デバイス・クロック(DCLK)の不確定性を発生させます。これがSYSREF 分配スキュー(DSSYSREF)に加わり、総合DLU が発生します。

DSSYSREF は、システム内 (システム内の全デバイス間で)で最も早く到着するSYSREF の着信時間と最後に到着するSYSREF の着信時間の差です。説明では、TSU = ½ TDCLKおよび THOLD = ¼TDCLK です。最も早く到着するSYSREF (A)は最も早い時間に取り込まれ(DCLKA はセットアップ時間条件を満たします)、最後に到着するSYSREF (N)は最も遅い時間に取り込まれます(DCLKN はセットアップ時間条件を満たしません)。そのため、対応するLMFC はDSSYSREF + TDCLK だけ位相がずれます。

多くのアプリケーションで、DLU に対する条件はこのワーストケース・シナリオを許容するようになっています。これらのアプリケーションの場合、デバイス・クロックの分配スキューを厳しく制御することは不要です。SYSREF パルス幅を(2 × TDCLK)以上にして、システム・タイミング条件を満たすようにSYSREF 分配スキューを制御することで十分です。

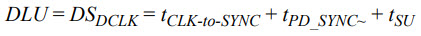

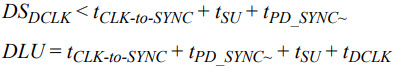

デバイス・クロックの不確定性が増えることを許容できないアプリケーションでは、デバイス・クロック分配スキューを厳しく制御して、SYSREF のタイミング条件をシステム内の各デバイスで満たす必要があります。このケースを図2 に示します。不確定性は次式で与えられます。

デターミニスティック・レーテンシー不確定性の最小化

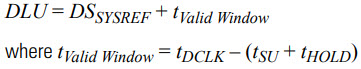

上の DLU の式が示すように、SYSREF/DCLK 対内の分配スキューを小さくすることにより、各対のセットアップ・タイムとホールド・タイムを満たすようにしてDLU を小さくすることができます。

セットアップ・タイム条件とホールド・タイム条件を満たすため、JESD204B システム内の各デバイスは自身のSYSREF/DCLK 対を持つ必要があります。これらの各対内で、タイミングを保証するためパターン長を一致させることができます。パターン長一致の規定値は、SYSREF スイッチングの有効なウインドウ時間により決定されます。また、SYSREF は取り込みエッジをDCLK とする出力とし、SYSREF の長さはホールド・タイム条件から決まるDCLK の長さより長い必要があります(THOLD が0 の場合は、2 つの長さを一致させることができます)。

パターン長を一致させるため、対内の分配スキューを小さくすることは、実質的にSYSREF 分配スキューを小さくすることと同じです。この分配スキューの規定値は、DLU 規定値から有効ウインドウ時間を減算した値になり、パターン長を一致させることにより調節することができます。DLU 規定値は、アプリケーションの条件から設定されます。

DLU を最小化するこれらの方法を図3 に示します。JESD204bシステム内の各デバイスは自身のSYSREF/DCLK 対を持つため、SYSREF 取り込みのタイミング条件を満たすことは、ソース同期クロックを採用するシステムと同様です。各デバイスのタイミング・マージンは、システム内の他のデバイスに依存しないと見なされます。

AD9250 を使ったSYSREF タイミング例

AD9250 は、14 ビット、250 MSPS のデュアルADC で、5 GbpsのJESD204B シリアル・データ出力を採用しています。PLL 性能を最適化するため、AD9250 は最大1.5 GHz のデバイス・クロック速度を許容します。このデバイスは、最も厳しいシステムDLU 条件のもとで、パターン長を一致させてSYSREF タイミングを満たす方法の優れた例を提供します。2 この例の条件は次の通リです。

- DCLK = 1.5 GHz (周期667 ps )

- TSU = 500 ps でTHOLD = 0 ps

- 例えば、システムのDLUMAX = 1 DCLK (667 ps)

SYSREF タイミングを満たすための対内パターン長の一致

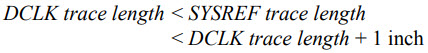

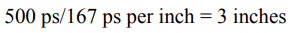

この例の仕様に基づき、セットアップ・タイムとホールド・タイムを満たす「有効ウインドウ」は167 ps (667 ps TDCLK – 500 psTSU)です。伝搬時間は、信号がソースを出発してからシンクに到着するまでの時間です。SYSREF の伝搬時間からDCLK の伝搬時間を減算した値は、セットアップ・タイムを満たすためには167 ps より小さい必要があり、かつホールド・タイムを満たすためには0ps より大きい必要があります。この伝搬時間の差を大まかにインチ数に変換するため、1 インチのFR-4 材料の伝搬時間を167 ps/インチと見積もります。そうすると、システム内の各SYSREF/DCLK 対で、次の配線条件を満たす必要があります。

この条件を満たすと、図4 に示すように、SYSREF の変化は有効ウインドウ内で発生するようになります。

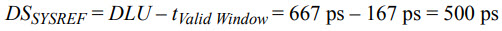

DLU 規定値を満たすための対内パターン長の一致

DLU 規定値が667 ps に設定されており、かつDLU 規定値と対内(すなわちSYSREF) 分配スキュー(DSSYSREF)との関係が既知であるため、パターン長一致の規定値は次のように簡単に求めることができます。

したがって、すべての SYSREF/DCLK 対での対内分配スキューは、次の値内である必要があります。3。

図 5に、このタイミング例を示します。「最適」分配スキュー(DSSYSREF)とは、厳しくないパターン長一致条件を許容するケースを意味します。

SYSREF タイミングとDLU 規定値を満たす高度なソリューション

もちろん、低速デバイス・クロックを使用すると長さの一致が容易になり、これを使用して問題を解決することができます。これには、システム位相ノイズ性能の犠牲がともないます。これと似たソリューションは、DLU 条件を緩くすることですが、システム位相ノイズ性能を向上させる利点は維持されます。DLU 条件の設定は、アプリケーションに依存します。これについては、デターミニスティック・レーテンシーの精度の文脈で次に説明します。位相ノイズ性能の向上が要求されて、DLU 条件を緩和できない場合、SYSREF/DCLK のデバイス内スキューとデバイス間スキューに対する配線条件(上の例では、それぞれ1 インチと3 インチ)を満たすことは困難過ぎると思われます。この場合、デバイス・クロックおよび/またはSYSREFに対する調整可能な位相遅延が必要になります。調整の分解能は、セットアップ・タイムとホールド・タイムに基づく「有効ウインドウ」より小さい必要があります。例から、「有効ウインドウ」は167 psになります。

FPGAによっては、微調整条件を満たすことが困難なものがありますが、AD9528はこの条件を満たします。これは、SYSREF位相遅延を60 ps ステップで調整可能で、これが全出力での変異性が50 psより小さいためです。図6に、タイミング条件を満たすためにSYSREFを遅延させる方法を示します。この説明では、SYSREFを60 ps インクリメントで遅延させます。位相の設定値は、SYSREF エッジを有効ウインドウの中央付近に設定することを推奨します。説明で、緑のエッジは良い位相設定値を、赤のエッジは悪い設定値を、それぞれ表します。位相設定値3は有効ウインドウの中央であるため、この場合これを使います。

AD9528のデバイス・クロック出力は、SYSREF 出力で使用可能な60 ps の位相ステップの他に、½デバイス・クロック・サイクルで位相を遅延させることができます。この機能も、SYSREFタイミング条件を満たす際に役立ちます。

SYSREF セットアップとホールド・タイミングのモニタ

ADI のAD9680 は、SYSREF とデバイス・クロックとの間の相対的タイミングの調整に役立つSYSEREF セットアップとホールド・タイムのモニタ回路を内蔵しています。これら2 つのレジスタをモニタすると、SYSREF の取り込みでタイミング条件に問題があるか否かを知ることができます。これらのいずれかのレジスタが、タイミング・マージンが不十分であることを示すと、デバイス・クロックに対するSYSREF の相対位置の調整が必要であることが分かります。上の例では、デバイス・クロックに対するSYSREF 位相の調整によって(例えばAD9528 を使用) 、またはSYSREF および/またはデバイス・クロック信号のパターン長の調整によって、この調整を行うことができます。

デターミニスティック・レーテンシーの精度

システムのデターミニスティック・レーテンシーの不確定性がどのように設定されるかを理解するためには、アプリケーションの理解が必要です。デターミニスティック・レーテンシーを必要とする大部分のシステムでは、時間内で、どのサンプルが注目するデータの開始を表すかを精確に知る必要があります。デターミニスティック・レーテンシーの一般的な用途は、システム内の複数のコンバータを同期させることです。これは、マルチチップ同期と呼ばれています。これらのシステムでは、すべてのコンバータ間でサンプルのアライメントが必要です。このため、デターミニスティック・レーテンシーには「精確なサンプル」が必要です。これらのシステムでは、DLU はサンプル・クロックの± ½である必要があります。サンプル・クロックの整数倍であるデバイス・クロックを持つ利点は、精確にサンプルするなどのように、SYSREF の取り込み処理が簡素化されることです。AD9250 の例では、デバイス・クロックはサンプル・クロックの6 倍です。精確なサンプルであるためには、±½ サンプル・クロックのDLU 条件は±3 デバイス・クロックに言い換えられます。これを図7 に示します。AD9250 の例では、各デバイスでSYSREF 位相を調整できるため、最も厳しいDLU 条件でも容易に満たすことができることを示しました。デバイス・クロックがサンプル・クロックの倍数である場合、サンプル精度に対するSYSREF の取り込みは、大幅に簡素化されます。コンバータのサンプル・レートが1 Gbps を超えて高くなると、SYSREF クロックとデバイス・クロックの位相遅延機能が不可欠になります。

SYSREF 取り込みでの問題

SYSREF のセットアップ・タイム条件とホールド・タイム条件、およびDLU 条件を満たす他に、SYSREF の取り込みに関係して発生する他の問題があります。例えば、システムの初期パワーアップ時、システム・クロックが安定する前にSYSREF がアクティブになる可能性があります。これは、連続的なSYSREF 信号を使用する際に発生することがあります。この問題は、デバイスを所定エッジ数だけ待たせた後、クロックを同期するプログラム可能なJESD204B インターフェースを導入することにより解決されます。もう1 つのプログラムに関するオプションは、有効なエッジが予想される際にSYSREF 取り込みの「用意」を可能にすることです。これにより、連続SYSREF で同期化するタイミングを制御できるようになります。AD9625 やAD9680のようなJESD204B インターフェースを採用する多くのADI コンバータ・デバイスは、これらの機能を内蔵しています。

もう 1 つの例は、SYSREF の小さな変動により、再同期を不要にできることです。この問題は、SYSREF エッジに対してLMFC を中心とする有効ウインドウをユーザーが指定できるようにプログラム可能なJESD204B インターフェースを導入することにより解決されます。SYSREF がこの有効ウインドウ内で発生する場合、システムは「同期中」と見なします。多くのアプリケーションでは連続SYSREF 信号をモニタしリンク状態を知るため、これは非常に便利な機能です。LMFC 境界とSYSREF を比較して、この場合同期状態を決めています。ADI のAD9680 はこの機能を内蔵しています(図8)。

SYSREF 取り込みで役立つその他の機能は、SYSREF の取り込みに使用するデバイス・クロック・エッジを変更する機能とLMFC を揃えるために使用するSYSREF エッジを変更する機能です。JESD204B インターフェースを採用する多くのADI コンバータ・デバイスはこれらの機能を内蔵しています。

サブクラス2

サブクラス 2 システムでは、デターミニスティック・レーテンシーの精度はデバイス・クロックとSYNC~信号との間のタイミング関係、および次に説明する、タイミング計画を使ってしまう様々な項目に依存します。サブクラス1 の場合と同様に、デターミニスティック・レーテンシー不確定性に対するアプリケーションの耐性が、SYNC~ とデバイス・クロックに対するアプリケーションのパターン長一致条件を決める際に重要になります。

SYNC~ 取り込みと開始の精度

SYNC~ を精確に取り込むためのタイミング条件を満たす問題は、SYSREF の取り込みでサブクラス1 の説明に示した問題と本質的に同じ問題ですが、サブクラス2 でのクロック方式はシステム同期であるため、各取り込みデバイス間で独立にタイミング解析を行えなくなるので、マルチコンバータ・アプリケーションでは難しくなります。これだけでなく、SYNC~ 信号の発生に関して不確定性を考慮することも必要になります。システム同期クロックを使用するシステム内の各デバイスは、タイミング余裕の一部を使ってしまいます。タイミング余裕を失ってしまう項目としては、クロック分配スキュー(DSDCLK)、マルチコンバータ・システムのSYNC~ 分配スキュー(DSSYNC~)、SYNC~ 信号の伝搬遅延、各JESD204B トランスミッタのセットアップ・タイム条件とホールド・タイム条件、各JESD204B レシーバのSYNC~ 出力でのクロック―SYNC~ 間出力遅延などがあります。

サブクラス2 でのデバイス・クロックの上限

JESD204B 規格では、サブクラス2 インプリメンテーションでシステム同期クロック方式を採用しているため、デバイス・クロック・レートの限界が必要なことを認識しています。規格のアネックスB では、この規定値を500 MHz とすることを推奨し、「SYSREF はデバイス・クロックと精確に位相が揃う方法で発生できるソース同期信号であるため、500 MHz より高いデバイス・クロック・レートでの動作を狙うシステム設計者はサブクラス1 の方法を使うことを好むものと予想する」と述べています。

このような規定値が存在する理由を説明するため、詳細なタイミング例を示します。

サブクラス2 マルチDAC のタイミング例

2 個のサブクラス2 DAC デバイスと1 個のロジック・デバイスを接続したトランスミッタ・アプリケーション(図9)について調べます。

例えば、500 MHz のデバイス・クロックを使用します。SYNC~信号とDCLK 信号は、次に示すPCB スキュー4 を持ちます。

- FPGA へのクロック= 300 ps

- DAC1 へのクロック= 600 ps

- DAC2 へのクロック= 720 ps

- FPGA へのSYNC~1 = 660 ps

- FPGA へのSYNC~2 = 750 ps

ジッタと PVT 変動を考慮する前のタイミングを図10 に示します。この図で、ワーストケース・タイミングはFPGA 入力でSYNC~2 信号の取り込みで発生します。DLCK2 伝搬遅延、SYNC~2 伝搬遅延、SYNC~2 のクロック―出力間遅延の組み合わせにより、FPGA 入力での取り込みに対して600 ps のセットアップ・タイムが残ります。

ただし、セットアップ・タイム、ジッタ、PVT 変動が加わると、図11 に示すようにタイミング違反が容易に発生します。この例では、セットアップ・タイムが500 ps で、PVT 変動5が300 psに増え、ジッタ6が150 ps になります。最終到着のSYNC~(SYNC~ 2)で、このためにタイミング違反が発生します。

上の例では、パターン長および/またはクロック位相の調整を行ってタイミングを解決することができますが、DCLK 周波数が高くなると、サブクラス1 インプリメンテーションに比べて考慮すべき変数が増えるため、遥かにタイミング条件を満たすことが難しくなります。JESD204B 規格のセクション6.4 に、SYNC~ 取り込みタイミングの問題を詳細に記載してあります。

サブクラス2 のデターミニスティック・レーテンシーの不確定性

サブクラス 1 の場合と同様に、タイミングの制約はデターミニスティック・レーテンシーの不確定性に対するアプリケーションの耐性により決まります。表1 に、システムのDLU に対するサブクラス2 タイミング条件を満たす際に考慮すべき変数をまとめます。7

| Application | Variable 1 | Variable 2 | Variable 3 | Variable 4 | Variable 5 |

| Single converter | Clock-to-SYNC~ output delay | tSU and tHold @ ADC | tPD_SYNC~ | DSDCLK | |

| Multiconverter | Clock-to-SYNC~ output delay | tSU and tHold @ ADC | tPD_SYNC~ | DSDCLK | DSSYNC~ |

サブクラス2 システムでのDLU は、TCLK-to-SYNC、TPD_SYNC~、TSU、システム内のデバイス・クロック(DSDCLK)の分配スキューの間の関係で決まります。シングル・コンバータ・アプリケーションでは、最適ケースのDLU は次式で与えられ、図 12 に示します。

説明では、TSU = ½ TDCLK および THOLD = ¼ TDCLK です。図に示すように、DLCK に歪を与えてDCLK―SYNC~ 間遅延とSYNC~伝搬遅延に一致させ、セットアップ・タイム条件を満たすようにします。

シングル・コンバータ・サブクラス 2 システムでのワーストケースDLU は、トランスミッタでDCLK の歪が小さいために最初の使用可能な取り込みエッジのセットアップ・タイムを満たさない場合に発生します(図 13 参照)。

アプリケーションに最適なサブクラスはどれか?

JESD204B システムに使用するサブクラスの選択は、デターミニスティック・レーテンシーの必要性、必要な場合のその精確さ、システムのデバイス・クロック条件に依存します。

サブクラス 0 は実現が最も容易で、デターミニスティック・レーテンシーが不要な場合に使用することができます。マルチコンバータ・システムがすべての (または幾つかの) コンバータからのサンプルの同期を必要とする場合でも、これをAD9625 とAD9680 でサポートされているタイム・スタンプ方式を使って実現することができます。

極めて高いデバイス・クロック・レートをサポートするサブクラス 1 の能力があり、かつ高いサンプリング・レートのコンバータで使用する場合、これはこれらの高いレートを必要とするシステムに対する最小リスクのソリューションになります。サブクラス 1 デバイスを低周波のレートで使うこともできます。500 MHz より低いデバイス・クロック・レートで使う場合、タイミング条件を満たすことは、クロック位相の調整なしで済む非常に簡単なことです。

サブクラス 2 デバイスも、500 MHz より下で使うことができます。低いレートでサブクラス 2 を使用する小さい利点は、ロジック・デバイスのIO 数の削減と、各JESD204B デバイスへのSYSREF の配線が不要になることです。

参考文献

1 DLU 概念の説明をシンプルにするため、ここではクロック・ジッターと処理、電圧、温度(PVT) に起因する変動を考慮しません。

2 DLU 条件をデバイス・クロックに一致させることは、SYSREF のタイミングを満たすためのワースト・ケースになります。

3 500 ps はSYSREF のワースト・ケース・スキューであり、パターン長一致の規定値を決める際に使う必要があります。

4 300 ps = PCB パターンの1.8 インチ。

5 SYNC~ 出力でのPVT 変動と両クロック出力。

6 DLCK とSYNC~のジッター。

7 DLU 概念の説明をシンプルにするため、ここではクロック・ジッターと処理、電圧、温度(PVT) に起因する変動を考慮しません。

著者について

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}