フェーズド・アレイ用分散型ダイレクト・サンプリングSバンド・レシーバーの測定の概要

概要

本稿では、16チャンネルSバンド・ダイレクト・サンプリング・レシーバー設計の性能測定値と予測値について詳しく述べます。この設計は、最近発売された4GSPSクロック使用のダイレクト・サンプリングA/Dコンバータ(ADC)をベースとしており、サンプリングはコンバータの第2ナイキスト・ゾーンで行われます。以下では、まず詳細な解説が記載されたオンライン資料の参照先を示しながら、設計の構成を説明します。次に、レシーバーのRFコンポーネントと組込みのデジタル信号処理(DSP)機能について説明します。最新のデータ・コンバータはDSP機能を内蔵しています。更に、シングルチャンネル性能を予測するための計算を示して、それを測定値と比較します。シングルチャンネルの性能を理解したところで、16個のチャンネルからのデータを結び付けた一連の測定値を使い、ノイズ密度、スプリアス信号、および相互変調積について、ダイナミック・レンジの改善を評価します。最後に、マルチチャンネル性能の傾向に関する一連の評価結果を示します。これらの結果は、分散配置された多数のレシーバーによって実装される大型フェーズド・アレイ・モデルに応用できます。

はじめに

ADCのサンプル・レートの増大により、現在ではSバンド以上の帯域を通じて、ダイレクト・サンプリングRFシステムを実現できるようになっています。ADC技術の進歩は、デジタル・ビームフォーミング・フェーズド・アレイの急速な普及を可能にしました。これらの進歩の一方で、業界には2つの点に関して問題が残されています。すなわち、ダイレクト・サンプリング・レシーバーのシングルチャンネル性能に関する問題と、多数のダイレクト・サンプリング・レシーバーを大型フェーズド・アレイに分散させた場合に実現できるダイナミック・レンジの改善に関する問題です。

最新のデータ・コンバータを開発している半導体企業とフェーズド・アレイ・アーキテクチャの改善を図っている大規模なシステム・インテグレータ企業のどちらもが多大な努力を払っているにも関わらず、分散配置された複数のレシーバーのデータを一体として組み合わせる多チャンネルのダイレクト・サンプリング・レシーバー・システムで実現可能な、性能の向上を定量的に示す公開データの数は依然として限られています。

本稿の目的は、システム・エンジニアが各自の大型フェーズド・アレイ・モデルを特徴づけるために使用できる、定量化可能な測定を行いやすくすることにあります。ここに示すデータ収集は、より複雑なフェーズド・アレイ・システム・モデルを作成する際に考慮すべき、基本的測定セットの1つに過ぎません。

評価したレシーバー設計

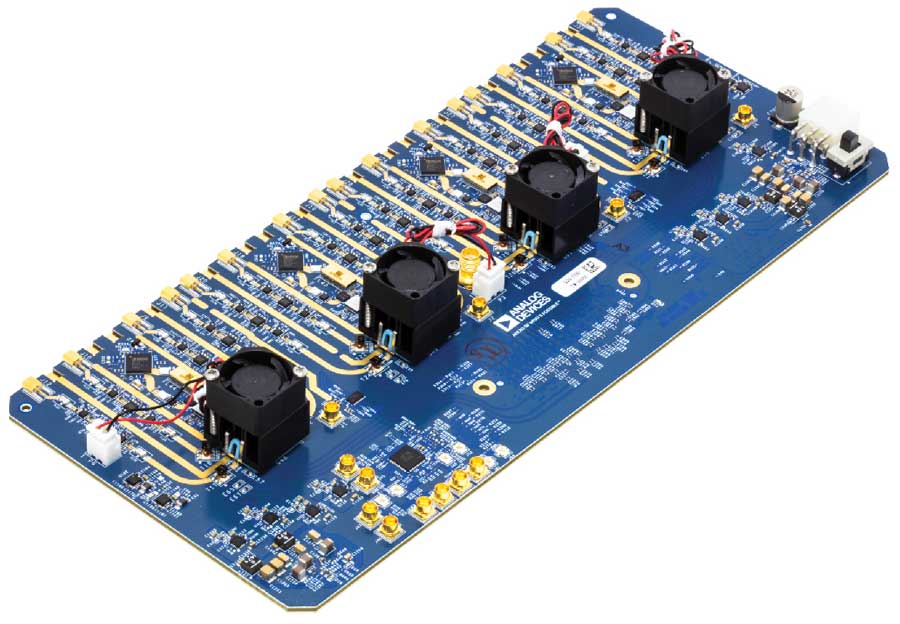

マルチチャンネル環境で最新の高速データ・コンバータを評価するために、16チャンネルのダイレクトSバンド無線周波数(RF)サンプリング・プラットフォームを作成しました1。このプラットフォーム(図1参照)には、4個のAD9081ミックスド・シグナル・フロント・エンド(MxFE®)集積回路(IC)が含まれています。それぞれのAD9081は4個のRF D/Aコンバータ(DAC)と4個のRF ADCを内蔵しており、合計で16個のRF送信チャンネルと16個のRF受信チャンネルを使用できます。Quad-MxFEプラットフォームの製品ページには、このプラットフォームの詳細な説明と使用ソフトウェアが記載されています。

図1 Quad-MxFE 16チャンネル・ダイレクト・サンプリング・プラットフォーム

レシーバー設計の詳細を図2に示します。レシーバー・フロント・エンドのRFコンポーネントと、AD9081内部のADCおよび組込みDSP構成が示されています。

図2. レシーバーのブロック図。AD9081内部の組込みDSPの構成とフロントエンドRFコンポーネント。

新型ADCのサンプル・レートが増加してダイレクト・サンプリング・レシーバー・アーキテクチャが可能になったのに伴い、設計構成における検討事項の多くがRF領域から組込みDSPへとシフトしています。RFチェーンは極めてシンプルです。主な構成要素は、ゲインを得るためのいくつかのアンプ、デジタル制御減衰器を使用するゲイン制御機能、そしてアンチエイリアシング用のフィルタです。しかし、組込みDSP構成は、前世代のデータ・コンバータを利用するレシーバー設計と比較して、プログラム可能な属性をより多く備えています。組込み処理の増加というこの傾向は、将来のデータ・コンバータでも続くことが予想されます。したがって、レシーバーの設計者は、組込み処理の内部で選択されるオプションにどのような意味があるのかを、2つの観点から理解することが必要になります。その1つは、システムの求めるものを基準にADCデータの前処理を捉えることです。2つめは恐らくより重要なことで、データ・コンバータ内にある組込みDSPを最適な形で使用し、以前はフィールド・プログラマブル・ゲート・アレイ(FPGA)ファブリックによって行われていた処理の負荷を軽減して、最終的にシステムの処理能力の効率を最適化することです。

この傾向に基づき、測定値と計算予測値を比較する場合には、DSP構成を記述する必要があります。本稿に示すデータセットは、4GSPSでサンプリングを行うようにAD9081 ADCを設定します。ADCの後段にはプログラム可能な有限インパルス応答(pFIR)フィルタが置かれています。このフィルタは、帯域全体にわたって振幅と位相を等しくするために使われます。更にその後段には粗調整デジタル・ダウンコンバータ(DDC)が置かれており、その内部では数値制御発振器(NCO)が対象帯域の中央に設定され、1/4のデシメーション・ブロックが使われています。微調整DDCはNCOをバイパスするように設定されており、追加の1/4デシメーション・ブロックと6dBのデジタル・ゲインが使われています。以上の設定にすると、データ・レート250MSPS、デジタル・ゲイン0dBとし、粗調整NCOのNCO周波数をゼロ以外の値に設定して帯域中央を選択した場合、合計デシメーション・レシオは16になります。

コンポーネント設定は、AD9081の製品ページから入手できるアプリケーション・プログラミング・インターフェース(API)を通じて行うことができます。本稿で使用する関連主要レシーバーAPI関数の概要を表1に示します。

| API関数呼び出し | ビットフィールド | レジスタ | 値 |

| adi_ad9081_adc_ddc_ coarse_nco_mode_set(…, …, AD9081_ADC_NCO_VIF | COARSE_ MXR_IF | 0x282<7..6> | 0x00 |

| adi_ad9081_adc_ddc_fine_nco_mode_ set(…, …, AD9081_ADC_NCO_ZIF) | FINE_MXR_IF | 0x283<7..6> | 0x01 |

| adi_ad9081_adc_ddc_coarse_gain_ set(…, …, 0) | COARSE_GAIN | 0x282<5> | 0x0 |

| adi_ad9081_adc_ddc_fine_gain_set(…, …, 1) | FINE_GAIN | 0x283<5> | 0x1 |

シングルチャンネル性能測定値と計算予測値の比較

レシーバー性能のスプレッドシートによる計算を図3に示します。この分析は、ゲイン、ノイズ、および3次インターセプトの主要なレシーバー項だけを含めた簡単なものになっています。ノイズについては、ノイズ指数とノイズ電力の両方が示されています。最初にRF成分のカスケード分析が示されていて、これが次のADC性能に追加されます。RF成分とADCの両方を含むカスケード分析の詳細は、「広帯域RFレシーバー・アーキテクチャ・オプションの検討」2に示されています。最後にこの性能がレシーバーのRFコネクタ入力に反映されて、図3の最下部にその概要が示されています。

図3 レシーバー性能の計算:最初の部分にはRFカスケードだけが示されています。続いて、レシーバー全体の性能を予測するためにADC性能にRF性能が加えられます。更にこの性能が、RF入力位置での有効なADCを表すレシーバー・コネクタ入力に反映されます。

フルスケール入力電力と入力3次インターセプト・ポイント(IIP3)の測定値を図4に示します。まず、フルスケール入力電力を示す左側の図を見ると、図3に示す予測値の見積りが–21dBmであるのに対して、図4に示す測定値は、通常、帯域中央で–20dBm±1dBとなっています。帯域端における値の増加はアンチエイリアシング・フィルタによるもので、実際にこのデータにはフィルタ形状が現れています。スプレッドシートでは考慮されていない損失が更に1dB程度はあるものと予想されるので、1dBまたは2dB以内のゲイン・マッチングは妥当なものとみなされます。図4右側のIIP3データを図3の予測値と比較すると、2.8GHzでチャンネル2にディップがあることを除けば、IIP3は予測値よりわずかに(約1dB)良好であることが分かります。また、このIIP3データはカスケード予測に十分に近いとみなされます。

図4. フルスケール入力および入力IP3でのシングルチャンネル測定値。測定値はレシーバーのRFコネクタ入力に合わせて補正。

次に、高速フーリエ変換(FFT)分析の記述が妥当なものであることを確認します。ここでの記述に示すすべてのデータは、FFTと、FFTデータから測定値を得るための処理に基づいています。図5にFFTの例を示します。上のプロットはシングルチャンネルのもので、下のプロットは複数チャンネルを組み合わせて補正を加えた場合のものです。

図5. FFT測定値の例。

図5のシングルチャンネルFFTを使って、ノイズ密度を図3の予測値と比較することができます。図3のカスケード計算は、RFセクションをADCとカスケード接続した場合のノイズ指数を–145dBFS/Hzと予測しています。図5のシングルチャンネル測定値は–144.3dBFS/Hzを示しているので、ここでも、カスケード計算は測定値に近い値を示していることが分かります。

図5下側に示す組み合わせデータのFFTでは、「DAC/ADCとDSPの統合ICにより、広帯域マルチチャンネル・システムの性能を改善する」3 と、「マルチチップ同期機能を活用し、広帯域対応のDAC/ADCをデタミニスティックな位相で起動する」4の内容に従って補正が行われ、データが合計されています。次いで、組み合わせデータによるビット数の増加に対処するためにフルスケールの調整を行い、最後に同じFFTを実行します。次に示すように、このアプローチでは組み合わせゲインのために、フルスケールの組み合わせレベルが平均チャンネル・レベルに近付いて、ダイナミック・レンジが向上します。

シングルチャンネルと組み合わせのレシーバー測定値

ノイズ密度とスプリアス信号

本稿では、チャンネルを組み合わせた場合のノイズとスプリアスの改善について調べることが目的でした。また、チャンネル組み合わせの影響と入力電力レベルおよび周波数の関係を確認することも、関心事でした。図6と図7にその結果を示します。

図6. チャンネルを組み合わせた場合はノイズ密度とスプリアスの両方が改善されています。これらのデータセットは2.8GHzで得られたものです。

図7. シングルチャンネルと組み合わせチャンネルでのノイズ密度およびスプリアスと周波数の関係。各周波数で10個のデータをキャプチャ。プロット上の各ドットが1つのFFTを表しています。

まず、図6の左側のプロットには、ノイズ密度の影響と入力電力の関係が示されています。低電力レベルでは、システムのチャンネル数がN = 16で10log(N)が12dB改善されています。電力が大きくなるにつれて、組み合わせ出力のノイズ密度の方が個々のチャンネルよりわずかに速いレートで増加しています。これは、チャンネル間の相関ノイズ項を示すものです。これらのデータセットにおける性能低下は約1dBに過ぎないので、チャンネルを組み合わせた場合はやはり大きな改善が実現されています。相関性の源は、1つのAD9081内の4つのチャンネルに共通のフェーズ・ロック・ループ(PLL)か、使用しているRF入力源のどちらかと考えられます。確認された10dBの改善が非常に大きなものであることは間違いないので、これ以上の調査は行いませんでした。

図6の右側はシステムのスプリアス性能の詳細です。やはり、チャンネルを組み合わせた場合はスプリアス性能が大きく改善されており、各チャンネルのスプリアス間には相関関係がないことが示されています。スプリアスの改善は極めて良好な結果を示しています。これらのデータ・キャプチャの際には、特定周波数オフセットにおける特定スプリアスの評価にかなりの労力が割かれています。意外だったのは、スプリアスの発生が極めて不規則だったことです。シングルチャンネルの最大スプリアスはチャンネルごとに異なり、図7に示す明確な2次高調波の場合を除いて、組み合わせデータに最大スプリアスとして現れることはありません。このスプリアスの不規則性については2つの理由が考えられます。1つは、図5のFFTに示すように開始点が非常に良好なことです。もう1つの影響は、テスト・セットアップにおける16チャンネルすべてのデータ・キャプチャのサイズが限られて、そのキャプチャされたデータに対するFFT長さも、16チャンネルすべてについて4096ポイントに限られていたことです。このデータ・キャプチャ長さにも関わらず、依然として90dBc未満のスプリアスが確認できます。今後のマルチチャンネル・テスト・プラットフォームは、FFTの長さを伸ばすことに目が向けられるでしょう。

図7は、同じシングルチャンネルと組み合わせチャンネルの性能と周波数の関係です。このデータセットでは、各周波数で10個のデータをキャプチャしました。プロット上の各ドットが1つのFFTを表しています。これらのデータの電力レベルは、通常–5dBFSです。

図7左側のノイズ密度データは、すべてのチャンネルと周波数について、個々のチャンネルの値が図3の予測値と非常によく一致していることを示しています。組み合わせデータはいずれの周波数でも約11dBの改善を示しており、該当電力レベルにおける図6の結果とよく一致しています。

図7右側のスプリアスも、組み合わせチャンネルでは一貫して性能が改善されていることを示しています。2.65GHzにおけるスプリアスはコメントに値します。この周波数では、帯域内で2次高調波が発生してシングルチャンネルのスプリアスが大きくなります。この周波数ポイントは、チャンネルを組み合わせた場合の折り返し高調波によるスプリアスの影響評価に関係するので、データに含まれています。ここには、2つの興味ある結果が示されています。1つは、スプリアス同士の間に相関関係があるようには見えないということで、もう1つは、スプリアスのレベルがチャンネルによって大きく異なるということです。この結果は良好なものであり、組み合わせ出力を最大チャンネル・スプリアスより更に10log(N)近く改善できることを示しています。また、レイアウト設計を改善することによって、チャンネル・レベルでスプリアスを改善できることも示しています。これ以上の詳しい調査は行いませんでしたが、結果を文書に残すために確認点を指摘しておきます。

振幅と位相の安定性

各周波数で複数のデータセットが収集されているので、図7のデータは振幅と位相の安定性を評価するのに役立ちます。結果を、図8の箱ひげ図(MATLAB®のボックス・プロット)に示します。

図8 振幅および位相安定性の測定値:図7で収集したデータの箱ひげ図。データセットは10個のキャプチャ・データからなり、通常は5秒間で収集します。上の図の振幅安定性は、数千分の1dBの範囲内で一定していることを示しています。下の図の位相安定性は、位相安定性が数十分の1度以内に収まっていることを示しています。

ここでは使用できるデータの数が限られているので、MATLABのボックス・プロットを選択しました。箱ひげ図はデータの分布状態を素早く把握できるように考えられたグラフで、5つの主要要素で構成されています。赤い線はデータセットの中央値を表し、この赤い線を囲む青のボックスはデータセットの第1四分位数と第3四分位数を表しています。この範囲は四分位範囲(IQR)と呼ばれ、このボックス内にデータセットの50%が含まれます。ボックスの上下には、データセットのみなし最大値とみなし最小値を表す黒い線があります。1.5×IQR(第1四分位数から第3四分位数までの範囲に1.5IQRを加えた範囲)の外にあるデータ・ポイントは外れ値とみなされ、個別のデータ・ポイントとして赤い十字で表されます。図8の振幅安定性プロットでは、すべてのチャンネルと組み合わせ出力の振幅が比較されています。位相安定性については、シングルチャンネルの位相と組み合わせ出力の位相を比較しました。このような比較方法が必要になった理由は、このテスト・セットアップでのデータ・キャプチャが非対称だったためです。興味深いのは、位相安定性データの結果からクロック分配を見ることができるという点です。位相安定性データに示すボックスの形状が4つのグループ(チャンネル1~4、5~8、9~12、13~16)内で一致していることに注意してください。これらのチャンネルはそれぞれのAD9081内部の4つのチャンネルを表し、それぞれのAD9081には専用のADF4371 PLLが使われています。この4つのグループの特定セット内で位相ドリフトが一致するという結果は、位相安定性がPLLに支配されていることを示しています。この事実は、アナログ・デバイセズが最近行った位相ノイズ分析5の結果とも一致します。

組み合わせ2トーン測定値

ここでの最終的なデータセットは、複数チャンネルを組み合わせた場合の相互変調積の影響を評価する2トーン測定値です。図9と図10にその結果を示します。

図9. 代表的な2トーンFFT測定値。チャンネルを組み合わせても搬送周波数基準の相互変調積レベル(dBc)は改善されません。

図10 組み合わせ相互変調積と周波数の関係:組み合わせ相互変調積のレベルは個々のチャンネルの平均に近いものとなっています。

結果は、相互変調積の間に相関関係があり、その値はチャンネル・レベルの相互変調積の平均に近付くことを示しています。この結果は、「Digital Arrays using Commercial Transceivers:Noise, Spurious, and Linearity Measurements.」(市販トランシーバーを使ったデジタル・アレイ:ノイズ、スプリアス、直線性の測定値)6に示されたデータと一致します。

確認された結果の概要

この広範な測定値のセットを使用し、いくつかの重要な点について概要をまとめることができます。

組み合わせチャンネルについて:

- 振幅:組み合わせ出力の振幅は平均値に近いものになっています。チャンネルの振幅と位相を揃えるために最初にキャリブレーションが行われるので、これは自然な結果です。

- ノイズ密度:

- 低出力時には、10log(N)の改善を実現できます。

- 出力がフルスケールに近付くと、共有する回路が原因となって相関項が影響する可能性があります。測定結果は、性能低下が16チャンネルで1dBに過ぎないことを示しています。

- スプリアス信号:

- スプリアスは、当初予想していたより不規則であるように見えます。この結果は良好なものであり、チャンネルを組み合わせた場合はダイナミック・レンジの改善が可能です。

- 最大スプリアスは一般に10log(N)程度改善できます。

- 16チャンネルを組み合わせた結果は、スプリアス信号が90dBc以下になることを示しています。これは非常に良好な値であり、シングルチャンネルの高性能狭帯域レシーバーに匹敵します。

- スプリアス分析用にFFTのダイナミック・レンジを改善するため、今後の評価ではFFT長を伸ばすことを考える必要があります。

- 相互変調:相互変調積の間には相関関係があり、ダイナミック・レンジの改善は期待できません。これは、フェーズド・アレイ分野では既に知られている問題です。ダイナミック・レンジに関係する他の項はチャンネルの組み合わせによって改善が実現されているので、将来のシステムや仕様は、相互変調積が原因となって直線性に左右される可能性があります。この事実は、非直線性補正における革新と、大型アレイにおける相互変調積の相関性をなくす方法に関する研究を促進することになるでしょう。

- 振幅と位相の安定性:約5秒間のデータ・キャプチャでは、数千分の1dB以内での振幅の一貫性と、数十分の1度以内での位相の一貫性が確認されています。この設計における位相安定性は、データ・コンバータのクロック源として使われるPLLによって制限されていると考えられます。位相安定性を改善する必要がある場合は、別のクロック源の使用を考えることができます。

結論:16チャンネルのノイズおよびスプリアス測定の結果は極めて優れたもので、過去の高性能狭帯域レシーバーに匹敵するとみなすことができます。これらのデータは、ダイレクト・サンプリング・レシーバーを分散配置することが完全に可能であり、プログラム可能なデジタル・ビームフォーミング・アレイ・レベルを実現しながら、従来型狭帯域システムなみの高性能を維持できることを示しています。

まとめ

本稿の目的は、代表的マルチチャンネル環境における広範なレシーバー測定値のセットを集約して定量化し、システム・エンジニアがそれを使用して、より大型のフェーズド・アレイのモデルに応用できるようにすることにあります。本稿ではこの目的に沿って、特定のダイレクト・サンプリングRFレシーバー設計を詳しく説明し、測定値と計算性能予測値を比較して、シングルチャンネルに対する組み合わせチャンネルのノイズ密度/スプリアス/相互変調性能の向上について説明しました。エンジニアが、半導体業界の供給する最新のデータ・コンバータに基づいて大型のシステムを開発する際に、これらのデータセットがその設計評価の役に立てば幸いです。

著者について

この記事に関して

産業向けソリューション

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}