広帯域RFレシーバー・アーキテクチャ・オプションの検討

ヘテロダイン・レシーバーは、過去数十年にわたり広く使われてきた標準的なレシーバー・オプションです。近年、A/Dコンバータ(ADC)のサンプリング・レートの急速な向上、組み込みデジタル処理の採用、そしてマッチングされたチャンネルの内蔵が進み、わずか数年前には現実的ではなかったレシーバー・アーキテクチャが現在では選択可能となっています。

本稿では、一般的な3つのレシーバー・アーキテクチャであるヘテロダイン・レシーバー、ダイレクト・サンプリング・レシーバー、およびダイレクトコンバージョン・レシーバーについて、その利点と課題を比較します。更に、スプリアス・システム・ノイズとダイナミック・レンジについても検討します。その意図は、この中から最も推奨される1つを選び出すことにあるのではなく、それぞれの長所と短所を明らかにし、設計者がアプリケーションに最も適したアーキテクチャを工学的基準に基づいて選択できるようにすることにあります。

アーキテクチャの比較

ヘテロダイン、ダイレクト・サンプリング、ダイレクトコンバージョンの各アーキテクチャの比較を表1に示します。表には各アーキテクチャの基本的なトポロジと、そのメリットおよび課題を示します。

| タイプ | 構成 | メリット | 課題 |

|

ヘテロダイン |

|

|

|

|

ダイレクト・サンプリング |

|

|

|

|

ダイレクトコンバージョン |

|

|

|

ヘテロダイン方式は十分に実証された技術であり、非常に優れた性能を発揮します。これを動作させることで中間周波数(IF)へのミキシングが行われます。IFには、動作帯域内で実用的なフィルタを実装して良好なイメージ除去とLOアイソレーションを実現できるよう、十分に高い周波数が選ばれます。また、更にミキシング段を追加して周波数を下げ、超高ダイナミック・レンジのADCを使用することもよく行われます。更に、レシーバー・ゲインが異なる周波数に分散することで、高ゲイン・レシーバーの発振リスクが最小限に抑えられます。適切な周波数プランニングを行えば、ヘテロダイン・レシーバーを優れたスプリアス電力性能とノイズ性能を持つものにすることができます。しかし、残念ながらこのアーキテクチャは構造が最も複雑で、使用可能な帯域幅に対する消費電力と物理的フットプリントも最も大きくなります。加えて、比帯域幅が大きい場合、周波数プランニングが極めて難しくなる可能性があります。これらの課題は、より小さなサイズ、重量、消費電力(SWaP)が求められる現代の傾向や広帯域化への要求を考えると特に深刻なため、他のアーキテクチャを採用し得るのであれば設計者はそちらを検討することになります。

ダイレクト・サンプリングは、これまで長期にわたって追求されてきた方式です。これまで障害となっていたのは、ダイレクトRFサンプリングに見合った速度でコンバータを動作させることと、広い入力帯域幅を実現することでした。このアーキテクチャでは、すべてのレシーバー・ゲインが動作帯域周波数にあるので、大きなレシーバー・ゲインが必要な場合は慎重にレイアウトを行う必要があります。現在では、LバンドとSバンドの両方において、より高いナイキスト帯域でのダイレクト・サンプリングに使用できるコンバータが存在します。この方式は進歩を続けており、Cバンド・サンプリングも間もなく実用化される見込みで、Xバンドのサンプリングがこれに続くと目されています。

ダイレクトコンバージョン・アーキテクチャでは、データ・コンバータの帯域幅を最も効率的に使用することができます。データ・コンバータは第1ナイキスト内で動作しますが、この領域では最大の性能が得られ、ローパス・フィルタリングも容易です。2個のデータ・コンバータが同時に動作してI/Q信号をサンプリングするので、インターリービングという課題に悩まされることなくユーザ帯域幅を広げることができます。これまで長年にわたりダイレクトコンバージョン・アーキテクチャについて回ってきた主な課題は、イメージ除去、LOリーク、およびDCオフセットを受容できるレベルに抑えられるようなI/Qバランスを維持することでした。近年では、ダイレクトコンバージョンのシグナル・チェーン全体の統合化とデジタル・キャリブレーション技術が進歩したことでこれらの課題が克服され、ダイレクトコンバージョン・アーキテクチャは、多くのシステムにおいて極めて現実的なアプローチと見なされるようになりました。

周波数プランからの視点

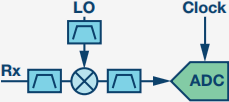

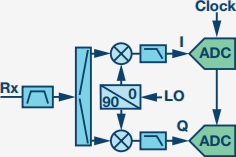

これら3つのアーキテクチャのブロック図と周波数プランの例を図1に示します。図1aは、動作帯域をADCの第2ナイキスト・ゾーンにミキシングするハイサイドLOを備えたヘテロダイン・レシーバーの例です。処理に際し、信号は更に第1ナイキスト・ゾーンにエイリアスを発生させます。図1bはダイレクト・サンプリング・レシーバーの例です。動作帯域は第3ナイキスト・ゾーンでサンプリングされ、エイリアスは第1ナイキスト・ゾーンに発生します。NCOは帯域の中央に置かれ、デジタル的にベースバンドへダウンコンバートした後にフィルタリングとデシメーションが行われて、チャンネル帯域幅に見合う値までデータ・レートが下げられます。図1cにダイレクトコンバージョン・アーキテクチャの例を示します。デュアルADCと直交復調器を接続することによって、チャンネル1がI(同相)信号をサンプリングし、チャンネル2がQ(直交)信号をサンプリングします。

図1. 周波数プランの例

今日の多くのADCは、3つのアーキテクチャをすべてサポートしています。例えば、AD9680はプログラマブル・デジタル・ダウンコンバージョン機能を備えた1.25GSPSのデュアルADCです。このタイプのデュアルADCは2チャンネルのヘテロダイン・アーキテクチャとダイレクト・サンプリング・アーキテクチャをサポートしています。あるいは、このコンバータをペアにすればダイレクトコンバージョン・アーキテクチャで使用できます。

ダイレクトコンバージョン・アーキテクチャのイメージ除去に関する課題は、ディスクリート実装で解決することが非常に困難な場合があります。デジタル方式を利用した処理と組み合わせて更に統合化を進めることで、I/Qチャンネルの良好なマッチングを実現し、イメージ除去性能を大幅に改善することができます。図2は最近発売されたAD9371のレシーバー部分で、これはダイレクトコンバージョン・レシーバーですが、図1cと同様の構成になっています。

図2. AD9371のレシーバー部分:モノリシック・ダイレクトコンバージョン・レシーバー

スプリアス・ノイズ

周波数変換を伴う設計では、帯域内への不要な周波数の折返しを最小限に抑えるために、かなりの努力が必要です。これは周波数プランニングに関わる技術であり、使用可能な部品間のバランスを取ることと、実用的なフィルタ設計をすることが求められます。スプリアスの折返しに関わる問題のいくつかについて、その概要を説明します。また、更に詳細な内容を知りたい設計者のために各種の資料を示します。

ADC入力周波数の折返しと最初の2つの高調波を、ナイキスト帯域周波数に対する入力周波数の関数として図3に示します。チャンネル帯域幅がナイキスト帯域幅よりはるかに小さい場合、レシーバー設計者の目標は、折り返した高調波がチャンネル帯域幅の外側になるような動作点を選ぶことです。

図3. ADCの周波数折返し

レシーバーのダウンコンバージョン・ミキサーには、その構造を複雑にするもう1つの要因があります。すべてのミキサーはデバイス内に高調波を発生させます。更にこれらの高調波がミキシングされることによって、新たな周波数が生じます。この現象を図4に示します。

図4. ダウンコンバージョン・ミキサーのスプリアス

図3と図4には、3次までのスプリアスだけを示しています。実際、これらは更に高次のスプリアスで、設計者にとって即、スプリアス・フリー・ダイナミック・レンジの問題となります。比帯域幅がより狭い場合は、細部にわたる慎重な周波数プランニングを行うことで、ミキサー・スプリアスに関する問題を克服することができます。ミキサー・スプリアスに関する問題は、帯域幅が広くなるほど大きな障害となります。ADCのサンプリング周波数が高くなると、ダイレクト・サンプリング・アーキテクチャに低スプリアス性能を持たせるほうがより現実的な場合があります。

レシーバー・ノイズ

レシーバー設計では、ノイズ指数(NF)を最小限に抑えることに多くの努力が払われます。ノイズ指数はS/N比の低下を表す量です。

部品やサブシステムのノイズ指数の影響は、そのノイズ指数の分だけ出力ノイズ電力が増加して、熱ノイズとゲインのレベルを超えることです。

カスケード・ノイズ指数は次式で計算されます。

ADC前段のレシーバー・ゲインを選択し、ADCの必要なS/N比を決定する場合、合計レシーバー・ノイズ指数と瞬時ダイナミック・レンジのバランスを考慮します。考慮すべきパラメータを表したグラフを図5に示します。説明のためレシーバー・ノイズが示されていますが、これはADC前段のアンチエイリアシング・フィルタによって処理されます。また、ADCノイズはフラットな白色ノイズとして、対象信号は−1dBFSでの連続波(CW)トーンとして示されています。

図5. レシーバーとADCのノイズ

まず、単位をdBmまたはdBFSに統一する必要があります。ADCノイズのdBFSからdBmへの変換は、コンバータのフルスケール・レベルとコンバータのノイズ密度から行うことができます。更に、ノイズ電力は帯域幅に比例するので、共通の帯域幅単位が必要です。チャンネル帯域幅を使用する設計者もいますが、ここでは1Hz帯域幅に正規化してノイズ電力を/Hzとします。

合計ノイズは次式で計算されます。

ここからADCの感度喪失という概念が生じます。ADC感度喪失とは、ADCによるレシーバー・ノイズ性能の低下の度合いを表す量です。この性能低下を最小限に抑えるには、レシーバー・ノイズがADCノイズより十分に大きいことが必要です。この制限はダイナミック・レンジの形で示され、レシーバーのゲインが大きくなると、ADCが飽和することなく受信できる最大信号が制限されます。

したがって設計者は、常にダイナミック・レンジとノイズ指数のバランスという課題に直面することになります

まとめ

以上、ヘテロダイン、ダイレクト・サンプリング、およびダイレクトコンバージョン方式のレシーバー・アーキテクチャについて、それぞれの利点と課題を中心に検討すると共に、レシーバー設計における最近の傾向と検討事項を示しました。より広い帯域幅を求める世界的な需要とGSPSデータ・コンバータの進歩によって、将来的には様々なレシーバー設計が急速に広がっていくことが予想されます。

著者について

この記事に関して

産業向けソリューション

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}