概要

A/Dコンバータ(ADC)は、外部からアナログ信号を取得する必要があるシステムに不可欠なコンポーネントです。そうしたシステムは、通信用のレシーバ、テスト/計測システム、防衛/航空宇宙など、さまざまな分野のさまざまな用途で使われています。いずれの場合も、ADCは、外部の情報を含むアナログ信号をデジタル・データに変換し、デジタル領域で処理するために使用されます。最近のADC製品(IC)は、65nm~28nmクラスのCMOSプロセスなど、半導体の製造技術が進化したことにより、GSPS(ギガサンプル/秒)レベルのサンプル・レートという大きな障壁を克服しています。その結果、システム設計者は、より広い帯域幅を対象としてアナログ信号のサンプリングを行い(つまり、RF信号のサンプリングを行い)、より高度なデジタル処理を実施できるようになりました。その一方で、システム設計者は、環境やコストへの対応を図るために、消費電力の削減にも絶えず取り組んでいます。従来、ADCのメーカーは、GSPSレベルのサンプル・レートに対応するADC(以下、GSPS ADC)で最高の性能を得るために、低ノイズのLDOレギュレータ( 以下、LDO) によって電力を供給することを推奨していました。LDOとは、ドロップアウト電圧の小さいリニア・レギュレータのことです。しかし、LDOは、電源供給回路(PDN:Power Delivery Network)の構成要素としては高い電力効率が得られるタイプのものではありません。そのため、システム設計者には、ADCの性能を大幅に低下させることなく、高い効率で電力供給を行えるようにすることが求められています。つまり、スイッチング方式のDC/DCコンバータ(以下、スイッチング・レギュレータ)からGSPS ADCに直接電力を供給するということです。そのためには、GSPS ADCの性能が損なわれないように、PDNのレイアウト/実装を注意深く行わなければなりません。

本稿では、まずLDOとスイッチング・レギュレータのそれぞれを使用する場合の違いについて説明します。そのうえで、システムの電力効率を高めるためにスイッチング・レギュレータを適用しても、GSPS ADCの性能を低下させずに済むことを示します。また、実装方法の異なる複数種のPDNを使用した場合のGSPS ADCの性能を紹介します。さらに、コストと性能の比較も行います。

従来推奨されていたPDN

帯域幅が広く、サンプル・レートの高いADC(その代表例がGSPS ADC)には、通常、アナログ回路用のAVDDやデジタル回路用のDVDDなど、複数の電源ドメインが存在します。また、半導体製造プロセスの微細化に伴い、電源ドメインの数だけではなく、必要な電圧の種類も増加しました。例えば、アナログ・デバイセズ(ADI)の「AD9250」1は、分解能が14ビット、サンプル・レートが170MSPS(メガサンプル/秒)/250MSPSで、JESD204Bに対応するデュアルADCです。このICは180nmのCMOSプロセスで製造されています。AVDD、DVDD、DRVDDの3つの電源ドメインがありますが、いずれのドメインにも1.8Vの電圧を供給します。

一方、「AD9680」2は、分解能が1 4 ビット、サンプル・レートが1.25GSPS/1GSPS/820MSPS/500MSPSで、JESD204Bに対応するデュアルADCです。このICは、65nmのCMOSプロセスを使用して製造されています。AVDD1、AVDD1_SR、AVDD2、AVDD3、DVDD、DRVDD、SPIVDDという7 種の電源ドメインがあり、1.25V、2.5V、3.3Vの3種の電圧を使用します。

このように、電源ドメインと電圧の種類が増加している理由は、高いサンプル・レートでの動作に必須だからです。さまざまな回路ドメイン(サンプリング、クロック、デジタル、シリアライザなど)の間に適切なアイソレーションを確保し、最高の性能を実現するうえで必要になるということです。このような理由から、ADCのメーカーは、各製品向けの評価用ボードを自ら設計し、リスクを最小限に抑えつつ最高の性能を実現できるように綿密な電源設計を行うことを推奨しています。図1に示したのは、AD9680の評価用ボードで使用されているデフォルトのPDNのブロック図です。この評価用ボードは、VITA 57.1規格に準拠したFMC(FPGAメザニン・カード)コネクタから供給される12V/1Aと3.3V/3Aを主電源とします。サーマル・シャットダウンの状態に移行することなくLDOを制御できるように、「ADP2384」3と「ADP2164」4の両スイッチング・レギュレータを使用して、管理可能なレベルまで2つの主電圧を降圧しています。

このPDNは、計7個のLDO(ドメインごとに1個ずつ)を使用した高コストの実装であることに気づくでしょう。性能面では最適だと言えますが、最も優れた費用対効果、最も効率的な運用コストを実現するものではありません。システム設計者にとって、複数のADCを搭載するシステムを実装するのは容易なことではありません。例えば、フェーズド・アレイ・レーダーでは同期のとれた数百個のADC(AD9680)を使用します。数百個のADCに対し、電源ドメインごとに1個のLDOを配置するといった設計を行うのは合理的とは言えません。

より簡素なPDN

PDNにおいて、電圧の値が等しい複数のドメインに1つのLDOから電力を供給するという設計も考えられます。例えば、1.25Vの複数のアナログ・ドメインをひとまとめにして給電するということです。この方法であれば、費用対効果が高くなります。また、部品点数(部品にかかるコスト)も削減できます。実際、このような設計が適しているアプリケーションも存在します。図2に、AD9680の評価用ボード向けに、実装を簡素化したPDNを示しました。この実装では、3.3Vの単一の主電源を基に、AD9680に必要なすべての電源電圧を生成/供給しています。

スイッチング・レギュレータによる給電

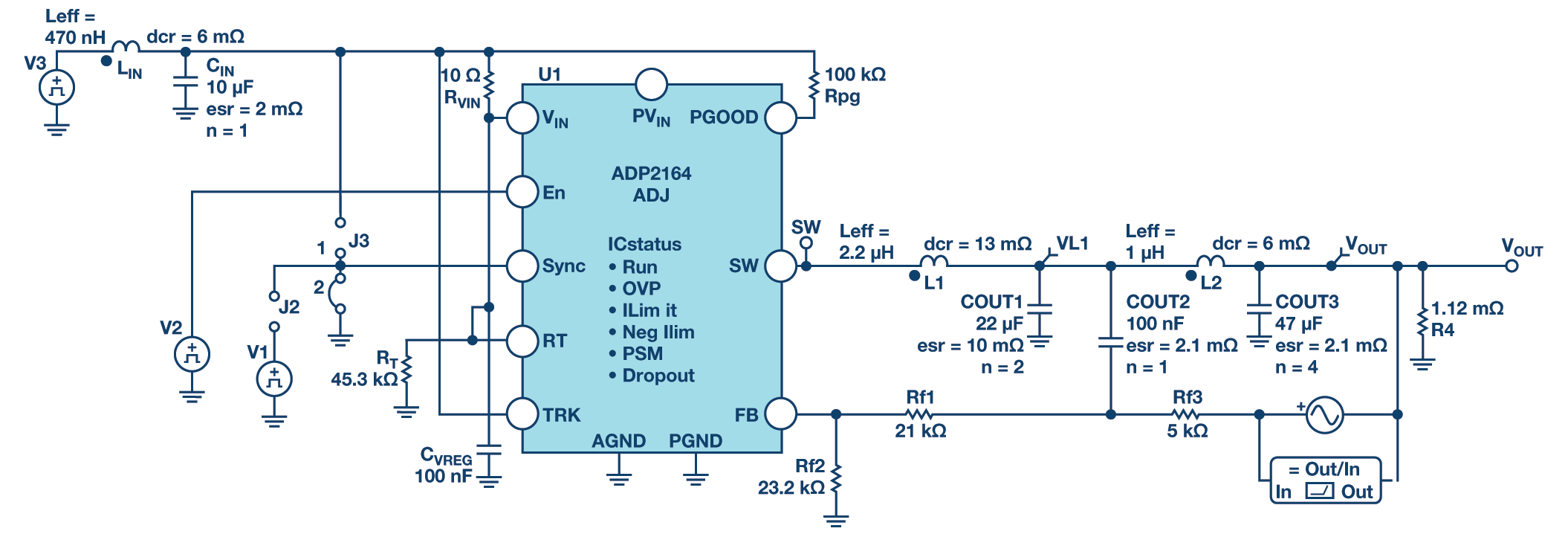

1.25Vのすべてのドメインに電力を供給するLDOを取り除けば、PDNをさらに簡素化できます。これは最も効率的で費用対効果の高いソリューションだと言えます。その場合の課題は、ADCの性能に影響が及ばないようにスイッチング・レギュレータの動作を安定させることです。図3のPDNでは、1.25Vのすべてのドメイン(AVDD1、AVDD1_SR、DVDD、DRVDD)に、ADP2164から電力を供給しています。

各種PDNの比較

上述した3種のPDNを使用した場合に、それぞれどのような特性が得られるのか評価を行いました。比較のために、AD9680の評価用ボード上でベンチトップ型の電源装置から電力を供給した場合の評価結果も示します。表1は、計4種の電源供給方法についてまとめたものです。

表1. 電源供給方法の一覧

| PDNの種類 |

説明 | ||

| ベンチトップ型 | AD9680には、ベンチトップ型の電源から給電 | ||

| PDN #1 |

評価用ボードに実装された

デフォルトのPDN(図1) |

||

| PDN #2 |

1.25Vのすべてのドメインに対し、

1つのLDOから給電 |

||

| PDN #3 | 1.25Vのすべてのドメインに対し、 1つのスイッチング・レギュレータから給電 |

||

なお、SPIVDD(図1参照)には1.8V~3.3Vの電圧を使用できます。これは重要なノードではないと考えられるので、1.8V出力のLDOによって電力を供給しました。現実のシステムでは、SPIVDDは2.5Vまたは3.3Vの電源ドメインに接続するよう実装することができます。ただし、多数のADCやD/Aコンバータ(DAC)がSPI(Serial Peripheral Interface) バスを共有しているシステムでは、SPIVDDを監視しなければなりません。その場合、通常のSPIの動作によってSPIVDDのドメインで電源の過渡的な変動が生じないように注意する必要があります。そうした変動により、SPIVDDがパワーオン・リセット(POR)の閾値より低くなり、同機能にトリガがかかってしまうかもしれないからです。

表2. S/N比の比較〔dBFS〕

| 周波数 (MHz) | ベンチトップ型 | デフォルトのPDN (PDN #1) | 簡素化したPDN (PDN #2) | スイッチング・レギュレータを使用したPDN(PDN #3) |

| 63 |

66.5 |

66.5 |

66.6 |

66.7 |

| 170 |

66.4 | 66.1 | 65.9 | 66.2 |

| 340 | 64.8 | 64.5 |

64.5 | 64.7 |

| 450 | 64.0 | 63.7 | 63.6 | 63.8 |

| 765 | 62.5 | 62.2 | 62.2 | 62.3 |

| 985 | 61.3 | 61.0 |

61.0 | 61.1 |

| 1283 |

59.8 |

59.5 |

59.5 | 59.5 |

| 1725 | 57.7 | 57.4 | 57.4 | 57.5 |

| 1983 | 56.7 | 56.4 | 56.5 | 56.6 |

表3. SFDRの比較〔dBFS〕

| 周波数 (MHz) | ベンチトップ型 | デフォルトのPDN (PDN #1) | 簡素化したPDN (PDN #2) | スイッチング・レギュレータを使用したPDN(PDN #3) |

| 63 |

83 |

82 |

88 |

83 |

| 170 |

86 | 85 | 85 | 84 |

| 340 | 77 | 76 |

76 | 76 |

| 450 | 72 | 72 | 71 | 71 |

| 765 | 77 | 76 | 76 | 82 |

| 985 | 77 | 76 |

76 | 83 |

| 1283 |

74 |

74 |

74 | 75 |

| 1725 | 67 | 67 | 68 | 67 |

| 1983 | 60 | 60 | 60 | 60 |

表2と表3は、各PDNを使用した場合にAD9680のS/N比とSFDRがそれぞれどのようになるのかを示したものです。各ナイキスト・ゾーンに対応するためのフロントエンド回路とレジスタの設定については、AD9680のデータシートに記載された推奨値に従いました2。

表中の「PDN #3」は、スイッチング・レギュレータによってAD9680の1.25Vドメインに電力を供給する図3のPDNを使用した場合の結果です。ご覧のように、入力周波数の全体にわたって良好な性能が得られています。これは、複数のドメインに単一のスイッチング・レギュレータから電力を供給しても、ADCの性能は大幅に低下していないということを意味します。つまり、良好な性能を維持したまま、高い電力効率と費用対効果が得られるということです。また、ベンチトップ型の電源装置を使えば、最もノイズが少ない電源電圧を得ることができます。このことから、電源装置を使用するPDNでは最高のノイズ性能が得られます。その一方で、PDN #3を使用した場合、デフォルトのPDN(PDN #1)を使用した場合よりもS/N比が0.1dB~0.2dBほど高くなっています。この点は注目に値します。LDOは低い周波数のクリーンアップには有効ですが、数100kHzを上回るとそれほどの効果は得られません。そのため、このような結果になるのです。

FFTによる分析

図4と図5 は、PDN # 3 を使用し、それぞれ170MHz、785MHzのシングルトーンを入力した場合の出力をFFTした結果です。1.25Vのすべてのドメインに単一のスイッチング・レギュレータから電力を供給しても、特性は劣化しないことがわかります。

スイッチング・スプリアス

スイッチング・レギュレータを使用する場合、ノイズ性能に加え、スイッチング素子と磁性部品によって生じるスプリアスに注意する必要があります。また、グラウンド・ループとグラウンド・バウンスを低減できるよう慎重にPDNのレイアウトを行う必要があります。それにより、良好な結果を得ることが可能になります。スイッチング・レギュレータのノイズ測定に役立つリソースはたくさんあります5、6。スイッチング・スプリアスは、基本波の両側に、スイッチング周波数(この例では1.2MHz)の分だけオフセットした位置に現れます。図2、図3を見ると、スイッチング・レギュレータの出力部には2段構成の出力フィルタが配置されています。このフィルタがスイッチング・ノイズ(リップル)の低減に大きく寄与し、ADCのノイズ性能(S/N比)が維持されます。また、このフィルタは、FFT結果に現れているスイッチング・スプリアスの低減にも役立ちます。図6と図7に、170MHz、785MHzのシングルトーンを入力した場合のスイッチング・スプリアスを示しました。

( スプリアスのレベルは- 105dBFS )

( スプリアスのレベルは- 94dBFS )

スイッチング・スプリアスのレベルは、電源電圧変動除去比(PSRR)やADCの電源ドメインについて把握することで推定できます7。

レギュレータ回路のシミュレーション

スイッチング・レギュレータの出力に配置する2段構成のフィルタは、「ADIsimPE」などのツールを使用してシミュレーションすることができます8。図8に、ADIsimPEでPDNの出力ノイズと安定性をシミュレーションするための回路図を示しました。ADIsimPEは、システム設計者が電源回路の設計、最適化、解析を行ううえで非常に役立つ強力なツールです。

図9に、ADIsimPEによるシミュレーションの結果を示しました。2段構成のフィルタにおける1段目の出力リップルと、2段目の出力をプロットしています。リップルの大きさは約3mVp-pです。

部品表

前掲の図2は、AD9680の評価用ボードにデフォルトで実装されているPDNを簡素化したものです。このPDNは、表4に示した部品によって構成されています。これに対し、図3に示したPDNであれば、部品にかかるコストを40%~45%削減することができます。なお、部品のコストは、一般的な電子部品ベンダーのウェブサイトに掲載されている1000個単位の価格を使って見積もります。

表4. 図2に示したPDNの部品表

| 記号 | 個数 |

説明 |

メーカー |

部品番号 |

値 |

| C1 |

1 | コンデンサ:22μF、6.3V、X5R 0805 | 村田製作所 |

GRM21BR60J226ME39L |

22 µF |

| C2 |

4 | コンデンサ:22μF、6.3V、X5R 0805 | 村田製作所 |

GRM21BR60J226ME39L |

22 µF |

| Cf | 1 | コンデンサ:0.1μF、10V、X5R 0402 | 村田製作所 | GRM155R61A104KA01D |

0.1 µF |

| C3, C4, C5, C6, C7, C8, C9, C10, C11, C12, C13, C14, C15, C16, C17, C18, C19 | 17 | コンデンサ:4.7μF、6.3V、X5R 0402 | 村田製作所 |

GRM155R60J475ME47D | 4.7 µF |

| E1, E2, E3, E4, E5, E6 | 6 | フェライト・ビーズ:10Ω、0402 | 村田製作所 | BLM15AX100SN1D | 10 Ω |

| L1 | 1 | シールド付きパワー・インダクタ:1.0μH、10mΩ | Coilcraft社 |

XAL5030-102ME | 1.0 µH |

| L2 | 1 | シールド付きパワー・インダクタ:2.2μH、0.1Ω | Coilcraft社 |

ME3220-222ML | 2.2 µH |

| Rf1 | 1 | 抵抗:4.99kΩ、1% 1、W/10 W 0402 | パナソニック | ERJ-2RKF4991X | 4.99 kΩ |

| Rf2 | 1 | 抵抗:41.2kΩ、1% 1、W/10 W 0402 | パナソニック | ERJ-2RKF4122X | 41.2 kΩ |

| Rb | 1 | 抵抗:23.2kΩ、1% 1、W/10 W 0402 | パナソニック |

ERJ-2RKF2322X | 23.2 kΩ |

| ADP2164 | 1 | IC:レギュレータ、降圧型、調整可能、4A、 同期式、16リードLFCSP |

ADI | ADP2164ACPZ-R7 | |

| ADP1741 | 3 | IC:レギュレータ、LDO、調整可能、2A、 16リードLFCSP |

ADI | ADP1741ACPZ-R7 | |

| ADP171 | 2 | IC:レギュレータ、LDO、調整可能、0.3A、 5リードTSOT-23 |

ADI | ADP171AUJZ-R7 |

部品の選択とレイアウト

本稿で紹介したように、ADC用のPDNにはいくつかのバリエーションが考えられます。ADCの性能はPDNに依存するので、設計を慎重に行う必要があります。PDNに使用する部品とプリント回路基板のレイアウトにより、ADCの性能が大きく変動する可能性があるということです。プリント回路基板には、マッチング回路で使われるインダクタや、アナログ信号/クロック信号のカップリングに使用するトランスなどの磁性部品が実装されます。これらの部品には、スイッチング・レギュレータで生成される大電流によって、強力な磁界がカップリングされます。そうした磁界から重要な信号に影響が及ぶことを避けるには、プリント回路基板のレイアウトを慎重に行わなければなりません。

インダクタの選択

出力フィルタで使用するインダクタとコンデンサは、大量の電力の供給に使われるため、これらの部品は慎重に選択する必要があります。本稿の例では、シールド付きのインダクタとシールドがないインダクタを組み合わせて使用しました。フィルタの1段目には、シールド付きのインダクタを使っています。そうすれば、2段目はシールドのないインダクタで対応できます。ただし、EMI(電磁波干渉)の放射を最小限に抑えたい場合には、1段目、2段目ともにシールド付きのインダクタを使用することをお勧めします。インダクタの飽和や過剰な電圧降下が発生しないように、飽和電流(ISAT)とDC抵抗(DCR)について十分なヘッドルームを確保できる製品を選択しました。

コンデンサの選択

出力フィルタでは、X5RまたはX7Rのコンデンサを使用することを推奨します。その際には、必ず等価直列抵抗(ESR)の小さい製品を選択してください。ESRが小さければ、スイッチング・レギュレータの出力リップルを抑えることができます。また、コンデンサを並列に接続すれば、トータルのESRと等価直列インダクタンス(ESI)を最小限に抑えることが可能です。図3、表4に示したように、フィルタの1段目では22μFのコンデンサを2個使用し、2段目では22μFのコンデンサを4個使用しています。コンデンサを選択する際には、定格電圧も重要な要素となります。DCバイアスの増加に伴って、セラミック・コンデンサの誘電性が低下するからです。定格電圧が6.3Vで容量が2 2 μ Fのコンデンサは、4VのDCバイアスによって誘電性が最大50%低下します9、10。本稿の例では、1.25Vの電源用に定格電圧が6.3Vのコンデンサを使用しました。出力に多くのコンデンサを追加すると、基板上の占有面積とコストが増加します。しかし、それによって、ADCの性能を低下させる原因となるスイッチング・ノイズとリップルを低減することができます。

フェライト・ビーズの選択

図3 に示すように、各ドメインのアイソレーションにはフェライト・ビーズを使用しています。フェライト・ビーズのDC抵抗が必要以上に高いと、各ドメインにおける供給電圧が最適な値よりも低くなります。したがって、フェライト・ビーズの選択も重要です。供給電圧が下がると、ADCの最適な性能( S/N比やSFDR) が得られません。フェライト・ビーズのインピーダンス特性、DC特性の最大許容値、DC抵抗には十分な注意を払う必要があります11。

基板レイアウトで考慮すべき事柄

スイッチング・レギュレータがADCに及ぼす影響を最小限に抑えるには、スイッチング・レギュレータとそのスイッチング素子を、ADCに影響を及ぼすあらゆる磁性部品から十分に離れた場所に配置する必要があります。そうした磁性部品は、フロントエンドのマッチング回路やクロック回路などで使われているはずです。また、ループ電流を最小限に抑えるには、2段構成のフィルタをスイッチング・レギュレータのできるだけ近くに配置する必要があります。

まとめ

GSPS ADCを使用すれば、広範な帯域幅を対象としてアナログ信号をデジタル化することができます。それにより、システム設計には大きなメリットがもたらされます。GSPS ADCを使用する場合、PDNの複雑さを軽減し、実装面積とコストを削減することが重要になります。設計、部品の選択、プリント回路基板のレイアウトに十分な注意を払うことで、ノイズが少なく費用対効果が高いPDNを実現することが可能になります。そのように実装されたスイッチング・レギュレータを使えば、GSPS ADCの性能を低下させることなく、電源システムの効率を向上し、部品と運用にかかるコストを削減することができます。

参考資料

1AD9250. Analog Devices

2AD9680. Analog Devices

3ADP2384. Analog Devices

4ADP2164. Analog Devices

5Akdrick Limjoco「スイッチング・レギュレータの出力ノイズを理解し、電源の設計を加速する」Analog Dialogue 48-08

6「Output Ripple and Noise Measurement Methods for Ericsson Power Modules」Ericsson.

7Rob Reeder、技術記事MS-2210「高速ADCの電源回路設計で考慮すべきこと」Analog Devices

8ADIsimPE. Analog Devices

9GRM21BR60J226ME39L 、村田製作所

10Istvan Novak, Kendrick Barry Williams, Jason R.Miller, Gustavo Blando, and Nathaniel Shannon「DC and AC Bias Dependence of Capacitors」DesignCon2011

11Jefferson Eco、Akdrick Limjoco AN-1368 アプリケーション・ノート「フェライト・ビーズの特性を知る」Analog Devices