はじめに

ガス/石油のプラントや発電所など、ハイエンドのFA(Factory Automation) を必要とする分野では、EMI(電磁干渉)の抑制、小型化、信頼性の向上、コストの削減といったことが求められます。そのため、チャンネル間の絶縁が特に難易度の高い課題となります。結果として、標準的なモジュールにおけるチャンネルの密度は4チャンネルから8チャンネル程度までに制限され、チャンネル間の絶縁性能は数百V程度に抑えられます。

本稿では、まずプロセス制御に使用するアナログ入力モジュールに対し、以前から適用されてきた絶縁手法について簡単に説明します。次に、それらの方法に代わるものとして、密度が高く設計が容易なチャンネル間絶縁型のアーキテクチャについて解説します。さらに、その具体例として2.5kVrmsのチャンネル間絶縁性能を備える16チャンネルのデモ・モジュールを取り上げます。最後に、そのモジュールがEN 55022のクラスBに定められた絶縁規格に適合することを示す試験結果を紹介します。

プロセス制御に使用するアナログ入力モジュールの絶縁

ガルバニック絶縁とは、物理的かつ電気的に分離された2つの回路に対し、直接的な伝導経路を設けることなくデータと電力を相互に交換できるようにすることです。一般的には、トランス、フォトカプラ、あるいはコンデンサを使用して実現されます。絶縁を適用する理由としては、回路や人間の保護、グラウンド・ループの切断、コモン・モード電圧やノイズ除去性能の改善などが挙げられます。

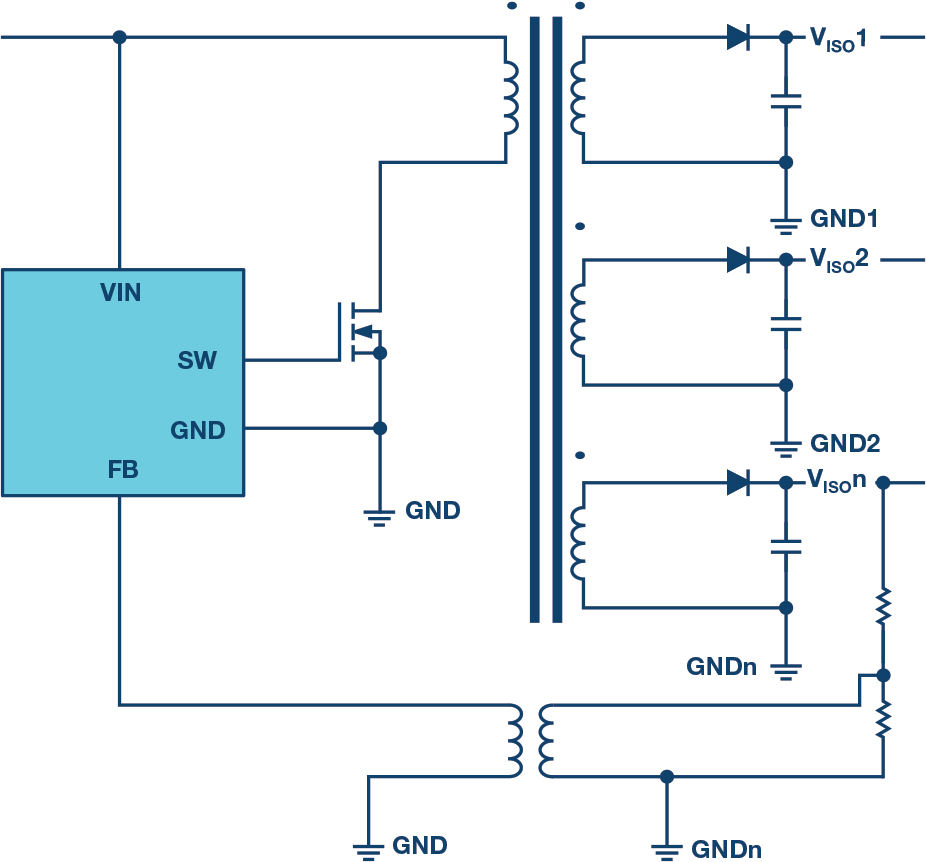

通常、プロセス制御システムの入力部には、グループ絶縁またはチャンネル間絶縁が適用されます( 図1) 。グループ絶縁では、複数の入力チャンネルを、電源絶縁と信号絶縁が可能な単一の絶縁バリアを共有する1つのグループとしてまとめます。この方法には、チャンネル間絶縁よりもコストを抑えられるというメリットがあります。しかし、1つのグループに含まれるチャンネル間のコモン・モード電圧の差に制約があり、全てのチャンネルを同じ領域に配置しなければなりません。図1の右側にチャンネル間絶縁の方法を示しました。こちらの方が、堅牢性が高く、間違いなく効果的です。ただし、チャンネル当たりのコストがかなり高くなるので、システムを構築する際にはトレードオフについて慎重に検討する必要があります。

チャンネル間絶縁を適用する場合、全てのチャンネルに対してそれぞれ個別に電源絶縁と信号絶縁を施さなければなりません。絶縁は、入力モジュールのチャンネル密度、EMI、コスト、信頼性に影響を及ぼす主要な要因の1つです。最新の設計手法では、チャンネルごとにデジタル・アイソレータを1つずつ使用することによってデータ絶縁を実現します。そのような用途に一般的に使用される製品の1つにアナログ・デバイセズの「ADuM141E」があります。このデジタル・アイソレータは16リードのSOIC(6.2mm×10mm)というパッケージに4つの絶縁データ・チャンネルを収容しています。ただ、この製品を使う場合でも、やはり電源絶縁はチャンネルごとに必要になります。そこで、以下では以前から使用されてきた3つの電源絶縁手法を紹介します。3つの手法とは、それぞれマルチタップ・トランス、プッシュプル設計、絶縁型DC/DCモジュールを適用するというものです。

図2に示したのは、マルチタップ・トランスを用いたフライバック絶縁型DC/DCのアーキテクチャです。フライバック・コンバータによってトランスを駆動することで、複数のタップに対応する複数の出力が生成されます。これは、電源のアーキテクチャとして確立されたものです。しかし、プロセス制御のアプリケーションで使うものとしては、以下に示す6つの大きな欠点があります。

- EMIを制御するために、カスタマイズされたマルチタップ・トランスとシールドが必要。十分な信頼性を確保しつつ小さなフォームファクタで実現するのは難しい

- 1つのチャンネルにしかフィードバック制御ループを適用できず、それ以外のチャンネルでは調整の精度が低くなる。したがって、信頼性の高い動作を保証するには慎重な評価が必要

- チャンネル密度がトランスの配置からの制約を受ける。各タップからの電力の出力に向けて、トランスはアナログ入力モジュールの中央に配置される。各入力チャンネルはトランスの周囲のファンアウト部分に配置するようにレイアウトされるので、アナログ入力モジュール・カードのチャンネル数は事実上4または8に限られる

- 1つのチャンネルからの干渉が、トランスのタップ間のカップリング・コンデンサを介して他のチャンネルに結合してしまう

- 絶縁耐圧のレベルが低い。マルチタップ・トランスでは、特殊な設計か特殊な絶縁材料を採用しない限り、数百V程度のチャンネル間絶縁しか実現できない。特殊な設計や特殊な絶縁材料を採用すると、トランスのコストが著しく増加してしまう

- カスタマイズしたトランスに対するUL/CSAの認証取得にコストがかかる

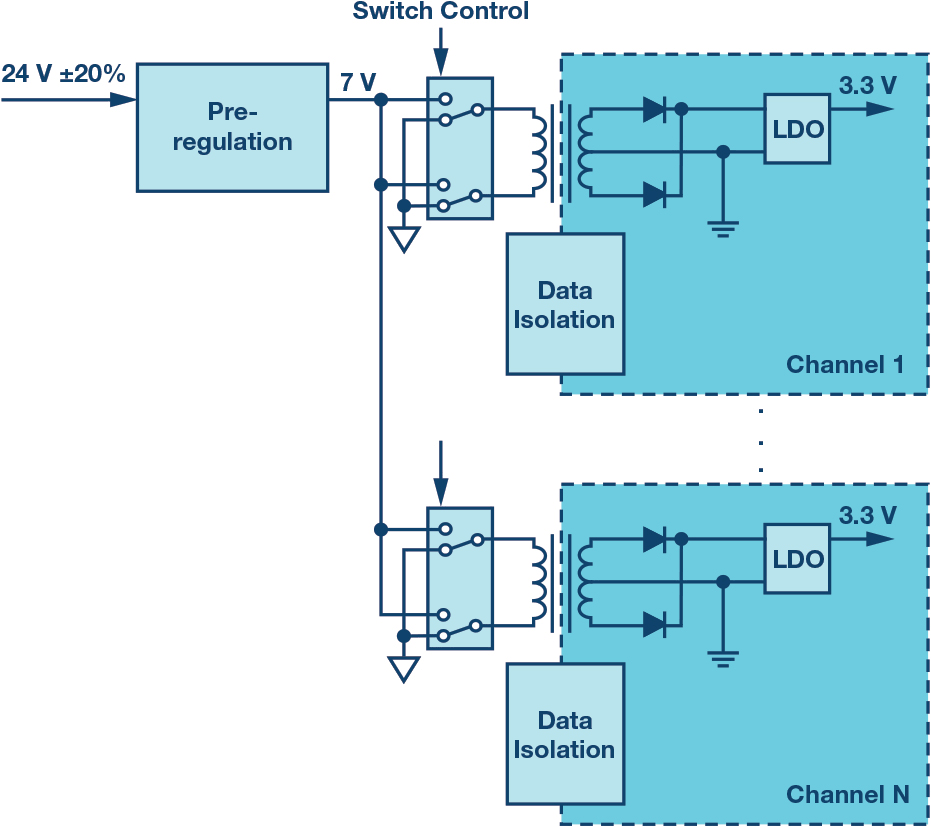

2つ目の方法は、チャンネルごとに個別のトランスを使用し、プッシュプル方式で各チャンネルを絶縁するというものです。この方法では、フィードバック制御は使用しません。まず、高い精度で調整された電源(7Vなど)によって各トランスを駆動します。そして、2次側では、各トランスがLDO(低ドロップアウト)レギュレータを駆動するようにすることで、さらに出力電圧の調整を行います。これは、2次側の電流が比較的少なく、十分に調整が可能であることから実現できる方法です。

この方法の欠点としては、まずプリレギュレーションが必要であることが挙げられます。また、チャンネルごとに追加の部品が必要になることも欠点の1つです。トランスとしては、必要に応じて何らかの絶縁定格を満たすものを選択する必要があります。プリレギュレーションに加え、トランス、スイッチ、チャンネルごとのLDOが必要になることから、基板面積が大きくなり、コストも増加します。さらに、全ての条件下で十分なレギュレーションが得られることを保証するために、多くの手間や時間を費やして評価を実施する必要があります。

3つ目の方法は、UL/CSAの認証を受けた表面実装対応の絶縁型DC/DCモジュールを使用することです。これであれば、より容易に電源絶縁を実現できます。また、数千Vの絶縁耐圧を実現しつつ、チャンネル密度を高めることが可能になります。ただし、この方法は比較的コストがかかることに加え、一般的にはEN 55022のクラスAの要件にしか適合できません。また、そうしたモジュールは、従来、EMIの問題の根源であった可能性もあります。実際、ほとんどのモジュールは、EMI放射を抑えるためにPWMの周波数が1MHz未満となっています。さらに、ほとんどのプロセス制御向けアナログ入力モジュールは、消費電流が10mA未満となっています。市場に提供されているほとんどの絶縁電源モジュールは、それよりもかなり多くの電流を消費します。

これら従来の手法では、必要な絶縁性能やコストを満たすことが困難です。また、チャンネルごとに個別のデータ用アイソレータが必要になり、基板面積とコストが増大します。仮に、電源絶縁の機能をデータ用アイソレータに含めることができるとしたらどうなるでしょうか。実はそれは実現可能なことであり、すでに製品化も行われています。

アナログ・デバイセズのiCoupler® 製品とisoPower®製品は、産業分野や車載分野で広く採用されています。実は、これらの技術は1つのパッケージに統合することができます。その実例が「ADuM5411」です(図4)。この製品は、7.8mm×8.2mmの24リードTSSOPに、完全な電源絶縁の機能と4チャンネルのデータ絶縁の機能の両方を搭載しています。アナログ入力のシグナル・コンディショニングとデジタル変換に十分な最大150mWの出力を備えており、UL1577で定められた2500Vrmsの絶縁耐圧を満たします。また、CMTI(Common Mode Transient Immunity:同相雑音除去性能)は75kV/μsを上回り、発電所など、過渡的な高電圧や大電流にさらされる過酷な産業環境に理想的な製品となっています。

データ絶縁と電源絶縁の両方の機能が高度に集積されていることから、同製品を採用すればアナログ入力モジュールの設計が大幅に簡素化され、チャンネル密度をより高めることができます。従来の絶縁方法では8つのチャンネルしか設けられなかったスペースに、16以上のチャンネルを実装することが可能です。

この絶縁方法を採用し、温度に対応する信号を入力とするモジュール( 以下、温度入力モジュール) を設計しました。各チャンネル間が絶縁された16のチャンネルを備えています(図5)。この温度入力モジュールでは、ADuM5411により、16のチャンネルのそれぞれに対して電源絶縁とデータ絶縁の両方を実現しています。また、集積度の高いフロントエンドIC( 「AD7124」または「AD7792」)を使って熱電対やRTD(測温抵抗体) による温度測定を行うようにすることで、ディスクリート構成の設計よりも基板面積を縮小しています。「ADP2441」は24Vのバックプレーン電源を3.3Vに変換し、それをマイクロコントローラ、タッチ・スクリーン、ADuM5411に供給します。各入力チャンネルに必要なスペースは、わずか63.5mm×17.9mmです。

16チャンネルを備えている

ADuM5411に適したレイアウト設計

この温度入力モジュールは多くのチャンネルを備えています。各チャンネルに使用するADuM5411のスイッチング周波数は125MHzです。そのため、モジュールの基板は、EN 55022のクラスBに対応する電磁干渉試験に確実に合格できるように、細心の注意を払って設計しました。

このモジュールの設計では、EMIの影響(放射)を最小限に抑えるために、消費電力を抑えて電流帰還ループの経路を短くするという方針を採用しました。モジュール全体としての消費電力は、集積度が高く消費電力の少ない温度測定用のフロントエンドICを使用することによって削減しています。それにより、絶縁バリアをまたぐ電力が低減され、放射エネルギーも抑えられます。AD7124はフル動作時の消費電流がわずか0.9mAです。電流帰還ループを短くするために、フェライト・ビーズに加えてスティッチング・コンデンサも利用しました。

フェライト・ビーズは、プリント基板の配線よりもインピーダンスが格段に高く、放射の信号源を制御するための有効な手段となります。図6に示すように、この設計ではADuM5411のピンと直列にフェライト・ビーズを配置しました。フェライト・ビーズの周波数応答は、非常に重要な検討項目です。フェライト・ビーズとしては、100MHz~1GHzの周波数範囲で2kΩ以上のインピーダンスを持つ「BLM15HD182SN1」を使用しました。このフェライト・ビーズは、ADuM5411のパッドにできるだけ近い位置に配置しなければなりません。VISOピンまでのパス上にあるE9とGNDISOピンまでのパス上にあるE10が、使用するフェライト・ビーズの中でも最も重要なものとなります。

帰還経路のインピーダンスを抑えて放射を低減させるうえではコンデンサも役に立ちます。その方法の1つは、安全規格で定められた沿面距離、空間距離、耐電圧の基準を満たす認証取得済みの表面実装型コンデンサを、絶縁バリアをまたいで配置することです。そうしたコンデンサは、村田製作所やVishay Inter technology社などから提供されています。ただし、コンデンサを実装することによってインダクタンスが生じるため、この方法は約200MHzまでの周波数にしか効果がありません。そこで、プリント回路基板においてADuM5411の下部にスティッチング容量を追加するというのが、より有効な方法となります。図7に示すように、浮遊スティッチング・コンデンサまたは重複スティッチング・コンデンサを実装することで効果が得られます。

重複スティッチング・コンデンサ

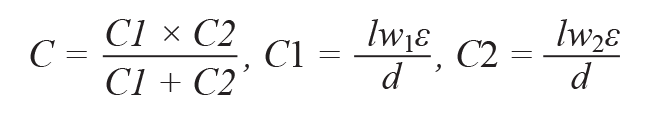

浮遊スティッチング・コンデンサとしては、C1とC2の2つのコンデンサを直列で実装します。その総容量値は、以下の式で求められます。

ここで、εはプリント回路基板に使用される絶縁材料の誘電率です。FR-4基板の場合は4.5となります。

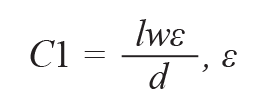

一方、重複スティッチング・コンデンサの容量値は以下の式で求められます。

ここで、εはプリント回路基板に使用される絶縁材料の誘電率です。FR-4基板の場合、4×10-11F/mです。

材料、面積、距離が同じである場合、浮遊スティッチング・コンデンサの総容量は、重複スティッチング・コンデンサの容量の半分になります。絶縁材料の厚さは2 倍です。IEC60950 2.10.6.4では、強化絶縁について、内部層の絶縁材料の厚さは最小0.4mm(15.74mil。1mil は0.0254mm)と定められています。ただ、基本絶縁についてはそのような要件はありません。ADuM5411は2.5kVrmsの基本絶縁にしか対応していないので、この設計では重複スティッチング・コンデンサを選択して容量を大きくすることにしました。同じ理由から、内部層の厚さは5milになるように調整しました。

この温度入力モジュールは、チャンネル間絶縁を適用した16のチャンネルを備えています。そのプリント回路基板には、6層の基板を使用しています。機械的な性能とEMIに対する性能を確保するために、最上層と最下層は20mil、内部層は5milに調整しました(図8)。

図9に示すように、重複スティッチング・コンデンサのプレーンは、GND1、SIG、PWR、GND2に対応するように設けています。GND1とPWRのプレーンはADuM5411の2次側に接続し、SIGとGND2のプレーンはADuM5411の1次側に接続しています。つまり、3つの並列スティッチング・コンデンサが、GND1とSIGの間、SIGとPWRの間、PWRとGND2の間にそれぞれ形成されるということです。重複領域は幅4.5mm、長さ17mmで、総容量値は72pFとなります。

EN 55022に対応する試験の結果

ここまでに説明した回路について、EN55022 に基づき10m の距離で2回のEMI試験を実施しました。1回目の試験では、スティッチング容量を加えた基板( 図10 ) を使用しました。結果は図11 に示したとおりです。約11.59dB のマージンがある状態でEN55022のクラスB に適合しています。2回目の試験では、スティッチング容量は使わず、150pF のコンデンサ「C1812C102KHRACTU 」(KEMET Electronics社製) を外付けした基板を使用しました。このコンデンサは、3kV に対応可能な高い安全性を有するという認証を得ています( 以下、安全コンデンサ) 。その結果は図12のとおりです。この条件でも、0.82dBのマージンがある状態でEN55022のクラスB に適合しました。

EN55022のクラスBに適合している

安全コンデンサを実装した回路の試験結果。

EN55022のクラスBに適合している

上記の試験結果から、安全コンデンサを使用するよりも、ICの下にスティッチング・コンデンサを実装する方がデカップリングに有効であることがわかります。

まとめ

チャンネル間絶縁は、ハイエンドのプロセス制御システムの設計において一般的に遭遇する課題です。アナログ・デバイセズのiso Power技術とi Coupler技術を採用した製品を利用することにより、従来のデジタル絶縁方法や電源絶縁方法を使うよりも格段に高いチャンネル密度を達成できます。また、設計作業は大幅に簡素化され、各チャンネルの堅牢性と信頼性も向上します。スティッチング・コンデンサをプリント回路基板に実装するか、安全コンデンサを追加することによって、EN 55022のクラスA/クラスBに適合するレベルにEMIを簡単に制御することができます。これは実に画期的な技術だといえます。

参考資料

ADuM5411のデータシート、Analog Devices

AN-0971「isoPower デバイスでのEMI 放射制御についての推奨事項」Analog Devices

AN-1349「ADM2582E/ADM2587E(RS-485/RS-422)トランシーバの EMI 放射を最小限に抑えるための PCB実装ガイドライン」Analog Devices