はじめに:進化の時代に技術者が直面する課題

多くのアプリケーション・ボードでは、複数種の電源電圧が必要になります。そこで、本稿では、マルチレール電源の設計について2回に分けて解説しています。電源の設計作業は、3つの段階に分けることができます。(1)設計戦略の策定とICの選択、(2)回路の設計、シミュレーション、テスト、(3)配置と配線の3つです。これらのうち、(1)の設計戦略の策定と(2)のシミュレーションに時間をかければ、設計コンセプトが適切であることを実証することができます。(2)のテストを行うには、実際に回路を構築して各種の測定を実施する必要があります。本稿のPart 1では、主に(1)の設計戦略について解説しました。(2)の設計やシミュレーションについて、アナログ・デバイセズはLTpowerPlanner®、LTpowerCad®、LTspice®、LTpowerPlay®など、無償でダウンロード可能な設計/シミュレーション・ツールを提供しています。また、これらに関する参考資料も数多く公開しています。そこで今回は、(3)の段階に着目することにします。具体的には、電力バジェットと基板レイアウトの話題を取り上げます。コンポーネントを適切に配置/配線することによって、再設計を行うことなく最初から質の高い回路を実現できるようにすることを目的とします。

電源については、サイズ、精度、効率の面で十分なヘッドルームを設けた堅牢な設計を行う必要があります。また、製造時の問題を回避するために、プリント回路基板(ボード)のレイアウトと配線を慎重に行うことが不可欠です。基板レイアウトについては、その最終段階に至る前に、長年の経験を持つ熟練技術者の助けも借りるとよいでしょう。

慎重な設計の効果

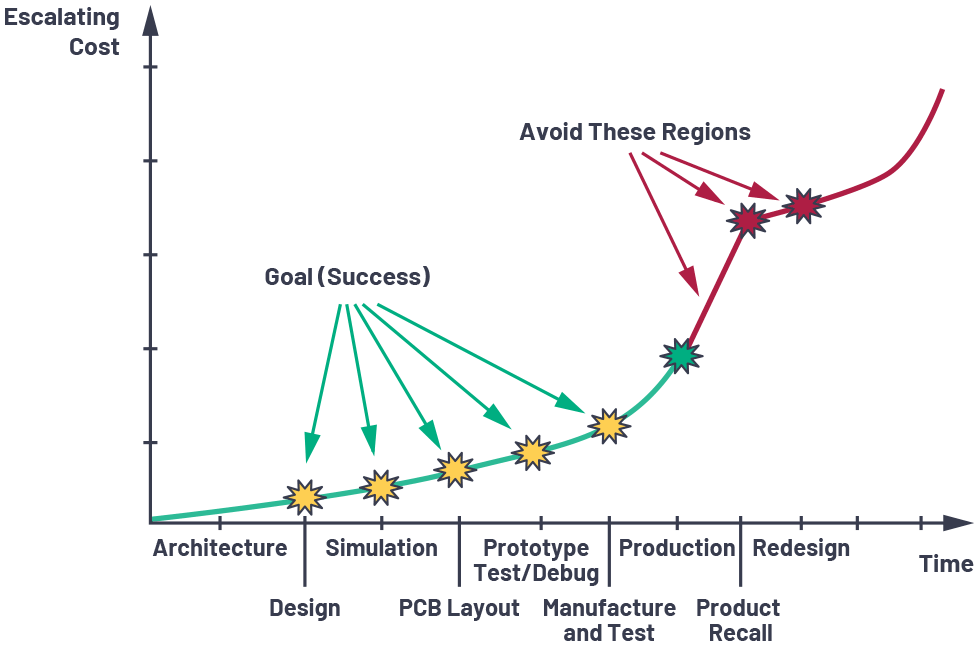

机上で設計した電源回路は適切なものに見え、シミュレーションでも問題は見つからなかったとします。その後、レイアウト、基板の製造、回路を実装したプロトタイプのストレス・テストも滞りなく実施できたとします。しかし、最終的なテストの段階になって問題が発覚することも少なくありません。ここでは、実際の設計例を基に、潜在的な問題を回避するための秘訣やヒントを紹介します。基板の再設計や再スピンにつながりかねない設計上の欠陥や落とし穴を避けるためには、いくつかの重要な概念について理解しておく必要があります。ここで、図1をご覧ください。これは、テストとヘッドルームの分析を慎重に行うことなく直ちに設計から製造に進むと、コストが急激に増加するおそれがあるということを表しています。

電力バジェット

通常の条件下では期待どおりに動作するものの、フル・スピード・モードで動作させたり、不規則なデータが現れ始めたりすると、(ノイズや干渉は排除しているのに)回路全体として誤動作を起こしてしまうことがあります。このような回路には注意が必要です。

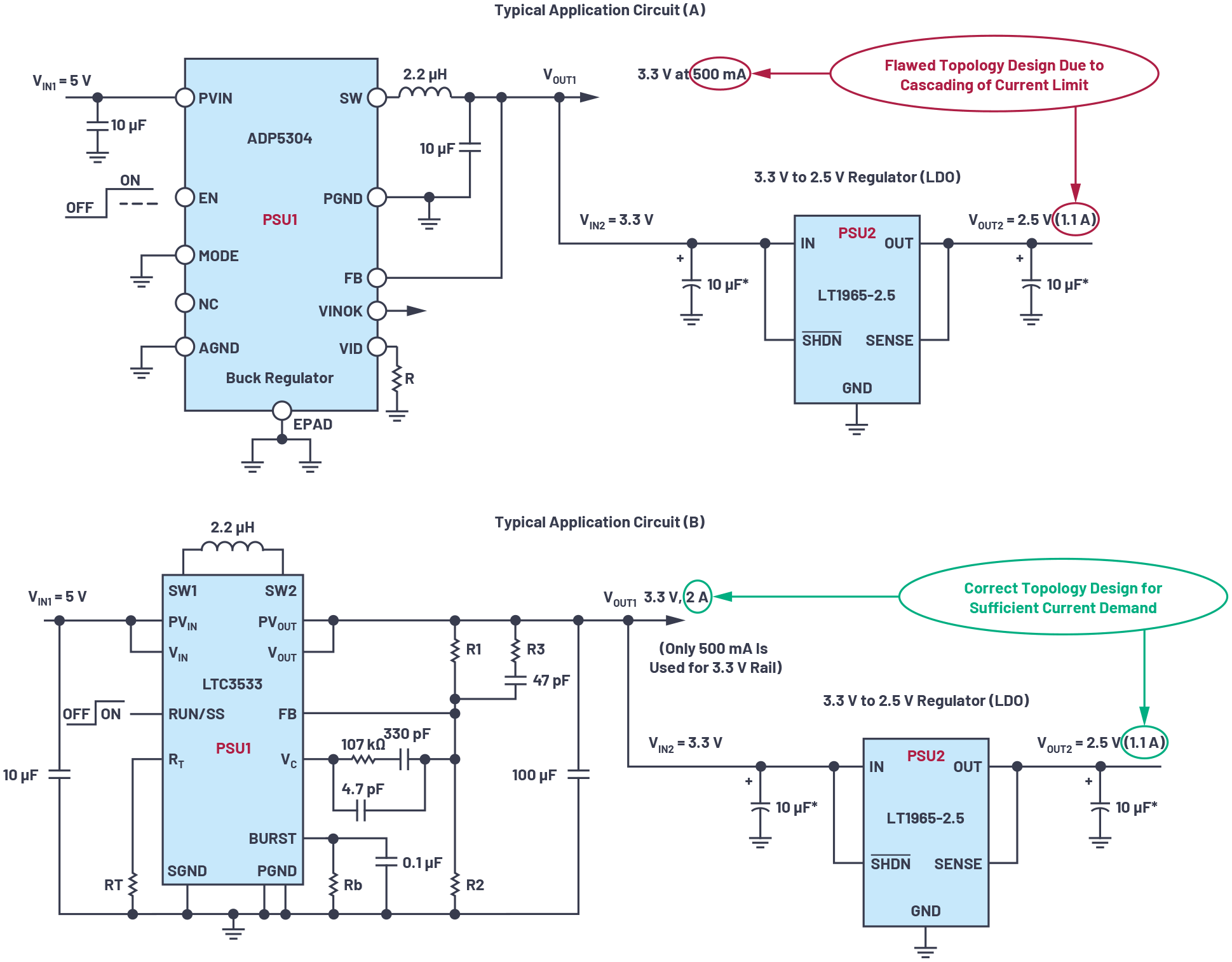

複数のDC/DCコンバータ段をカスケード接続する場合には、必要な電流量がレギュレータICの制限値を超えてしまう状態(以下、電流制限の状態)に陥らないように注意してください。図2に示したのは、カスケード接続で構成した典型的なアプリケーションの例です。この回路では、5Vではなく3.3Vの電圧を入力として2.5Vの電源電圧を得ます。これは、効率を重視するという観点からは適切な設計です。(a)の回路では、初段の電源ユニット(PSU1)として降圧レギュレータ「ADP5304」を使用しています。このICは、出力電圧が3.3Vである場合、最大500mAの電流を出力できます。この3.3Vの出力を2段目の電源ユニット(PSU2)であるLDO(低ドロップアウト)レギュレータ「LT1965」に入力し、2.5Vの出力を生成します。LT1965の最大出力電流は1.1Aです。この回路には、ある典型的な

この回路には、ある典型的な問題が潜んでいます。通常の条件下では、動作に何ら問題は生じません。しかし、回路が初期化されてフル・スピードで動作し始めると問題が発生します。例えば、マイクロプロセッサが動作し始めたり、A/Dコンバータ(ADC)の高速サンプリングが始まったりした場合です。入力された電力以上の電力を出力できるレギュレータは存在しません。そして、図2(a)のVOUT1における最大電力(P = V×I)は、3.3V×0.5A= 1.65Wです。したがって、VOUT1とVOUT2からは計1.65W以上の電力を供給することはできません。しかも、1.65WというのはPSU2の効率が100%の場合の値です。実際には損失が生じるので、利用できる電力は1.65Wよりも少なくなります。この設計では、VOUT2から最大2.75Wの電力が得られることを想定しています。しかし、この値が達成されることはなく、PSU1が電流制限の状態に達し始めると、回路に誤動作が生じます。電流制限の状態が生じるのは、この例のように電源回路を構成したケースに限られるわけではありません。場合によっては、使用しているレギュレータのうちいずれかが過電流の状態に陥り、完全に停止してしまうこともあり得ます。

図2(a)の回路について適切なトラブルシューティングを行えば、PSU1をより多くの電流に対応できる製品に置き換えなければならないということに気づくでしょう。ピン互換の製品が見つかればベストですが、最悪の場合、基板を一から再設計/再スピンしなければならなくなるでしょう。プロジェクトの日程に遅れが生じる危険性を回避するためには、設計コンセプトを固める前の段階で定めた電力バジェットを念頭に置いておくことが重要です(図1)。

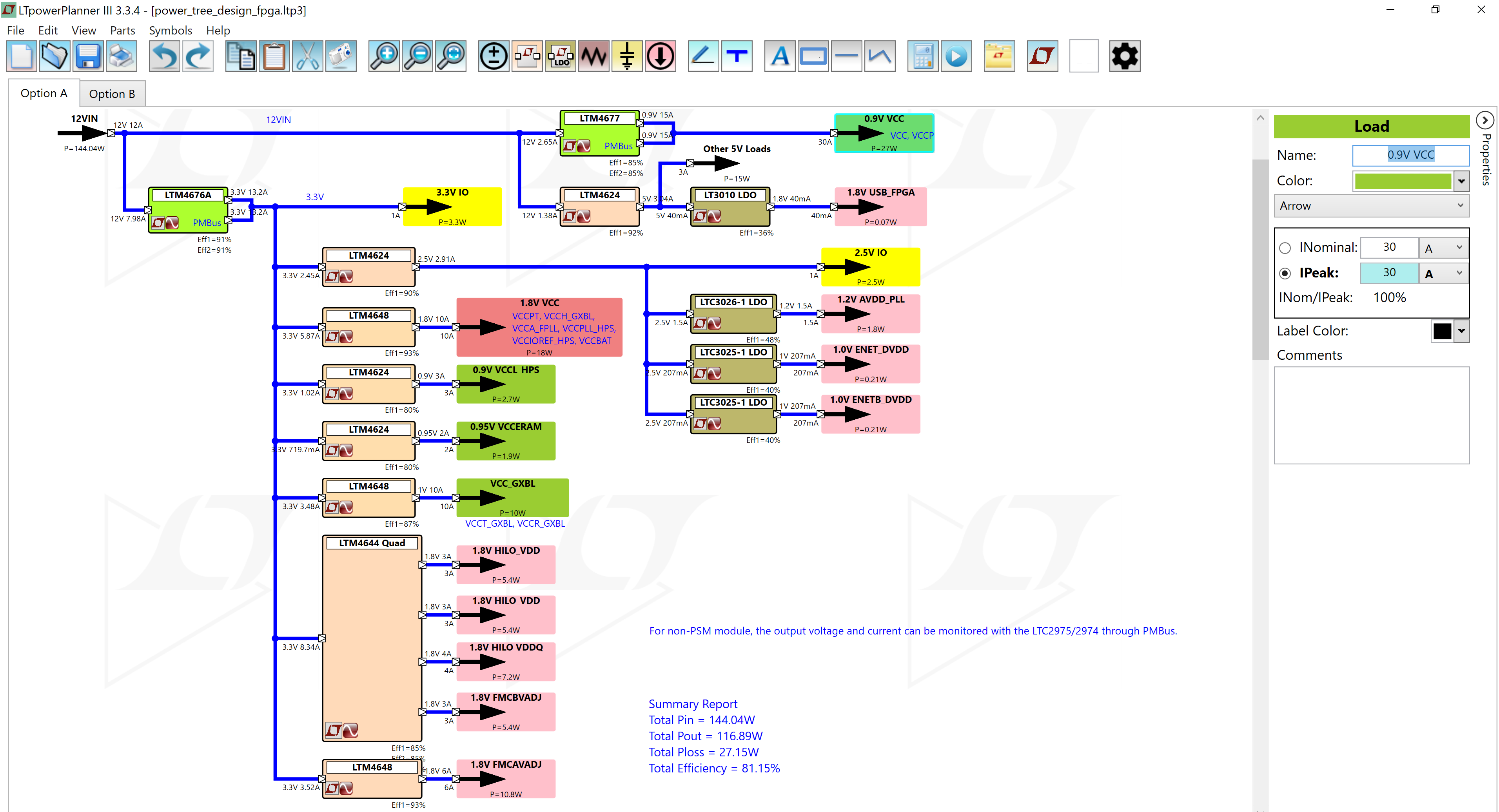

以上のことから、電源を設計する際には、レギュレータ製品を選定する前の段階で現実的な電力バジェットを立案することが重要です。まず、必要になるすべての電源レール(2.5V、3.3V、5Vなど)をピックアップしてください。また、それぞれの電源レールから電力を得るプルアップ抵抗、ディスクリート・デバイス、ICをすべて洗い出します。それらの値を基にして、図2(b)に示すように電源に対する要件を逆算します。LTpowerPlannerのようなパワー・ツリー用の設計ツールを使用すれば、策定した電力バジェットに対応するパワー・ツリーを容易に構成できます(図3)。

レイアウト、トラッキング、配線

トラックの幅、ビア、コンタクトのサイズが誤っていたり、ピン(コネクタ)の数が不足していたりすると、トラックのバーンアウトが生じます。その結果、電流制限の状態が発生するおそれがあります。このような状況は、レイアウト、トラッキング、配線を適切に行うことで回避できます。以下では、基板設計について覚えておくべき事柄やヒントを示します。

コネクタとピン・ヘッダ

トータルの出力電流が17Aになるように図2の回路を拡張するケースを考えます。その場合、(1本または複数本の)ピンにおけるコンタクトの電流容量(電流の処理能力)を考慮して設計を行う必要があります(図4)。一般に、ピンまたはコンタクトの電流容量は、物理的なピンのサイズ(コンタクトの面積)や金属の組成といった複数の要因に依存します。例えば、直径が1.1mmの標準的なスルーホールのオス型ヘッダ・ピン1の場合、電流容量は約3Aです。17Aの出力電流が必要であれば、相応の電流容量が得られるように、必ず十分な数のピンを用意してください。本数については、導電体(コンタクト)あたりの電流容量にピン数を乗じた値が、基板上に実装した回路の総消費電流にマージンを加えた値よりも大きくなるように決定します。上記の例の場合、17Aの出力電流に対応するには6本のピンが必要です(ヘッドルームは1A)。つまり、VCCとGNDで計12本のピンが必要になります。コンタクトの数を減らすには、パワー・ジャックまたはより大きなコンタクトの採用を検討してください。

トラック

レイアウトの電流容量を求める際には、オンラインで提供されているツールを利用すると便利です。1オンスの銅箔を採用したプリント基板の電流容量は、トラックの幅が1.27mmなら約3A、トラックの幅が3mmなら約5Aです。ヘッドルームを含めると、20Aのトラックには19mm~20mmの幅が必要になります(ここでは、温度上昇は考慮していないことに注意してください)。図4の例の場合、電源ユニットやシステムの回路におけるスペースの制約から、約20mmのトラック幅は確保できないと仮定します。この問題に対する1つの解決策は、プリント基板の複数の層を使用することです。例えば、トラック幅を3mmに設定し、それをプリント基板の全層に複製します。それにより、それらのトラック全体で20A以上の電流容量を満たすようにするといった具合です。

ビアとスティッチング

図5に示したのは、レギュレータを基板の電源プレーンに接続するビア・スティッチングの例です。電力の要件が2Aで、電流容量が1Aのビアを使用するのであれば、2Aの電流に対応可能なトラック幅とビア・スティッチングが必要です。図5の例では、電流を電源プレーンまでスティッチングするために少なくとも2個のビアを使用する必要があります(スペースが許すならば3個が望ましい)。これは見落とされがちな事柄の1つであり、スティッチングにビアが1個しか使用されていないケースが少なくありません。その場合、ビアはヒューズのように動作し、電流量が増えると隣接するプレーンへの電力が遮断されます。このようなビアに関する設計ミスについては、トラブルシューティングが困難になる可能性があります。ビアにダメージが加わっていることに気づかなかったり、コンポーネントの裏にビアが隠れていて見えにくかったりするケースがあるからです。

トラックの幅、ビアの穴のサイズ、そして両者の電気的なパラメータは、複数の要因を考慮して決定する必要があります。つまり、最終的な電流容量に影響を与える基板のめっきや、配線層、動作温度などに対する依存性を加味して決定しなければなりません。ここまでは、そうした依存関係については触れませんでした。しかし、実際には、それらの依存関係に注意してパラメータの値を決定する必要があります。トラック/ビアに関する計算に向けては、数多くのオンライン・ツールが提供されています。そうしたツールも活用し、細部に配慮して回路設計を行った後で、基板メーカーや基板レイアウトに精通した技術者からアドバイスを得ることを強くお勧めします。

過熱の回避

筐体や気流など、熱に関連する要素はいくつもありますが。ここでは露出パッドに着目することにします。「LTC3533」、「ADP5304」、「ADP2386」、「ADP5054」など、アナログ・デバイセズは露出パッド付きのレギュレータ製品を数多く提供しています。それらの製品をボードに正しく接続すれば、熱抵抗を下げることができます。通常、パワーMOSFETもダイ上に集積したモノリシック型のレギュレータICは放熱用の露出パッドを備えています。それに対し、外付けのパワーMOSFETを使用するコントローラICの場合、主な熱源(パワーMOSFET)が外部に存在することになります。そのため、通常は露出パッドは用意されていません。

通常、露出パッドは基板のグラウンド・プレーンにハンダ付けしなければ効果を発揮しません。但し例外も存在します。レギュレータ製品の中には、露出パッドをヒート・シンクとして機能させるために、基板上の絶縁されたハンダ領域に接続するという仕様のものがあります。各製品のデータシートを参照し、正しい使い方を確認してください。

露出パッドをグラウンド・プレーンや絶縁領域に接続する際には、必ずビア(その多くはアレイ状になっています)を使用して熱を効率的に伝導できるようにしてください。多層基板については、(全層において)露出パッドの下部のグラウンド・プレーンにビアを使って接続することをお勧めします。詳細については、稿末に示した参考資料2、3、4を参照してください。

露出パッドに関してここで説明した内容は、レギュレータICを対象としたものであることに注意してください。他の種類のICでは、露出パッドの取り扱い方が全く異なる可能性があります。露出パッドに関する詳細については、EngineerZone®5を参照してください。

まとめ

本稿で述べたように、電源を設計する際には、ノイズを十分に低く抑えつつ、トラックやビアのバーンアウトによってシステムの回路に影響が及ばないようにする必要があります。その作業には、コスト、効率、性能、実装面積に関する課題が伴います。本稿では、電源を設計する際、設計者が見落としがちな事柄に注目しました。例えば、パワー・ツリーを設計する際には、電力バジェットの分析に基づき下流のすべての負荷について考慮しなければならないといったことです。

回路図を作成したり、シミュレーションを実施したりするのは、設計作業の第1段階にすぎません。その後の工程では、適切な手法に即してコンポーネントの配置と配線を慎重に実施する必要があります。その際には、ビア、トラック、電流容量が要件を満たすことを確認しなければなりません。システムの回路は必ず正常に動作するとは限りません。インターフェース部にスイッチング・ノイズが生じていたり、ICの電源ピンまでノイズが伝わっていたりする場合には、問題の特定が難しくなる可能性があります。

参考資料

1 61302221121 header pin(ヘッダ・ピン)、Würth Elektronik

2 MT-093 Tutorial「Thermal Design Basics(熱設計の基本)」Analog Devices、2009年

3 Application Note 136「PCB Layout Considerations for Nonisolated Switching Power Supplies(非絶縁型スイッチング電源の基板レイアウトで考慮すべき事柄)」Linear Technology、2012年6月

4 Application Note 139「Power Supply Layout and EMI(電源レイアウトとEMI)」Linear Technology、2012年10月

5 「AD8045 Exposed Paddle Connection(AD8045の露出パドルの接続)」EngineerZone、2011年1月

LTM4700、Analog Devices、2018年10月

Power Management Tools(パワーマネジメント ツール)、Analog Devices