フェーズ・ロック・ループ(PLL)と電圧制御発振器(VCO)は、特定周波数のRF信号を生成したい場合によく使用されます。その際、 出力されるのは単一周波数の信号のみであり、それ以外の信号成分は 存在しないことが理想です。しかし、現実の出力には不要なスプリアス信号や位相ノイズが含まれます。なかでも、より大きな問題につながる可能性があるのが、スプリアス信号の1つである整数境界スプリアスです。本稿では、この整数境界スプリアスのシミュレーション方法と、それを除去する方法を紹介します。

PLLとVCOの組み合わせ(以下、PLL/VCO)には2つの種類があります。1つは インテジャーN型(整数分周型)と呼ばれるものです。この種のPLL/VCOは、位相周波数検出器(PFD)に入力される基準周波数の整数倍の周波数しか生成しません 。これに対し、より細かい周波数ステップに対応可能なPLL/VCOもあります。それが、フラクショナルN型(分数分周型)のPLL/VCOです。フラクショナルN型のPLL/VCOは柔軟性が高いため、より広範に使用されています。その動作は、基準レートにおけるPLLのフィードバック経路を調整することにより実現されます。フラクショナルN型のPLL/VCOでは、PFDに入力する基準周波数(以下、PFD周波数)よりもはるかに小さい周波数ステップを実現できます。ただし、その出力には整数境界スプリアス(IBS:Integer Boundary Spurs)と呼ばれる成分が混入します。このIBSは、PFD周波数fPFDの整数倍(1、2、3、……20、21、……)の位置に発生します。例えば、fPFDが100MHzであるとすると、100MHz、200M-Hz、300MHz、……2000MHz、2100MHz、……の位置にIBSが現れます。VCOの出力信号として2001MHzを得たいシステムでは、2000MHzの位置、つまりは所望の周波数から1MHzのオフセットを持った位置にIBSが現れることになります。PLLでは事実上のサンプリング処理が行われることになるので、所望の周波数を軸とする対称位置にも折り返し成分としてIBSが現れます。つまり、所望の出力周波数が2001MHzである場合、±1MHzのオフセット位置である2000MHzと2002MHzにIBSが生じるということです。)

IBSは次の2つの理由から望ましいものではありません。

- キャリア(所望の周波数)の低周波側に存在するIBSの電力は、積分位相ノイズの一因になる

- キャリアの高周波側にあるIBSにより、所望のチャンネルに近接するチャンネルに変調/復調が生じ、システムに歪みが発生する

システムによっては、高レベルのIBSによっていくつかの出力チャンネルが使用できない状態になることがあります。あるシステムが、一定の周波数帯域幅において1000個のチャンネルを備えているとします。そして、それらのチャンネルのうち10%に一定の電力レベル以上のIBSが生じているとしましょう。この場合、おそらくそれら100個のチャンネルは使用できなくなっているはずです。周波数帯域幅に対して多額のコストがかかるプロトコルを採用している場合、用意したチャンネルのうち10%も使用できないというのは大きな無駄です。

IBSは、所望の出力周波数からPLLの帯域幅の範囲内に整数境界が存在する場合に最も大きくなります。例えば出力周波数が2000.01MHzでループ帯域幅が50kHzであるといった場合にIBSが最も大きくなるということです。一方、IBSの電力は、出力周波数が整数境界から離れていくにつれ、計算によって算出でき、なおかつ再現性のある様態で減少していきます。アナログ・デバイセズ(ADI)は新たなシミュレータ「ADIsimFrequencyPlannerTM」を無償で提供しています。これを使えば、IBSの電力などの値を正確にシミュレーションすることができます。

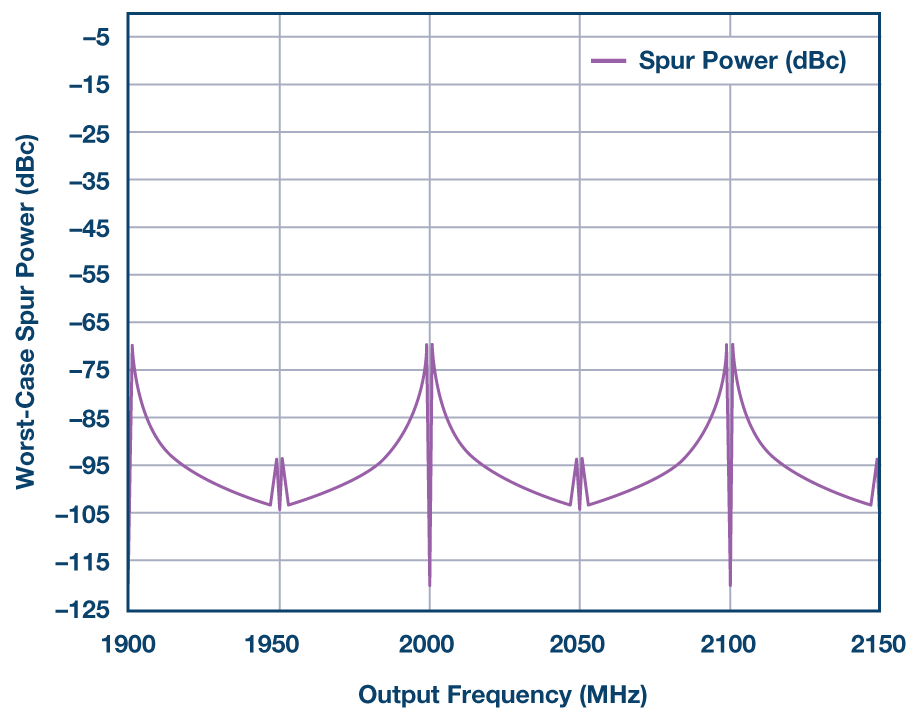

図1は、1900MHz~2150MHzの出力周波数(1MHzステップ)におけるワーストケースのIBS電力を示したものです。この図を見ると、2001MHzにおけるワーストケースのIBS電力が-70dBc(キャリアの電力より70dB小さい)であることがわかります。また、2000MHzでは出力周波数が整数境界になるためIBSは生じていません。IBS電力はキャリア周波数が整数境界から離れるにつれて減少します。その減少は次の整数境界に近づくまで続きます。

整数境界の中間(図1の2049MHzと2051MHz)に見えるスプリアス信号は、2次のIBSです。このように、2次のIBSは整数境界の中間に発生します。通常、2次のIBSは1次のIBSに比べて10dBから20dB低くなります。ADIsim-FrequencyPlannerでは、1次~5次のIBSのシミュレーションが行えます。

(「HMC830」の例、1MHzステップ、ループ帯域幅は100kHz)

「IBS電力が-80dBc以上になるチャンネルは使用できない」と規定されている変調方式を想定してみます。この場合、図1のチャンネルのうち約10%は使用することができません。この問題を解決するために、ADIsimFre-quencyPlannerを利用することができます。同ツールを使えば、IBSを低減する(ほとんどの場合は除去する)ようにPLL/VCOの構成(コンフィギュレーション)を最適化することが可能です。先述したように、IBSはPFD周波数の整数倍の位置で発生し、キャリア周波数の近くで最大になります。PFD周波数の整数倍がキャリア周波数から十分に大きいオフセット位置になるようPFD周波数を変えられるなら、IBS電力は問題のないレベルまで低減できるでしょう。このようなアルゴリズムがADIsimFrequen-cyPlannerで実行されます。その際には、1次~5次のIBSの相対電力も考慮されます。その結果として、ADIsim-FrequencyPlannerはVCOの出力でIBSを最小化できる最適な解を導き出します。

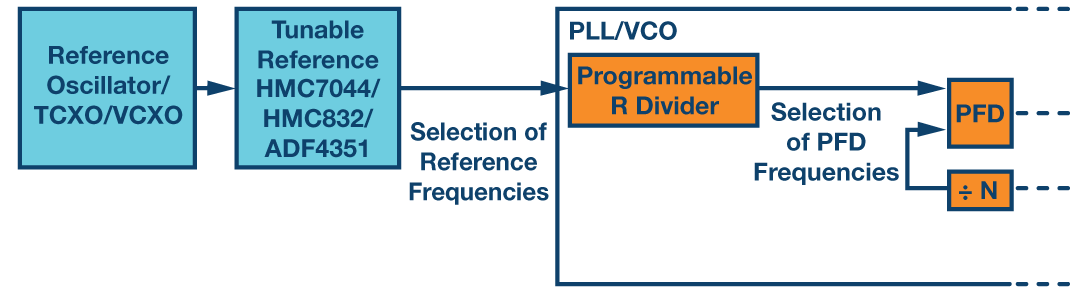

では、PFD周波数はどうすれば変更できるでしょうか。従来の一般的なPLL/VCOでは、PFD周波数は固定されていました。しかし、現在では、プログラマブルなクロック分配器や、PLLの基準入力部に使用する分周器、フラクショナルN型の変調アーキテクチャを最大限に活用することで、各出力チャンネルに対するPFD周波数を比較的容易に変更できるようになりました(図2)。

利用をお勧めしたいのは、クロック生成/分配用の新製品 「HMC7044」を利用したソリューションです。HMC7044は、超低ノイズの出力を14系統備えています。各出力には個々にプログラマブルな分周器が用意されています。これらの出力の1つをPLLの基準入力に接続し、必要に応じて出力分周器をプログラムすることにより、PLLでは数多くの基準周波数を使用できるようになります。

HMC7044は、A/Dコンバータ(ADC)やD/Aコンバータ(DAC)などのシステム・コンポーネントに対して数多くの同期クロックを供給する必要がある用途に適したクロック分配システムです。なお、それほど多くの種類のクロック は必要ない単純なアプリケーションでは、PLLとVCOを集積した「HMC832」や「ADF4351」といったシンプルな製品を使用するとよいでしょう。

このソリューションでは、PLLの基準入力部に分周器(R分周器)を配置します。この分周器は、より多くの PFD周波数(R分周器の出力周波数)を用意するために、使用可能な基準周波数を必要に応じて分周するようプログラムすることができます。各PLLは高次のフラクショナルN型変調器を備えているので、PFD周波数を変更することによって、出力周波数を生成する際に 問題が起きることはありません。また、PLLが備えるプログラマブルなチャージ・ポンプ(電流値をプログラムできる)により、PFD周波数の変更に対する補償を行います。その結果、ループ帯域幅を一定に維持することが可能になります。

例:

| fPFD (MHz) |

N | ICP | fPFD × N = RFOUT (MHz) |

Comments |

| 100 | 20.01 | 2.08 | 2001 | ±1MHzでのIBS |

| 75 | 26.68 | 1.88 | 2001 |

±24MHzでのIBS |

ICP = プログラマブルなチャージ・ポンプ電流

fPFD = PLLのPFD周波数

N = PLLのフラクショナルNの値

RFOUT = VCOの出力周波数(キャリア周波数、所望の周波数)

プログラマブルなチャージ・ポンプ電流は、PFD周波数とは逆向きに変化させます。つまり、PFD周波数を高くする場合、チャージ・ポンプ電流は減少させなければなりません。このような働きにより、ループ・フィルタ・ダイナミックは一定に維持されます。

ADIsimFrequencyPlannerを使用する際には、所望の出力周波数範囲、ステップ幅、PFD周波数と基準周波数に対する制約条件、ループ・フィルタのパラメータ値を入力します。また、利用可能なクロック・ジェネレータ、出力分周器、PLLの基準入力用分周器を選定します。すると、ADIsimFrequencyPlannerは所望の周波数を1ステップずつ変更しながら、使用可能な数多くのPFD周波数の中から最適なPFD周波数を計算によって割り出します。次に、ADIsimFrequencyPlannerは分周器の設定条件とチャージ・ポンプの電流の情報をユーザーに返します。これらのデータは、ルックアップ・テーブルに容易にエクスポートできます。最終的なアプリケーションのファームウエアによってこれらのデータを読み出し、その結果に応じてHMC7044とPLL/VCOをプログラムすることができます。さらに、ADIsimFrequencyPlannerは、発生している事象に関する一連のグラフを生成し、ユーザーに提示します。

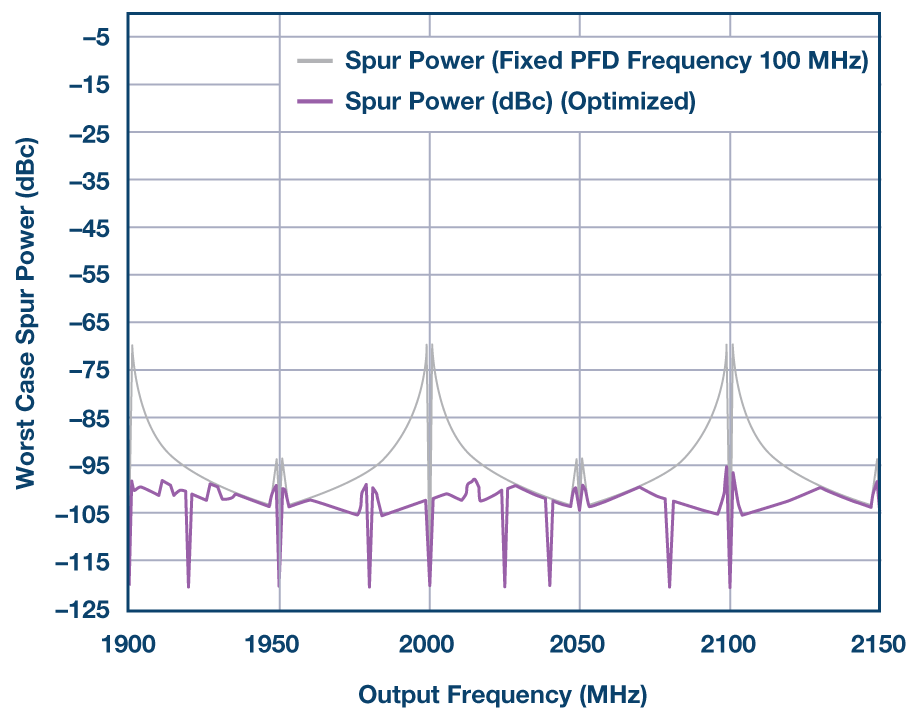

図3は、図1と同じ出力構成で同等のシミュレーションを行った結果です。紫色のプロットのとおり、HMC7044の出力分周器とPLLの基準入力用分周器に変更を加えることで、PFD周波数が最適化されています。比較を行うために、最適化されていない状態のシミュレーション結果を灰色のプロットで示しています。

図3を見ると、全出力範囲(1900MHz ~ 2150MHz、1MHzステップ)におけるIBSは-95dBc以下に保たれています。つまり、所望の出力のほとんどで優れた周波数品質が得られるということです。このように、最適化を行ったことによって飛躍的な改善が図れました。

広帯域のVCOにADIsimFrequencyPlannerを適用

ADIsimFrequencyPlannerの精度の高さと有用性を評価するために、ADIが提供する高性能の製品をいくつか使用して、実機による評価/実験を行いました。実験に使用した製品の概要を以下に示します。

-

HMC7044(クロック生成/分配)

- 出力周波数は最高3.2GHz

- JESD204Bに準拠

- 超低ノイズ(ジッタは12kHz~20MHzの範囲で50fs未満)

- 983.04MHzの出力から800kHzのオフセット位置で-142dBc/Hz

- プログラマブルな16系統の出力

-

ADF5355(PLL/VCOを集積)

- 出力周波数は55MHz~13.6GHz

- パッケージは5㎜×5㎜のLFCSP

- 3.4GHzの出力から1MHzのオフセット位置で-138dBc/Hz

-

HMC704(超低ノイズのPLL)

- RF入力周波数は最高8GHz

- PFD周波数は最高100MHz

- 正規化した位相ノイズフロアは-233dBc/Hz

ADF5355はPLLを内蔵していますが、この実験では、ADF5355のVCOを外部からロックするためにHMC704を使用しました。この手法により、以下に示す2つのメリットが得られます。

- ADF5355が備えるVCOの位相ノイズ性能とHMC704が備えるPLLの位相ノイズ性能はいずれも業界最高レベルにある。両性能を活かすことによって、優れた全位相ノイズ性能が得られる

- VCOとPLLが分離されることにより、信号の好ましくないカップリングが削減され、IBS電力を抑えられる

この実験に向けて、250kHzのステップ(ステップ数は6000)で4800MHz~6300MHzの範囲で出力を最適化するためにADIsimFrequencyPlannerを使用しました。その結果を踏まえ、HMC7044、ADF5355、HMC704のそれぞれに対し、各ステップにおいて最適な分周条件(最適なPFD周波数)とチャージ・ポンプ電流の条件をプログラムしました。各ICを1つの出力ステップにプログラムしたら、スペクトル・アナライザによってキャリアの電力と1次/2次のIBS電力を測定します。スペクトル・アナライザの周波数スパンと分解能帯域幅は非常に狭く設定しました。それでも、ほとんどのチャンネルにおいて、IBS電力は測定器のノイズフロアよりも低く、ノイズしか測定されませんでした。

次に、PFD周波数を60MHz~100MHzに制限して測定を行いました。ループ帯域幅と位相マージンはそれぞれ17kHzと49.6°です。

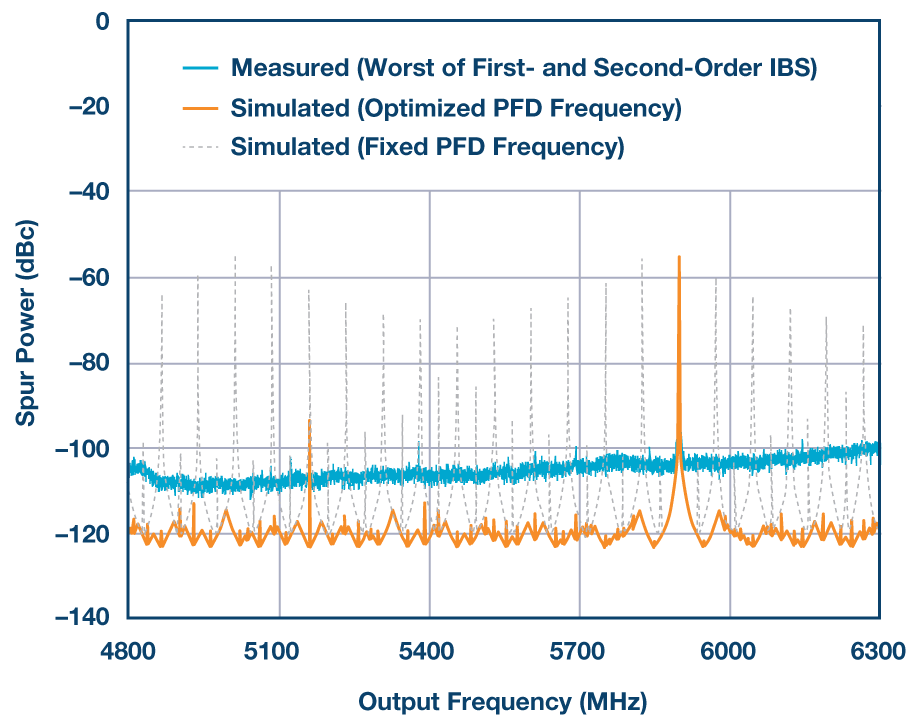

図4に、HMC7044、ADF5355、HMC704を使用した測定結果とシミュレーション結果を示しました。この測定/シミュレーションについてまとめると以下のようになります。

- 6000個の出力チャンネルに対するシミュレーションと測定を実施できた

- IBSのシミュレーション結果のほとんどは約-120dBcとなった。この値はスペクトル・アナライザのノイズフロアよりも小さいので、実験ではノイズだけが測定された

- 一般的なIBSの要件は-70dBc~-80dBcだが、ほとんどの周波数でIBSを-100dBc以下に抑えることができた

- HMC7044のマスター・クロック周波数の2倍の位置に、最適化を図ってもIBSが改善されない領域がある。その領域の幅は2MHzよりも狭い。この領域では、分周器をどのように組み合わせてもIBS性能を改善できない

(最適化が行えない周波数範囲については、ADIsimFrequencyPlannerによって正確にシミュレーションを行っている。それ以外のほとんどの周波数では、スペクトル・アナライザのノイズフロア以下の測定値となった)

上述したように、PFD周波数を最適化してもIBS性能が改善されない非常に狭い周波数範囲が1つだけあります。その周波数範囲は、システムのマスター・クロックの2倍の位置にあります。ここで取り上げている例であれば、2949.12MHz×2=5898.24MHzの位置です。この位置の周波数を使う場合、可能であれば、キャリア周波数をすぐ近くのよりクリーンな周波数にシフトするとよいでしょう。そのうえで、補償を行うために、デジタル領域のベースバンド周波数をシフトすることを推奨します(NCO:数値制御発振器)。例えば、キャリア周波数を2MHzだけシフトし、デジタル領域のベースバンド周波数を補償のために2MHzだけシフトするといった具合です。あるいは、システムとして可能であれば、マスター・クロック周波数を変更してクリーンな出力周波数を生成するという方法も考えられます。

なお、先述したように、HMC7044ではなく、HMC832やADF4351を使用するよりシンプルなソリューションであれば問題になる周波数はありません。

図4から、ADIsimFrequencyPlannerによって、以下のようなことが可能になることがわかります。

- IBSの正確なシミュレーションが行える

- 基準周波数の生成元とPLL/VCOシステムを最適化し、良好なIBS性能を実現することができる

- IBSに関する最適化を行うことにより、特定の周波数範囲内でより多くのチャンネルを使用することが可能になる。その結果、周波数帯の価値が多額なコストに見合うレベルまで高まる

- 広範な周波数に対応するシステムのシミュレーションを非常に迅速に実施できる。これと同等のプロセスを手作業で行うと、数日ないしは数週間もの時間を要することがある。ADIsimFrequencyPlannerであれば、6000以上のステップのシミュレーションを1分以内に完了できる