ADAU1850

新規設計に推奨3 ADC、1 DACの低消費電力コーデック、オーディオ/FastDSP付き

- 製品モデル

- 1

- 1Ku当たりの価格

- 最低価格:$6.42

製品の詳細

- プログラマブルなFastDSPオーディオ処理エンジン

- 最大768kHzのサンプル・レート

- バイクワッド・フィルタ、リミッタ、ボリューム制御、ミキシング

- 低遅延の24ビットADCおよびDAC

- 106dBのS/N比(ADCを通した信号にA加重フィルタを適用した場合)

- 110dBの合計S/N比(DACおよびヘッドフォンを通した信号にA加重フィルタを適用した場合)

- シリアル・ポートのサンプル・レート:8kHz~768kHz

- アナログtoアナログの群遅延:5μs

- 13段イコライザ用のプログラマブルな倍精度MACエンジン

- 3つのアナログ入力(2差動および1シングルエンド)、マイクロフォン入力またはライン入力として設定可能

- アナログ差動オーディオ出力:ライン出力またはヘッドフォン・ドライバとして設定可能

- PLLは30kHz~27MHzの任意の入力クロック・レートに対応

- 1チャンネルASRCI、3チャンネルASRCO

- シリアル・オーディオ・ポートはI2S、左詰め、最大16チャンネルのTDM(TDM16)に対応

- 柔軟なルーティングが可能な2つのインターポレータと4つのデシメータ

- 電源

- アナログAVDD:1.8V

- デジタルI/O IOVDD:1.8~3.3V

- ヘッドフォンHPVDD:1.8V

- ヘッドフォンHPVDD_L:1.2~1.8V

- 制御/通信インターフェース

- I2C、SPI、またはUART

- 28ボール、0.4mmピッチ、2.957mm × 1.757mm WLCSP

ADAU1850は、1つのデジタル・シグナル・プロセッサを搭載する3入力、1出力のコーデックです。アナログ入力からDSPコアを経由してアナログ出力に至る経路は、低遅延になるように最適化されており、ノイズ・キャンセリング・イヤフォンに最適です。少数の受動部品を追加することにより、ADAU1850はフル機能のヘッドセット・ソリューションを提供できます。

ADAU1850は、小型の28ボール、2.957mm × 1.757mmのウェーハ・レベル・チップ・スケール・パッケージ(WLCSP)を採用しています。

アプリケーション

- ノイズ・キャンセリング機能搭載のハンドセット、ヘッドセット、ヘッドフォン

- Bluetoothアクティブ・ノイズ・キャンセリング(ANC)機能搭載のハンドセット、ヘッドセット、ヘッドフォン

- 個人向けナビゲーション機器

- デジタル・カメラおよびビデオ・カメラ

- 楽器用のエフェクト・プロセッサ

- マルチメディア・スピーカ・システム

- スマートフォン

ドキュメント

データシート 2

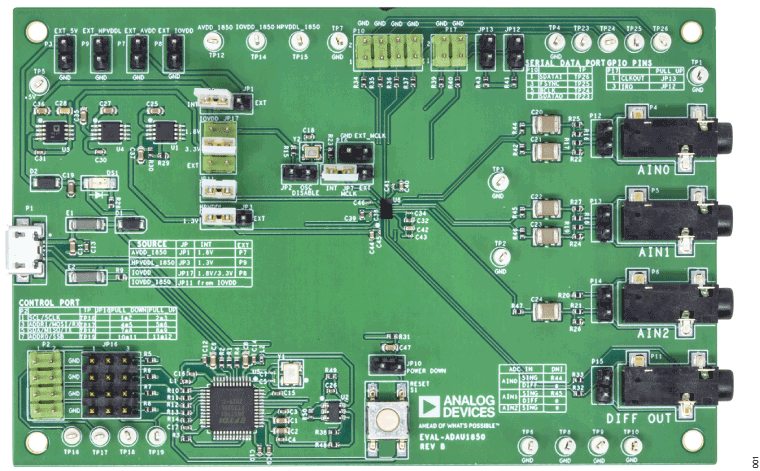

ユーザ・ガイド 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| ADAU1850BCBZRL | 28-ball WLCSP (2.957mm x 1.757mm x 0.5mm) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

2 7, 2022 - 21_0236 ADAU1850 Addition of an Alternate Test Site + Die and Data Sheet Revision |

||

| ADAU1850BCBZRL | 製造中 | |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

Lark Studio

Lark Studio is a standalone Windows Graphical User Interface (GUI) tool for programing and tuning software on the Lark/Lark-Lite/SSM6515. Lark Studio includes intuitively reading/writing control registers, and providing a drag and drop interface for user to design FastDSP schematic, which can be downloaded to the target directly. It also supports safe loading, generating C source files, calculating tables of filter coefficients and visualizing filter magnitude & phase response. It also supports EQ configuration, along with calculating tables of filter coefficients and visualizing filter magnitude & phase response, generating C source files, and download to the target.

Lark SDK Setup

Lark SDK is embedded firmware package, including driver for all hardware modules of ADAU1860 and ADAU1850. It is delivered in source code format and also featured by log support, friendly high level APIs, etc.

評価用ソフトウェア 0

必要なソフトウェア/ドライバが見つかりませんか?