目的

論理ゲートICが初めて登場したのは1960年代のことです。それ以降、論理回路(デジタル回路)では様々な種類の技術が使われてきました。そうした初期の技術の例として、今回はTTL(Transistor-transistor Logic)を取り上げます。その具体的な例として、TTLのインバータ(NOTゲート)と2入力のNANDゲートについて検討します。

背景

図1に、TTLインバータの回路図を示しました。この回路では、1個のトランジスタで構成したインバータ回路の制約が克服されています。基本的なTTLインバータは、電流制御入力段、位相分割段、出力ドライバ段の3つの段で構成されます。

入力段のトランジスタQ1は、電流制御の機能を担います。この入力段は、バック・ツー・バック・ダイオードを利用した回路と同じようなものだと考えることができます(図2)。この回路では、Q1を順方向モードまたは逆方向モードで動作させます。それにより、2段目の位相分割段を構成するトランジスタQ2のベース電流を制御します。順方向の電流ゲインβFは、逆方向の電流ゲインβRよりもはるかに大きな値になります。そのため、オフになるときにはベースを放電するためにより多くの放電電流が流れます。

2段目のQ2は、位相分割機能(フェーズ・スプリッタ)を使って出力段を駆動します。すなわち、入力の条件に応じて逆位相を生成し、プルアップ側とプルダウン側の出力トランジスタを駆動します。つまり、トランジスタQ3がオンのときにはトランジスタQ4をオフにし、Q3がオフのときにはQ4をオンにします(図3)。

2つの出力トランジスタQ3とQ4は、ダイオードD1と共に、トーテムポール出力と呼ばれる構造を形成します(図4)。この構造により、電流の能動的なソースとシンクを実現できます。そのため、容量性の負荷も適切に駆動することが可能です。抵抗R4は、VCCから供給される電流を制限する役割を果たします。定常状態では、一度に1つのトランジスタだけがオンになります。

D1は、Q4の実質的なターン・オン電圧を高める役割を担います。それにより、Q3が完全にオンになる前にQ4をオフにすることができます。この構造は、論理の状態が遷移する際、出力段に大きなサージ電流が流れ込むことを防ぐ効果をもたらします。R4も、出力段に流れる可能性がある電流を制限する効果をもたらします。この回路の欠点は、ダイオードの電圧降下の分だけ論理レベルのハイに相当する電圧が低下することです(これについては、後ほど示す図11を参照してください)。

準備するもの

- アクティブ・ラーニング・モジュール「ADALM2000」

- ソルダーレス・ブレッドボード

- ジャンパ線

- 抵抗:100kΩ(1 個)、2.2kΩ(1 個)、470Ω(1 個)、100Ω(1 個)

- 小信号ダイオード:「1N914」(1 個)

- 小信号 NPN トランジスタ:「2N3904」(5 個。出力段では「SSM2212」も使用可)

TTLインバータ

まずはTTLインバータの回路を実際に構成し、その動作を確認してみましょう。

説明

アナログ・パーツ・キットの「ADALP2000」には、NPNトラジスタとして2N3904が5個含まれています。古いキットには、マッチングのとれたトランジスタ・ペアであるSSM2212が1個含まれているかもしれません。以下に示すブレッドボードの実装例は、SSM2212を使用することを前提としています。2N3904だけを使用する場合には、必要に応じて配置/配線を変更してください。

ここでは、図5に示すようにTTLインバータの回路を構成します。これをソルダーレス・ブレッドボード上に実装してください。SSM2212は、出力段のQ3とQ4としてしか使用できません。SSM2212は、ベース端子とエミッタ端子の間に逆バイアスがかかることを防ぐための保護用ダイオードを内蔵しているからです。

ハードウェアの設定

図5に示したとおりに、ADALM2000の入力/出力コネクタに回路を接続してください。オシロスコープの未使用の負入力(1-、2-)は、グラウンドに接続するのが最善です。図6に、図5の回路を実装したブレッドボードを示しました。

手順

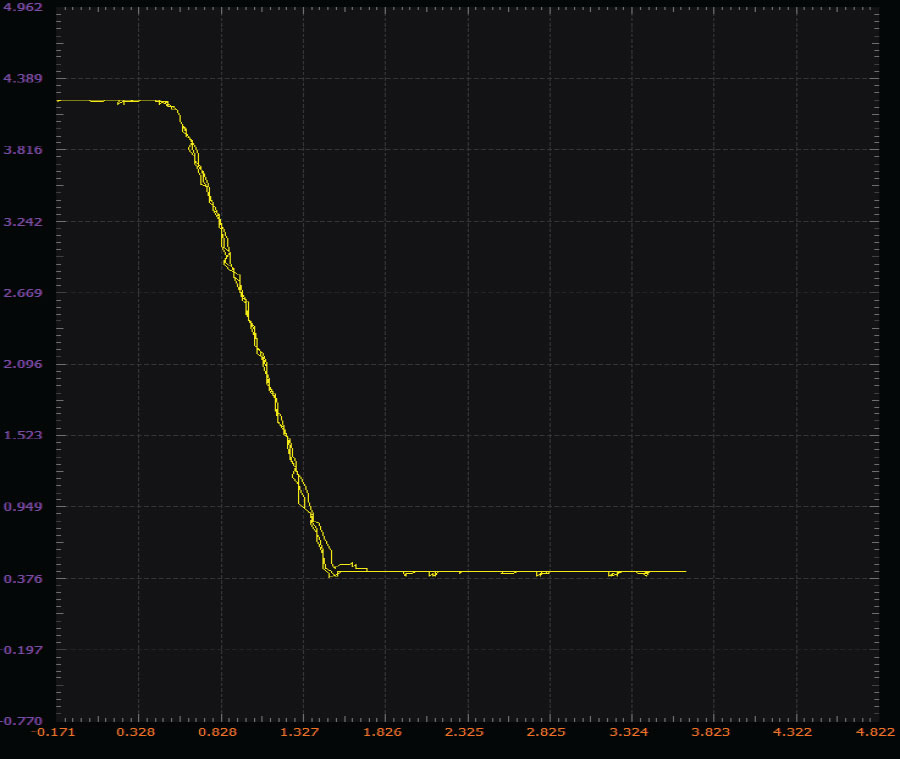

任意波形ジェネレータ(AWG)の出力(W1)は、ピークtoピークの振幅が6V、オフセットが0V、周波数が100Hzの三角波を生成するように設定します。オシロスコープのXYモードを使用し、回路の伝達特性(入出力電圧の関係)を観測してください(図7)。

TTLのNANDゲート

続いて、TTLのNANDゲートを構成し、その動作を確認します。

説明

TTLインバータにもう1つ入力を追加すれば、NANDゲートを実現することができます。具体的には、図8のような回路を構成します。

ハードウェアの設定

図8に示すとおりに、回路をADALM2000の入出力コネクタに接続します。オシロスコープの未使用の負入力(1-、2-)はグラウンドに接続してください。

図9に、図8の回路を実装したブレッドボードを示しました。

手順

AWGのW1は、ピークtoピークの振幅が6V、オフセットが0V、周波数が100Hzの三角波を生成するように設定します。一方、W2は、位相が90°、ピークtoピークの振幅が6V、オフセットが0V、周波数が100Hzの三角波を生成するように設定してください。

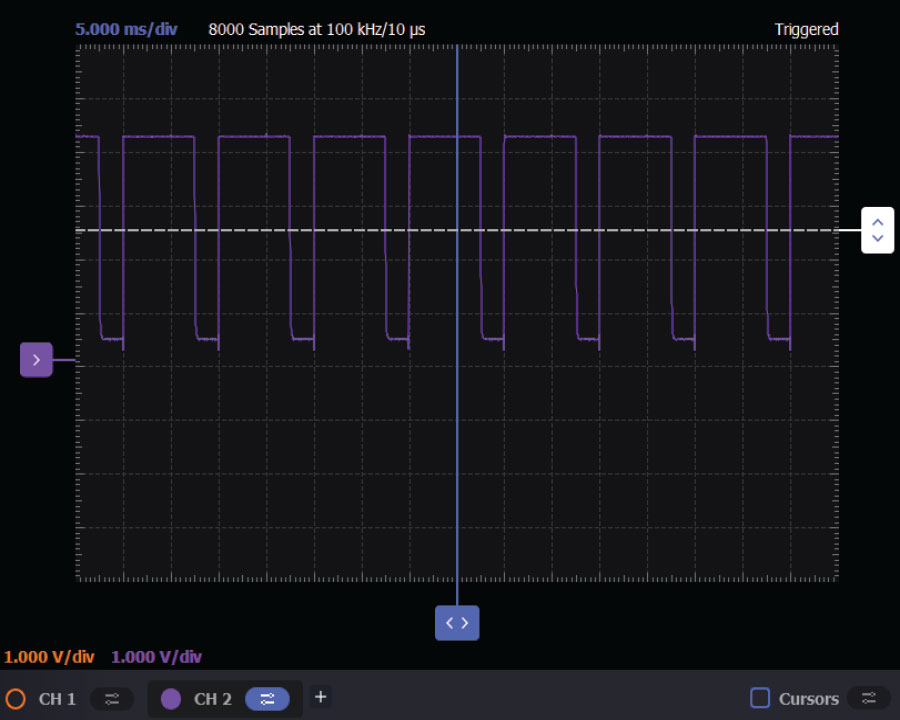

オシロスコープを使用して、回路の出力(チャンネル2)を観測します。適切に回路を構成していれば、図10に示すような結果が得られるはずです。

伝達特性についての検討

TTLインバータの伝達特性は、どのようにすれば分析できるでしょうか。その答えは、入力電圧を緩やかに増加させた場合に起きる事象のシーケンスを、各トランジスタの導通状態の変化とその変化が始まる臨界点に注目して観測するというものになります。図11に、TTLインバータの入力と出力の関係を示しました。以下、この図を基に、回路の伝達特性について考察してみましょう。

ブレーク・ポイントP1

入力電圧はほぼ0Vの状態で、Q1にベース電流が供給されています。そのため、Q1は順方向モードで導通します。コレクタの電流源はQ2のリーク電流だけですが、Q1は飽和するまで駆動されます。それによってQ2は確実にオフになります。結果として、Q3もオフの状態になります。負荷は存在しませんが、リーク電流が出力段に流れ込みます。Q4とD1はオンの状態になりますが、電流はほとんど流れません。

VOUT = VCC – VBE4 – VD1

VOUT = 5 V – 0.6 V – 0.6 V = 3.8 V

[ポイント P1]:VIN = 0.5 V, VOUT = 3.8 V

ブレーク・ポイントP2

入力電圧が少し上昇したとしても、上記と同様に、Q1は飽和状態でオンになっているという状態がしばらく続きます。その後、Q2のベース電圧が上昇し、導通点に達します。この段階では、次のような状態になります。

VIN = VBE2 – VCE1(SAT) = 0.6 V – 0.1 V = 0.5 V

[ポイント P2]:VIN = 0.5 V, VOUT = 3.8 V

ブレーク・ポイントP3

入力電圧が更に上昇すると、Q2の導通状態は更に進み、完全にオンになります。Q2のベース電流は、Q1のベース‐コレクタ接合部から供給されます。Q1は、この時点でまだ飽和状態にあり、ベース‐コレクタ間には順方向のバイアスがかかっています。しばらくすると、Q3が導通点に達します。そのときには、以下のような状態になっています。

VIN = VBE2 + VBE3 – VCE1(SAT)

VIN = 0.7 V + 0.6 V – 0.1 V = 1.2 V

Q3がまさにオンになるとき、VBE3は0.6Vであることに注意してください。つまり、R3を流れる電流は、0.6V/470Ω = 1.27mAとなります。線形アクティブ領域で動作しているため、Q2のコレクタ電流は0.97mA×1.27mA = 1.23mAとなります

R2における電圧降下は、VR2 = 1.23mA×2.2kΩ = 2.7Vです。

この条件下で、Q2のコレクタ‐エミッタ間の電圧降下は以下のようになります。

VCE2 = VCC – VR2 – VR3

VCE2 = 5 V – 2.7 V – 0.6 V = 1.7 V

したがって、Q2はまだ順方向のアクティブ・モードで動作していることになります。

Q3が導通し始めると、Q4とD1にも電流が流れるようになります。やがて、D1は完全にオンになります。このときの状態は以下のようになります。

VO = VCC – VR1 – VBE4 – VD1

VO = 5 V – 0.94 V – 0.65 V – 0.6 V = 2.81 V

[ポイント 3]:VI = 1.2 V, VO = 2.81 V

ブレーク・ポイントP4

入力電圧が更に上昇すると、Q2の導通状態は更に進み、最終的には飽和モードに移行します。Q3の導通も更に進み、最終的には飽和点に達します。Q2の導通が進むにつれ、そのコレクタ電流が増加します。それによりR1における電圧降下が大きくなり、Q2のコレクタ‐エミッタ間電圧であるVCE2が低下します。この電圧がQ4とD1の導通条件を下回ることになることから、Q3が飽和する前にQ4とD1の両方がオフになります。

Q3がまさに飽和に達するときには、次のような状態になります。

VI = VBE2 + VBE3 – VCE1

VI = 0.7 V + 0.7 V – 0.1 V = 1.3 V

[ポイント 4]:VI = 1.4 V, VO = 0.2 V

問題

一般に、標準的なTTLの出力回路はトーテムポール出力と呼ばれています。2つの出力トランジスタを上下に積み重ねている状態が、トーテムポールに似ているからです。では、トーテムポール出力を備える論理ゲートは、負荷電流のソース、シンクのうちどちらに対応できるのでしょう? あるいはどちらにも対応可能なのでしょうか?

答えはStudentZoneで確認できます。