AN-1464:AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2、AD7124-4和AD7124-8校准

简介

ADI公司的精密Σ-Δ型产品具备片内校准功能,支持内部校准和系统校准。这些Σ-Δ型产品集成了系统中所需的许多附加构建模块,例如增益和内部基准。内部校准可最大限度降低内部失调误差和增益误差。这些器件上使用的校准方法可校准所有内部模块的失调误差和增益误差,例如校准增益级的误差。

转换器支持系统失调误差和增益误差校准,外部组件通过模数转换器(ADC)配合内部误差源提供校准。

本应用笔记将详细讨论 AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2、AD7124-4 和 AD7124-8中使用的校准方法。

失调误差和增益误差

本应用笔记中讨论的ADC均支持单极性和双极性两种工作模式。而本部分讨论单极性模式的失调误差和增益误差。

失调误差是指当ADC代码为000时与理想值之间的电压偏差。图1显示了ADC传递函数。

图1. ADC传递函数

ADC的增益误差是指在最大输入电压时,实际值与理想值之间的误差;即最大和最小输入电压时的误差,如图2所示。

图2. ADC增益误差

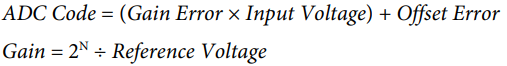

图2中的ADC传递函数可等效换算成Y = MX + B形式的直线方程,相当于

可以对整个信号链的失调误差和增益误差进行微调,从而提高整体系统精度。失调误差可通过执行失调校准或零电平校准来调整,而增益误差可通过执行增益校准或满量程校准来调整。

一般来说,模数转换后的结果会显示转换误差。而执行校准可确保这些误差得到调整。可以使用微控制器单元(MCU)上的预定义软件来实现校准,校准系数存储在MCU存储器中。这些校准系数可对整体ADC转换结果进行调整,从而消除增益误差和失调误差。使用这种技术时需要花费更多的时间,因为ADC转换结果需要由MCU进行后处理以确保数值的正确性。

ADI公司的精密Σ-Δ型ADC产品系列内置多种校准模式,可用于调整ADC转换结果中的增益误差和失调误差。该系列Σ-Δ型ADC配有片内寄存器来存储校准系数。

ADC转换过程的一部分,这些系数将自动校正ADC转换结果中的增益误差和失调误差。转换结果先减去失调校准系数,然后乘以增益误差系数。

校准模式

AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2 Σ-Δ型ADC均采用类似的方法执行校准。

AD7124-4和AD7124-8属于低功耗Σ-Δ型ADC产品系列,具有全集成式模拟前端,适用于高精度测量应用。AD7124-4和AD7124-8支持以下四种校准模式:

- 内部零电平校准

- 内部满量程校准

- 系统零电平校准

- 系统满量程校准

AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2属于兼具低噪声和快速建立特性的多路复用Σ-Δ型ADC产品系列,支持以下三种校准模式:

- 内部零电平校准

- 系统零电平校准

- 系统满量程校准

这些校准模式可使用软件编程,并通过ADC_CONTROL寄存器(AD7124-4和AD7124-8)和ADC模式寄存器(AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2)进行访问。

失调(零电平)和增益(满量程)校准是模拟输入已知的转换过程。在所有情况下,RDY 会在校准启动时变为高电平,并在校准完成后返回低电平。

内部零电平失调校准

对于内部零电平失调校准,所选正输入引脚会自动断开与外部的连接,并从内部连接到所选的负模拟输入引脚。因此,需确保所选负引脚上的电压不超过允许的限值,并且没有过大的噪声和干扰。图3显示了正模拟输入(AINP)和负模拟输入(AINM)的内部连接框图。

图3. 内部零电平失调校准

系统零电平失调校准

对于系统零电平失调校准,必须对ADC输入引脚施加校准电压。执行此类校准后,可同时降低信号链中的外部电路失调以及ADC失调。例如使用输入模块时,用户可在连接器端子处将各输入短接,以便通过校准消除由于信号调理以及ADC失调而引起的任何误差。图4显示了 EVAL-AD7124-4SDZ 评估板的设置(AIN0与AIN1短接)。EVAL-AD7124-4SDZ由 ADP1720 供电,并使用 ADR4525 作为基准,使用 EVAL-SDP-CB1Z 作为评估控制器板(基于ADSP-BF527处理器)。

图4. EVAL-AD7124-4SDZ评估板系统零电平校准设置

使用的是EVAL-AD7124-4SDZ评估板和AD7124-4/AD7124-8 Eval+软件。AD7124-4的配置如下:

- 通道:AIN0和AIN1

- 使用评估板上的LK5将引脚AIN0和引脚AIN1短接

- 使能VBIAS

- 增益 = 2

- 功率模式:全功率模式

- 输出数据速率:50 SPS

图5显示了对AD7124-4执行校准前后的性能对比结果(AIN0与AIN1短接在一起)。执行外部失调校准后,失调误差减小了,转换结果为零伏左右。而执行外部失调校准前,ADC的转换结果存在0x7FFF60(即24 μV)的失调误差。更多信息参见AD7124-4数据手册。

图5. 执行系统零电平校准前后的对比

在低功耗模式下执行系统零电平校准后,失调寄存器更新为0x7FFF89。而ADC刚执行完转换时的结果为0x7FFFFC(平均值约为120 nV),噪声水平大约为330 nV RMS。

内部满量程增益校准

内部满量程增益校准可确保将接近满量程的输入电压自动连接到所选的模拟输入。

AD7124-4和AD7124-8包括一个电阻网络,可使ADC产生幅值为"VREF ÷ 增益"的信号,从而保证器件在全部增益条件下支持内部满量程校准。

请注意,不能在全功率模式下对AD7124-4和AD7124-8执行内部满量程(增益)校准,必须采用低功耗模式或中功耗模式。不过,若是在低功耗模式或中功耗模式下执行内部满量程增益校准并在转换期间切换回全功率模式,则是可以接受的。只要使用的基准和增益相同,校准系数就依然适用。

系统满量程增益校准

执行系统级满量程增益校准时,需要将满量程电压施加到输入。此类校准可同时降低ADC外部的任何增益误差。以输入模块为例,在校准期间,可以将满量程信号施加到模块输入而非ADC输入,从而校准整个模块的增益误差。图6显示了AD7124-4系统满量程校准的框图(使用EVAL-AD7124-4SDZ评估板)。要执行系统满量程校准,需将AIN1连接到AVSS并在AIN0上输入满量程电压(增益 = 2时为1.25 V)。

图6. EVAL-AD7124-4SDZ系统满量程校准设置

图7显示了AD7124-4和AD7124-8系统增益校准的效果。该校准再次使用了EVAL-AD7124-4SDZ评估板和软件,AD7124-4的配置如下:

- 通道:AIN0和AIN1

- 双极性模式

- 增益 = 2

- 功率模式:全功率模式

- 输出数据速率:50 SPS

在AIN1连接到AVSS的条件下,通过连接器J6向AIN0施加1.25 V电压。执行校准之前,生成的ADC输出代码为0xFF13C (16,744,765)。

图7. 使用EVAL-AD7124-4SDZ执行系统满量程校准前后的对比

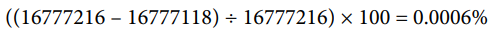

执行系统满量程校准之后,增益寄存器的内容更新为0x55A2D3。在使用同一输入电压的前提下,ADC结果平均值变为0xFFFF9D (16,777,118)。因此,最终的增益误差降至:

工厂校准

失调寄存器的默认值是0x800000,增益寄存器的标称值是0x5XXXXX。增益误差在增益为1时经过出厂校准。因此,AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2包含默认的增益系数,具体因器件而异。AD7124-4和AD7124-8在增益为1时不支持内部满量程校准。

系统校准电压

请注意,AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2的输入范围为"0.8 × VREF ÷ 增益"至"2.1 × VREF ÷ 增益"(对于AD7124-4和AD7124-8,增益 = 1至128;对于AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2,增益 = 1)。因此,用户可以调整输入范围。这一点很实用,因为有些设计可能并不使用整个ADC输入范围。例如,传感器产生的信号可能仅占ADC所允许的输入范围的95%。在这种情况下,可以向ADC施加"0.95 × VREF ÷ 增益"的输入信号,ADC使用这一幅值的信号即可执行系统满量程校准。

执行校准

通过将相关值写入ADC_CONTROL寄存器(对于 AD7124-4和AD7124-8)或ADC模式寄存器(对于AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2)的ADC模式位即可启动校准。校准启动时,DOUT/RDY引脚和状态寄存器的RDY位会变为高电平。校准完成时,相应失调或增益寄存器的内容会更新,状态寄存器的RDY位为低电平,DOUT/RDY引脚返回到低电平(如果CS为低电平)。因此,RDY下降沿或RDY状态位会指示校准何时结束,用户不必监视校准时间。

校准顺序取决于ADC。对于AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2,如果要执行失调和增益两种校准,建议先执行零电平校准再执行满量程校准。

对于AD7124-4和AD7124-8,仅当失调寄存器为其默认值0x800000时,才能执行内部满量程校准。因此,如果要执行内部零电平和内部满量程两种校准,建议按下述程序操作:

- 将失调寄存器值复位为0x800000。

- 执行内部满量程校准。

- 执行内部零电平校准。

对于系统校准,必须先执行系统零电平校准,再执行系统满量程校准。

内部满量程校准所需的时间等于1个建立周期(增益为1时)或4个建立周期(增益大于1时),其余三种校准所需的时间等于选定滤波器的建立时间加上要完成的输出数据速率。

AD7124-4和AD7124-8仅支持在低功耗模式或中功耗模式下执行校准。

请注意,增益误差和失调误差校准均可在任何增益或输出数据速率下进行。校准是模拟输入已知的转换过程。不过,建议以较低的输出数据速率执行校准,因为输出数据速率越低,噪声越低,AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2的性能也就越容易达到最佳水平。最终得到的校准系数适用于任何输出数据速率。

使用校准系数

AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2的模拟输入电压使用ADC输出代码来表示。失调二进制代码对于两个系列均适用。

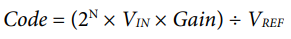

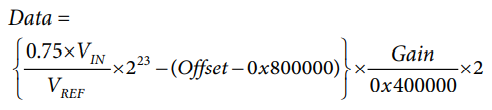

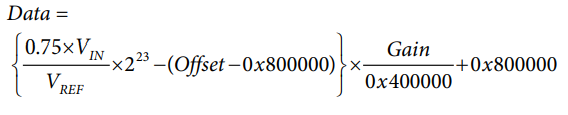

因此,单极性工作模式下的理想关系为

双极性模式下,计算公式变为

其中:

N = 24,位数(分辨率)。

VIN 为模拟输入电压。

VREF 为基准电压。

增益为增益设置(对于AD7124-4和AD7124-8为1至128;对于AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2,则仅为1)。

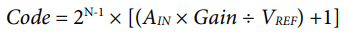

由于ADC转换结果中一定包括失调和增益校正,因此实际的ADC输出代码会略有不同。

单极性模式下的关系为

双极性模式下的关系为

其中:

失调为失调系数。

增益为增益系数。

这些公式使用失调和增益系数来调整ADC数字输出。

请注意,在ADC内采样的模拟输入减少25%。执行这一调整的目的在于确保不向Σ-Δ调制器施加满量程信号,从而保证调制器绝不会达到饱和状态。值得注意的是,在整体计算中衰减会由"增益 ÷ 0x400000"这一系数校正。

CN-0381突显出对AD7124-8执行增益和失调校准后精度的提升。

CN-0381原理图如图8所示。该系统使用AD7124-8,并为ADC连接了一个Pt100温度传感器 (RTD)。对ADC转换结果执行传感器的线性化校正。

图8. CN-0381原理示意图

在AD7124-8 处于环境温度的条件下,RTD在-50°C至+ 150°C的温度范围内的测量结果精度超出了使用默认增益和失调系数时的预期范围。

然而,在25°C温度下进行一次内部失调和增益校准后即提高了精度,并且系统结果完全在Pt100 RTD的预期特性曲线范围之内。图9显示了使用AD7124-8时Pt100 RTD传感器的结果。

图9. AD7124-8校准前后Pt100特性曲线测量值的变化、Pt100B级温度精度与温度的关系

何时执行校准

校准必须在上电后执行。因此,作为初始化程序的一部分,必须选中所有正在使用的通道并进行配置。例如,选择基准源并设置增益。然后必须对通道执行失调校准和增益校准。执行校准时只能使能一条通道。如果使能多条通道,ADC将仅校准最先使能的那条通道。如果更改了增益值,则必须重新校准通道。

一些用户喜欢定期执行校准,以便最大程度降低失调误差和增益误差漂移。执行频率取决于用户应用的温度变化速率。

不过,AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2和AD7177-2的失调漂移和增益漂移都很低。因此对于许多应用而言,在上电后执行一次校准即可满足要求。

内部校准通常用于调整因ADC漂移特性而引入的失调误差和增益误差。CN-0381显示了如何在整个温度范围内使用内部校准来微调AD7124-8的失调误差和增益误差。

系统校准用于补偿ADC系统的前端或外部电路所引入的失调误差和增益误差。系统校准最适用于称重应用,因为称重传感器的精度会发生漂移。为了微调漂移所引起的精度变化,用户必须执行系统校准。

结论

ADI公司的Σ-Δ型ADC可提供内部和系统级的增益误差和失调误差校准。这些片内校准功能可提高整体系统精度,为用户免去样品校准流程,从而简化整体设计并节省时间。