CareFusion社とアナログ・デバイセズとのディスカッション: EEG アンプ性能の最適化と消費電力の削減

この20年間、CareFusion Nicolet社は EEG 診断システム領域を開拓してきました。EEG (脳波) モニタリングは、睡眠研究、脳マッピング、脳卒中患者のICU モニタリングで神経学的解析に使用されています。脳研究とEEG 診断でのブレークスルーが続く中で、EEG モニタリング機器は従来の臨床環境の外側での新しい環境で動作することが期待されています。これらの新しい環境により新しいデザイン問題が発生しています—この資料ではこれらの問題の幾つかをとりあげます。

Harry (アナログ・デバイセズのオペアンプ・アプリケーション・エンジニア): 私は、最近、BillとMattの二人とEEG フロントエンド(計装アンプ) デザインの初期ステージでのトレードオフについて幾つかの議論をしました。三人はその内容を他の設計者とも共有することが有益だと思いました。

Matt (アナログ・デバイセズの計装アンプ・アプリケーション・エンジニア): その通りです。Billは、当社ポートフォリオ内の多くの計装アンプを調べましたが、独自の計装アンプ を構築する必要があるという結論になりました。これは、性能重視のアプリケーションでは非常に珍しいことなので、この思考プロセスを説明したいと思います。Bill、デザイン目標の概要を説明してください。

Bill Kolasa (CareFusion社の主任電気技師): 我々は現在、計装アンプを採用したデザインを持っており、性能は良いのですが、ある性能特性を最適化すると同時に消費電力を削減したいと思っています。

EEG機器とECG 機器の多くの設計者が知っているように、電極の半電池電位の差から大きなDC オフセットが発生し、計測システムがこれに耐える必要があることです。我々の現在のシステムは、最大±900 mV オフセットに対応できるようにデザインされています。様々な電極タイプとフィールドで遭遇する環境条件に対処するため、±1300 mVまで許容電圧を上げたいと思っています。

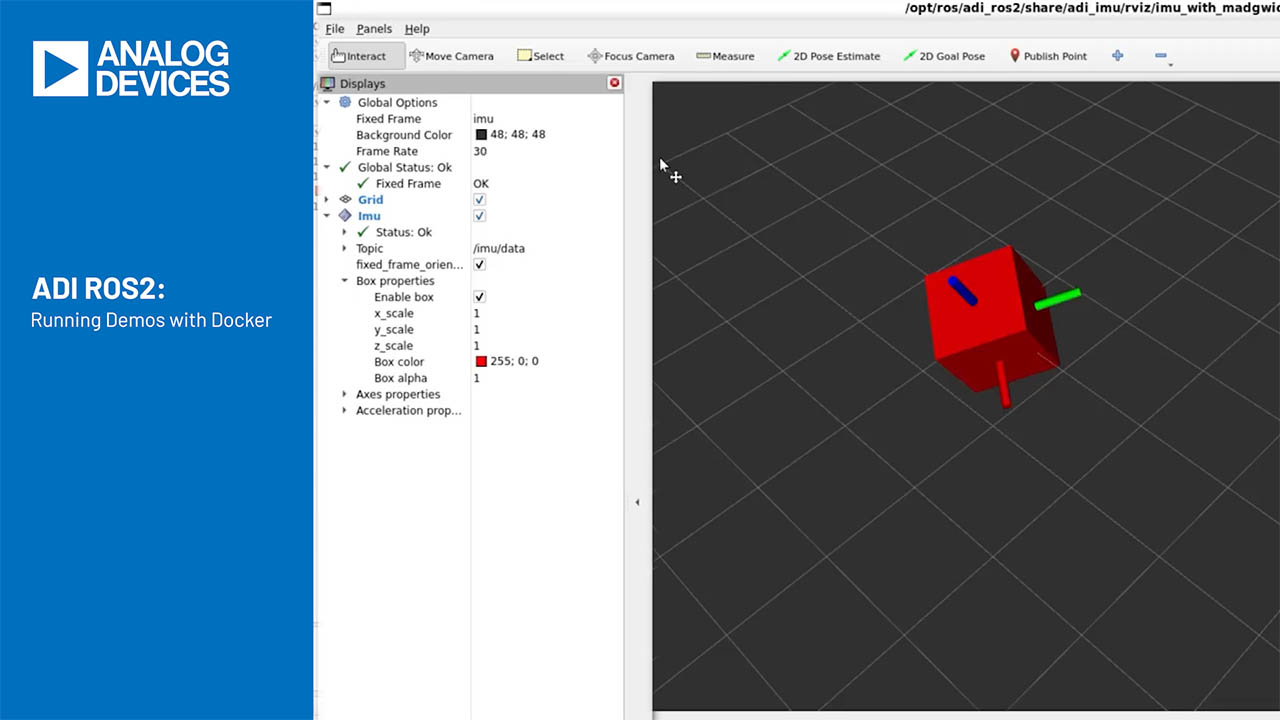

図1.EEG のシグナル・チェーン

これと同時に、バッテリ駆動のデザインを完成させようとしています。このため、計装アンプなどのすべての部品の消費電力を大幅に削減する必要があります。現在の消費電力はチャンネルあたり28 mW で、これを10 mW以下に削減したいと思っています。消費電力を削減しようとすると、ノイズが増加してしまうオプションしかありませんでした。

Matt: このトレードオフは、当社のECG 顧客とEEG 顧客でも多くみられますECGとEEG のフロントエンド・デザインの場合、ノイズ、オフセット処理能力、消費電力との間に固有のトレードオフがあります。

大部分の計装アンプは、減算ステージのノイズに起因する大きなノイズ成分を持っています。高ゲイン・アプリケーションでは、このノイズはゲインに無関係に出力で一定であるため、大きな問題にはなりません。このため、入力換算ノイズは非常に小さいものです。

残念ながら、EEG とECG のアプリケーションでは、ゲインは電極で生ずる大きなオフセットで制限されます。ノイズ性能を良くするために大きなゲインを使用しようとすると、この大きなオフセットに対処するため大きな電源を使用せざるを得なくなります。

Bill: これが、AD8221 計装アンプを採用した前のデザインで我々が直面したことです。出力ノイズは75 nV/√Hz で、入力ノイズは8 nV/√Hzです。大きな出力ノイズの入力換算成分を小さくするため、AD8221のゲインを14.8に設定しました (ノイズ計算の詳細については、式 1と式 2参照)。また、ゲイン増により同相モード・ゲイン = 1で同相モード除去比も23 dBだけ大きくなりました (式 3参照)。しかし、このゲインで 900 mV の電極オフセットに対応するためには、±15.5 V DCの電源を使用する必要があります (式 4参照)。EEG アンプで構成されるこれらのチャンネルが64 個ある場合には、バッテリ駆動アプリケーションとして消費電力が大き過ぎます。

私は、アナログ・デバイセズが低出力ノイズの計装アンプを提供するのを待ち続けています。提供は何時になりますか?

Matt: 計装アンプの出力ノイズは、主に6個の抵抗(図 2のR1~R6)から発生します。これらの抵抗値を小さくすることができますが、これには次の欠点があります。1) 計装アンプ・アンプからこれらの抵抗を駆動しなければならない電流が増えます。これらの大きな駆動状態で優れた直線性を維持するためには、電流を多く消費する"たくましい"アンプをつくる必要があります。小さい値抵抗を通して大きな電流を供給することと、"たくましい" アンプへ大きな電流を供給することの2つの"魔法"を行うことになります。

図2.Textbook 計装アンプの構成

Bill: 私の消費電力問題にとってはグッド・ニュースでないようです。

Matt: Rg ゲイン設定抵抗は小さくできると思います。これはノイズにとつては良いのですが、大きな差動過電圧状態が予想される場合には良くありません。高ゲインでの大きな差動電圧に対してアンプ入力が弱くなります。この問題に対処するため回路を追加できますが、この回路により入力ノイズが増えます。

Bill: 電極入力には既に保護回路があるので、これは問題となることはないと思います。

Matt: 減算回路の抵抗を小さくすると、リファレンス・ピンの入力インピーダンスも小さくなります。これは、バッファを使ってこのピンを駆動しようとすると (このタイプのアプリケーションでは一般的なことです)、駆動アンプは注目する周波数範囲で非常に小さい出力インピーダンスを持つ必要があることを意味します。あるいは、システムのCMRR周波数特性が低下します。周波数に対して出力インピーダンスを小さくすると、消費電力の大きいドライバ・アンプが必要になります。

Bill: その通りです、このピンを駆動している当社の新しいデザインでは、これが問題になっています。ピンをグラウンドに接続する場合と同じCMRR 性能を持つバッファを探しました。

元の問題に戻ると、±15.5 V動作で電源電流0.9 mAのAD8221 がありました。計装アンプの電流を小さくし、電源電圧を低くすることにより消費電力を小さくしようとしました。低消費電力で、かつその他の我々の性能条件を満たすデバイスを探すことから開始しました。

我々が調べた計装アンプはAD8235/AD8236でした。このデバイスの消費電力は非常に小さくかつ小型でしたが、ノイズが大き過ぎ、かつ最大電源電圧が5 Vであったため、我々のDC オフセット仕様を満たしませんでした。

Matt: これらはCMOSベースの計装アンプで消費電流は40 μAです。消費電力が性能より大事なECG モニタリング・アプリケーションでは最も多く採用されていますが、CareFusion社の診断 EEGには不十分です。

Bill: 検討したもう1つのデバイスはAD627でした。これも、消費電力が非常に小さく、電源電圧が広くなっています。過去にノイズをテストしていたので、消費電力に対して優れた性能であることを知っていましたが、SOIC パッケージを採用していました。このパッケージは今日では大き過ぎて、小さいボード・サイズには合いません。

Matt: その通りです。これには対策が必要です。

Bill: その後、貴社は300 µA~500 µA の電源電流と広い電源範囲を持つ例えばAD8226やAD8227のような広範囲なデバイスを提供しましたが、これらすべてのデバイスは少なくとも20 nA の入力バイアス電流を持っています。このデザインで規定した5nA以下の条件を超えています。

Matt: AD8226やAD8227のようなデバイスでは、負電源まで連続して電圧を測定できる機能を必要としていました。このためにシンプルな入力ステージを使ったため、入力バイアス電流を確保することを犠牲にする必要がありました。AD8221では、入力バイアス電流補償機能とスーパーベータ・トランジスタを使って最小数百pAまでのバイアス電流を確保しました。これにより多くの当社顧客は満足しましたが、そこではこの入力でのヘッドルームをある程度犠牲にせざるを得ませんでした。

Bill、このバイアス電流仕様は何によるのですか? EEG 電極は約10 kΩのソース・インピーダンスを持っていると思うのですが?AD8226の場合、入力バイアス電流は最大27 nAであり、これは270 uVになります。これは、電極の大きなオフセットと比較にならないです。バイアス電流仕様は何によるのか説明してくれませんか?

Bill: この5 nA 仕様は、非常に高い電極インピーダンスを扱う必要のある当社のアンプからきていますが、このアンプはDCまでの EEG ディスプレイ帯域幅要求を持っています。電極インピーダンスの充電に起因してベースラインがドリフトする影響を小さくすることに注意していました。

ADI とその競合会社の計装アンプはすべて我々の条件を満たさないことが判った後、我々専用のものを構築することを決めました。100 dB より高いCMRRでは、減算ステージの抵抗一致が重要であることを知っていました。過去に抵抗一致回路の実験をしましたが、これらは高価であることが判りました。期待するCMRR 性能を得る見通しもありません。これは回路ボードの寄生容量が原因と思われます。AD8278 ディファレンス・アンプが我々が探している性能と消費電力を持っていることが分かりました。

Harry: 個の抵抗を使うディファレンス・アンプは、最初に登場したものより複雑になっています。完全なオペアンプでは、CMRRは抵抗の一致度により制限されます(図 2のR3~R6)。ディファレンス・アンプは次式で近似されます(参考資料1参照)。

ここで、Ad はディファレンス・アンプのゲイン。 t は抵抗偏差。したがって、ゲイン = 1で1% 抵抗の場合はCMRR = 50 V/V(約34 dB)に、0.1% 抵抗の場合はCMRR =500 V/V(約54 dB)に、それぞれなります。

Bill: 貴社のハンドブックで同じ説明を見たことがあります(参考資料 2参照)。

Harry: 上式は低周波に適用されます。CMRRは高い周波数ほど低下します。例えば、PC ボード・レイアウトまたは内部チップ・レイアウトに起因して2つのオペアンプ入力の入力容量の差が 400~500 フェムトファラッドで、抵抗が10 kΩの場合、10 kHzでのAC CMRRは6 dB~ 7 dBだけ低下します。システム内に20 kHz 以上のスイッチング・レギュレータが存在する場合、これは重要なことです。

完全な抵抗と一致した容量を持っていても、CMRRは最終的にオペアンプにより制限されます。

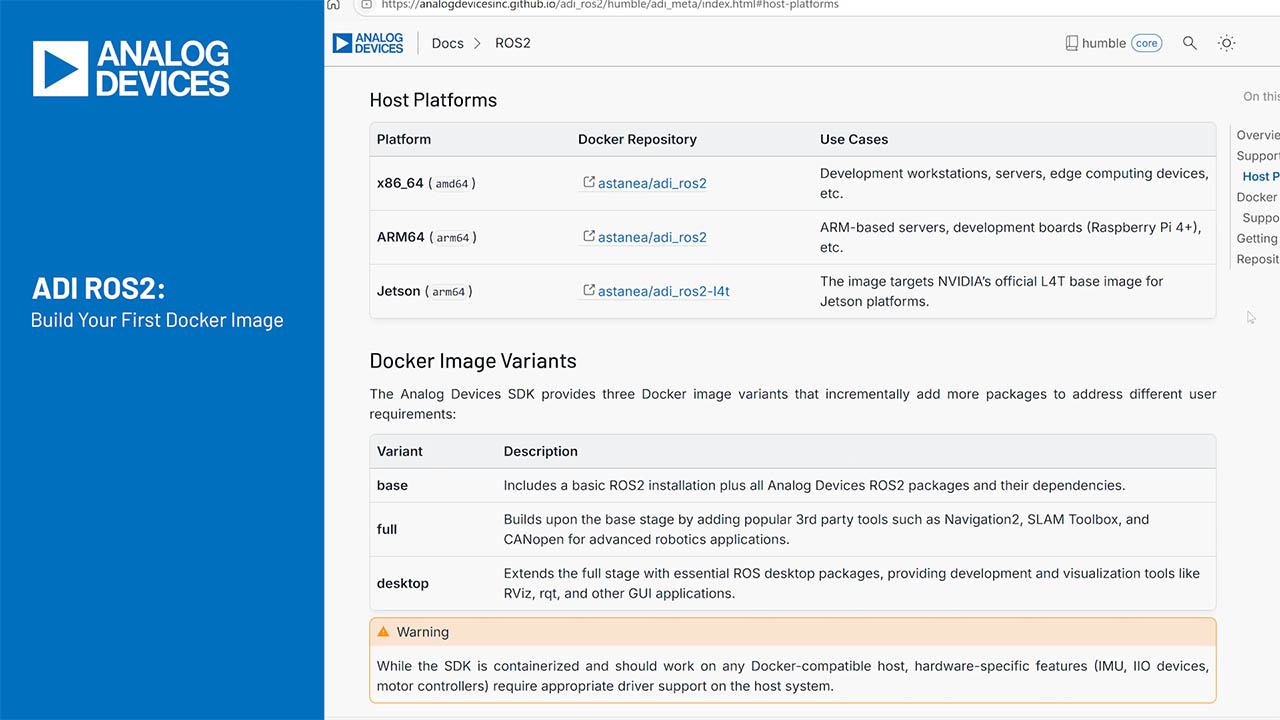

ディファレンス・アンプには2つの主要な性能分類があると思います。1つ目は、一般的なハイサイド電流検出アプリケーションであり、電流範囲の上限側で3%~5% の精度が必要です。 妥当なオフセットと1% 程度の抵抗を持つ低価格オペアンプがあります。 低価格オペアンプの幾つかはCMRRが50 dB以下であることに注意してください。これは見落とされることがあります。2つ目は、0.1%~1% の範囲と70 dB~80 dbを超えるCMRRを持つ、ディスクリート計装アンプの2段目ステージで使われるような高精度アプリケーションです。 これは、優れたオペアンプ、4個の一致した低TC抵抗、望ましくは比の一致したTC、慎重なPCBレイアウトにより実現することができます。合計コストとボード・スペースを考慮すると、モノリシックのディファレンス・オペアンプが最適に見えます。Bill がAD8278を選択した理由が理解できます。彼のために我々は最善を尽くしました。

Bill: アナログ・デバイセズは、ゲイン = 1/2、1、2のディファレンス・アンプ・ファミリーを提供しました。我々はAD8271とAD8278を比較して、低消費電力のAD8278を選択しました。これにゲイン = 1/2を設定しました。これにより、入力バッファのゲイン増加と電源電圧の低下 (±7.5V dcに設定)が可能になり、ノイズとDC オフセットの許容偏差仕様を満たすことができました。できるだけ多くのゲインを入力バッファへ移すことにより最小ノイズを実現したと信じています(新しいデザインのノイズ、CMRR、オフセット偏差については式 5~式 11参照)。

Matt: AD8278はゲイン = 1/2またはゲイン = 2に設定することができます。一般に、アンプ・ゲインをできるだけ高く設定して最適ノイズ性能を得ることが必要と考えられていますが、このデザインではAD8278は2段目ステージであるため、デザインのノイズ性能にとって、実際にはゲインを低く設定していることが役立っています。このために、Billは初段ステージに多くのゲインを配分できました。低ノイズ・デザインの基本ルールは、できるだけ多くのゲインを初段ステージに配分することです。実際にここではそのようになっています。

前段に配分するゲインを多くすることは、計装アンプのCMRRにも役立ちます。抵抗許容偏差対CMRRの前の議論から計算できるように、ディファレンス・アンプ・ゲインを1/2から2 へ変更すると、 CMRRが6 dB大きくなります。

これは AD8278 のデータ・シートにも一致していますが、前段でゲイン4に上げると、差動ゲインが4だけ増加し、同相モード・ゲインは不変です。言い換えると、前段のゲインを上げることにより、12 dBのCMRR増が得られることになります。これに対して、ディファレンス・アンプのゲイン増ではCMRR増は6 dB だけでした。このトリックは初段ステージのオペアンプが優れたCMRRを持っている場合にのみ機能することに注意してください。したがって、高品質オペアンプを使うことが重要です。

ディファレンス・アンプ・ステージにG = 1/2を使うことは、当社の集積計装アンプを使用する代わりに、ディスクリート・デザインをBill が最適化する際に使用できる1つの方法です。当社の集積計装アンプの場合、ディファレンス・アンプをG ≥ 1 に維持する必要があります。これはディファレンス・アンプのゲインを低くすると、広い同相モード電圧振幅を処理する計装アンプの能力が制限されてしまうためです。

Bill: 我々は広範囲な調査の後、入力バッファ・オペアンプとしてAD8622を採用しました。このオペアンプは、小型パッケージ・サイズ、低消費電力、低入力バイアス電流、 0.1~10 Hz で低ノイズ、広い電源電圧の我々が求めていたすべての仕様を満たしていました。我々の考える重要なその他の特性はユニティ・ゲイン安定性です。我々のバッファはゲイン = 10で動作しましたが、計装アンプ構成では同相モード信号がゲイン = 1となるため、安定性の問題が生ずる可能性があります(参考資料 3参照)。

Harry: フロントエンド・オペアンプの場合、数百もの選択肢があります。このため、大きなオフセット電圧、バイアス電流、電源電流、バイアス電流などにより、デザインを最適化することができます。計装アンプをデザインする際、広範囲なトレードオフを行う必要があります。このため、最後の10パーセントの性能のために、努力する価値があります。AD8622は当社高精度アンプ・ラインに追加された最新バージョンであり、電圧ノイズ、低1/f コーナー、電源電流、ゲイン帯域幅、オフセット電圧、オフセット電圧ドリフトなどの優れた組み合わせを持っています。

私は、システムを分割する方法についてBillの補足を行いたいと思います。クワッド内の 3つのセクションが計装アンプとして使用される例を見ることがありますが、ここには陥り易い落とし穴があります。初段ステージの条件は、Vos、TCVos、ゲイン、帯域幅、CMRRなどに関してディファレンス・アンプ・ステージとは全く異なっています。この場合も、性能の最後の10パーセントのために、初段ステージのデュアルと2段目ステージのシングルとの間には大きな違いがあることに注目する必要があります。オペアンプで低電圧ノイズを得るためには、2段目ステージでは必要のないほどの大きい電流を流します。2段目ステージが重い負荷を駆動する場合には、初段ステージのオペアンプより大きな駆動が必要です。クワッドのもう一つの欠点は、出力オペアンプから初段ステージ・オペアンプへの熱帰還が生ずることです。詳細については、参考資料 4と参考資料 5を参照してください。

Bill: 我々の最初の選択肢は、ボード・スペースの理由で集積計装アンプを使用することでしたが、高精度ディファレンス・アンプが使用できるようになったため、高価でボードスペースを必要とする抵抗回路なしで計装アンプの調整ができるようになりました。消費電力を大幅に削減できると同時に、ノイズ、CMRR、DC 入力許容偏差などの重要な性能特性を維持することができました。

図3.簡略化した CareFusion社の計装アンプ

Harry: Bill、有り難うございました。Mattと私は、最新のデザインについて一緒に仕事を楽しむことができました。

アペンディックス: Billの式

ゲインの影響を示す、0.1 Hz~100 Hz 帯域でのAD8221の予測p-p ノイズの計算 (電極インピーダンスが小さいため電流ノイズは無視)。

1/f ノイズを算入 (データ・シートからゲイン = 10 を使用):

![]()

ゲインに起因する増加を表す、AD8221BRの予測最小CMRRの計算 (データ・シートからゲイン = 1を使用 ):

AD8221電極オフセット偏差 の計算:

新しい計装アンプ・デザインの場合 (インピーダンスが小さいため電流ノイズは無視)。

AD8622 バッファのノイズ:

1/f ノイズを算入 =

![]()

½ Rg とRfの並列接続のノイズ:

AD8278のノイズ:

1/fの算入:

すべてのソースを加算:

新しい計装アンプ・デザインの予測最小CMRR:

新しいデザインの電極オフセット偏差 (DCソースを一方の入力に接続、他方の入力をグラウンドへ接続)。