デジタル・ポテンショメータにより、スイッチング・モード電源を敏速かつ直線的に調整

電源の出力電圧を微調整する機能により、電力パスにおける許容誤差や電圧降下の解消、システムの限界における動作の検証、もしくはマイクロプロセッサのシンプルかつ動的な電圧制御の実行が可能になります。本稿では、スイッチング・モード電源(SMPS)を調整するためのいくつかのオプションについて解説すると共に、帰還制御部品としてデジタル・ポテンショメータを備えたスイッチング・レギュレータを使用するソリューションを提案し、設計上の課題や解決方法について説明します。最後に、このアプリケーションにおける一般的な制限を克服する簡単な方法として、シングル・チャンネルの不揮発性digiPOTであるAD5141を紹介します。

スイッチング・モード電源レギュレータは、大電流システムにおいてリニア電圧レギュレータよりも高い効率を実現しており、100µAを超える電流における標準的な効率は90%を超えています。

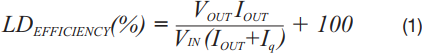

低ドロップアウト(LDO)レギュレータでは、効率は静止電流(Iq)および順方向電圧降下に依存しており、大きな静止電流が効率の低下を引き起こします(式1を参照)。

現行のLDOは適度に小さい静止電流のため、ILOADと比較してIqがはるかに小さい場合は無視することが可能です。その場合、LDOの効率は、シンプルに(VOUT/VIN) × 100となります。LDOには使用されない電力を大量に保存することはできないため、負荷に供給されない電力は、LDO内で熱として消費されます。LDOの標準的な効率は83%未満となります。

損失の少なさから、ATEやFPGAなどのアプリケーション、ならびに高電流または動的な負荷が求められる計測器では、リニア電圧レギュレータに替わり、スイッチング・レギュレータが使われます。

過酷な状態でシステム性能の特性評価を行う際、システム設計者は、電源電圧のレベルを最適化するため、もしくは公称値から強制的に引き離すため、電源電圧の調整が必要な場合があります。例えば、メーカーが正確に公称電源±10%で製品が機能することを確保したい場合など、この機能は通常、インサーキット・テスト(ICT)時に実行されます。

この手順はマージニングと呼ばれており、予測される範囲内で電源電圧を意図的に変えることで実施できます。加えて、出力電圧を微調整する機能により、電力パスにおける電圧電源の許容誤差、および電圧降下を補償することができます。

マイクロプロセッサの動的な電圧制御など、他のアプリケーションにおいては、低消費電力モードでは電圧を下げ、高性能モードでは電圧を上げるというように、電圧を随時変更できなくてはなりません。

図1に示すように、SMPSはLDOと同様に機能します。出力電圧は内部リファレンスと比較され、差分はパルス幅変調器に接続されます。

図1 SMPS電圧制御ループ

パルス幅変調器は、アンプ出力と上昇を比較し、負荷に電力を供給するスイッチを制御するPWM信号を生成します。

出力電圧は、反転アンプのピンで電圧を制御することで調整できます。

これは、DACまたはデジタル・ポテンショメータを使用して外部で行うことが可能です。レギュレータによっては、PMBUSやI2C、もしくはSPIといったシリアル・インターフェースを使用して、帰還電圧を内部で制御することが可能です。表1は、調整機能と消費電力に関する3つすべての方法を比較しています。

| 方法 | 粗調整 | 微調整 | 電源レール | 代表的な消費電力 |

| DAC | ミディアム | ハイ | VMIN < 2.5V | >100µA |

| digiPOT | ハイ | ミディアム | VMIN < 2.3V | >20µA |

| 内部レジスタ | ハイ | ロー | 該当せず | ロー |

一部のデジタル・ポテンショメータは、不揮発性メモリを備えているため、テスト時に出力電源をプログラムできます。この使いやすい機能は、他の2つの方法と比べ、大きなメリットをもたらします。

伝達関数式の直線化

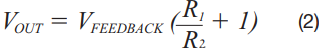

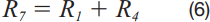

式2は、帰還抵抗R1およびR2の割合に基づくSMPSの出力電圧を表しています。

ここで、VFEEDBACKは内部リファレンス電圧です。

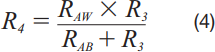

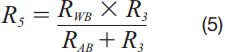

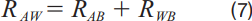

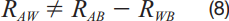

R1とR2をそのままデジタル・ポテンショメータに置き換える前に、いくつかの課題について考慮する必要があります。デジタル・ポテンショメータは内部にRAWとRWBの2つの抵抗ストリングを有しており、両方のストリング抵抗が相補しています。

ここで、RABはエンドtoエンドの抵抗、または公称値です。

R1とR2をRAWとRWBに置き換えることで、対数伝達関数が得られます。デジタル・コードと出力電圧との非線形な関係により、分解能の下限が低下します。図2に、16タップのデジタル・ポテンショメータの例を示します。

図2 対数伝達関数

この問題にはいくつかの解決方法があります。一般的な方法は、デジタル・ポテンショメータをレオスタット・モードで使用する方法、もしくはポテンショメータと直列に抵抗を配置する方法です。

許容誤差の最小化

抵抗許容誤差により、デジタル・ポテンショメータを外部抵抗と共に使用すると、不整合による問題が発生します。高精度デバイスの抵抗許容誤差は1%かもしれませんが、デジタル・ポテンショメータの大半は20%の抵抗許容誤差しか達成できません。

この場合には、図3および図4に示すように、直列や並列の抵抗を組み合わせて使用することで、不整合を低減できます。ただし、ダイナミック・レンジも低減します。

図3 レオスタットおよび直列抵抗

図4 ポテンショメータ・モード

レオスタット・モードでは、デジタル・ポテンショメータの許容誤差を無視できる大きさに直列並列を設定する必要があります。つまり、R2 ≥ 10 × RABです。ポテンショメータ・モードでは、並列抵抗を十分に小さく、つまり  にする必要があります。

にする必要があります。

図5の等価回路に示すように、直列と並列の組み合わせを使用したポテンショメータの直線化は極めて複雑です。

図5 最終Y – ∆ 変換

ここで、

通常、帰還入力ピンは高インピーダンスであるため、R6の影響は無視できます。

帯域幅の増加

スイッチング・レギュレータは通常、1MHzを超える高周波で動作し、小さな外付け部品も使用できます。最も厳しいケースでは、動的な負荷に給電する必要があり、そのため帰還抵抗ネットワークは、出力電圧を正確にトラッキングするのに十分な帯域幅を備えている必要があります。内部の寄生スイッチ容量により、デジタル・ポテンショメータはローパス・フィルタとして機能します。

図6に示すように、帰還ネットワークに十分な帯域幅がない場合は、出力電圧が振動します。

図6 帯域幅が限られている場合のディスクリート帰還抵抗とデジタル・ポテンショメータとの関係

この制限を克服する簡単な方法は、図7に示すように、出力と帰還ネットワークの間にコンデンサを並列に配置することで高周波インピーダンスを減らし、振動時間を最小限に抑えることです。

図7 並列コンデンサにより、高周波インピーダンスを減らし、振動を最小化

妥協のないシンプルなソリューション

アナログ・デバイセズの新しいAD5141 digiPOTは、他のデジタル・ポテンショメータで生じる問題を克服できます。特許化されたリニア・ゲイン設定モードにより、それぞれのストリング抵抗を個別に制御できます。

このモードをイネーブルすることで、外部抵抗が不要になります。抵抗許容誤差は無視できるようになり、伝達関数の総誤差は、内部ストリングの不整合に起因するもののみで、値も通常は1%未満です。

ストリング抵抗にはそれぞれ対応したEEPROM位置があり、起動時には各ストリング抵抗の個別の値をロードできます。その上、図8に示すように、このデバイスは高速帰還ループ用として最大3MHzの帯域幅を備えています。

図8 リニア・ゲイン設定モードのAD5141(10kΩ)バージョン

まとめ

スイッチング・モード電源レギュレータは高効率のため、大電流アプリケーションで広く使われています。本稿では、出力電圧をデジタル制御するために使用できる方法をいくつか説明しています。

事前定義された出力状態でシステムを起動することで得られる本質的な利点により、内部不揮発性メモリを備えたデジタル・ポテンショメータを使用するソリューションが望ましいと言えます。設計者が直面する主なトレードオフには、優れた性能を発揮するのに十分な分解能、精度、および帯域幅を確保することなどが挙げられます。AD5141 digiPOTを用いることで、設計者は妥協することなく最適なソリューションを実現できます。

著者について

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}

最新メディア 21

本記事に関するご注意

ご了承のほど、お願い申し上げます。