フラットパネル型フェーズド・アレイ・アンテナの設計を可能にするIC技術

概要

フェーズド・アレイ・アンテナは、より広範な用途で活用されるようになりました。その背景にあるのは半導体技術の進化です。機械的に制御されるアンテナからAESA(Active Electronically Scanned Antenna)への移行は、防衛分野で何年も前に始まりました。最近では、移動式衛星通信(SATCOM on-the-move)や5Gにおいて、AESAの採用が急速に進んでいます。小型のAESAには、高速に制御できる、複数の放射パターンを生成できる、信頼性が高いといった長所があります。ただ、広く利用可能な小型のAESAを実現するには、IC技術の著しい進化を待つ必要がありました。フラットパネル(平面)型のフェーズド・アレイには、消費電力が少なく高い効率で動作する集積度の高いデバイスが必要です。許容可能なレベルまで発熱を抑えつつ、各種のコンポーネントをアンテナ・アレイの背面に配置できるようにしなければならないからです。本稿では、フラットパネル型のフェーズド・アレイ・アンテナの実現を可能にするIC技術について説明します。この用途に向けたチップセットの進化について簡単に説明した上で、いくつかの具体例を紹介します。

はじめに

アンテナによる信号の送受において、指向性が重視されるケースがあります。従来、そうした場合には、主にパラボラ・アンテナ(ディッシュ・アンテナ)が使われていました。長年にわたる最適化を経た結果、そうしたシステムの多くは、比較的低コストで適切に動作するようになりました。しかし、機械的に制御されるパラボラ・アンテナには、いくつかの欠点があります。例えば、サイズが大きい、制御に時間がかかる、長期的な信頼性が低い、1つの放射パターンやデータ・ストリームにしか対応できないといった具合です。

機械的に操作される従来のアンテナと比べると、電気的に制御されるフェーズド・アレイ・アンテナは、数多くの長所を備えています。小型かつ軽量で、長期的な信頼性が高く、高速に制御でき、複数のビームに対応できるからです。フェーズド・アレイ・アンテナの設計においては、アンテナ素子の間隔が重要な意味を持ちます。多くのアレイでは、素子の間隔として、対象とする信号の約半波長分が必要になります。そのため、信号の周波数が高くなると特に設計が難しくなります。例えば、高い周波数に対応するICには、より高い集積度が求められます。また、パッケージング・ソリューションにも一層の高度化が要求されます。

フェーズド・アレイ・アンテナは、より多様なアプリケーションで利用できる可能性があります。ただ、従来はIC技術の限界がその実現を阻む要因になっていました。IC技術が進化を遂げた現在では、その問題は解消されつつあります。実際、デジタル制御、メモリ、RFなど、あらゆる機能を実現するトランジスタ回路を単一のチップに集積した高度なシリコンICが登場しています。また、GaN技術によってパワー・アンプの電力密度が著しく高まったことから、実装面積も大幅に縮小されています。

フェーズド・アレイ技術

市場では、アンテナ・アレイの小型化と軽量化が強く求められています。通常、厚板を使った従来のアーキテクチャでは、電子部品を搭載した小さなプリント基板(厚板)がアンテナのプリント基板の背面に垂直に配置されます。このアーキテクチャについては、20年間にわたり、厚板のサイズを縮小してアンテナの奥行きを抑えるために絶えず改良が加えられてきました。次世代の設計では、この厚板を使うアーキテクチャに代わってフラットパネルが使われるようになります。そうすれば、アンテナの奥行きが大幅に抑えられ、携帯型のアプリケーションや飛行型のアプリケーションでも利用しやすくなるからです。そのようなサイズの縮小を実現するには、アンテナの背面に配置できるように、各ICの集積度を十分に高めなければなりません。

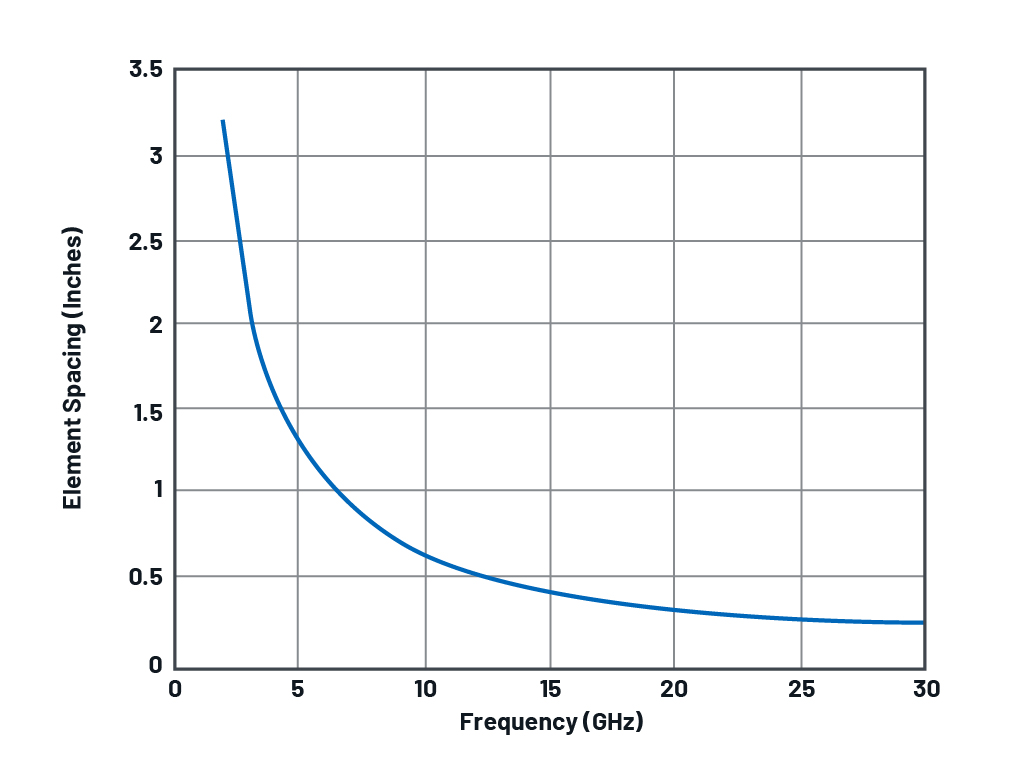

フラットパネル型のアレイの設計において、ICを配置できるアンテナ背面のスペースは、アンテナ素子の間隔によって制限されます。例えば、60°の走査角までにグレーティング・ローブが現れないようにするためには、アンテナ素子の間隔を最大0.54λに抑える必要があります。図1は、アンテナ素子の間隔(単位:インチ)の最大値と周波数の関係を示したものです。ご覧のように、対象とする周波数が高くなるにつれて、素子の間隔はかなり狭く設定する必要があります。その結果、ICを実装できるアンテナ背面のスペースはほんのわずかになります。

図1. アンテナ素子の間隔と周波数の関係。ボアサイトから60°の走査角までにグレーティング・ローブが現れないようにするためには、間隔をグラフの値以下に抑える必要があります。

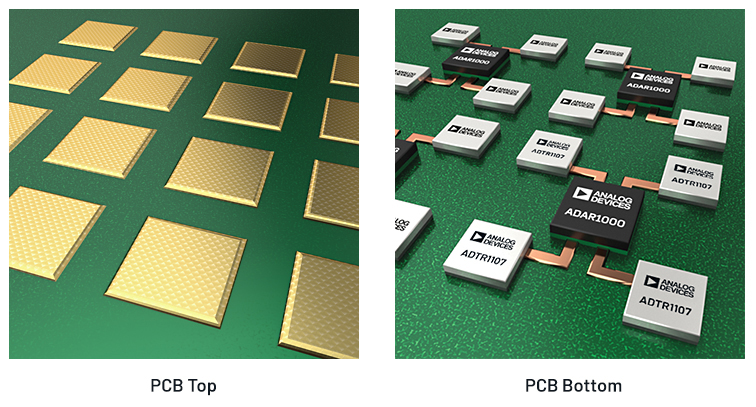

図2の左側は、プリント基板の上面の写真です。金色のパッチ・アンテナ素子が実装されていることがわかります。一方、図2の右側には、プリント基板の背面を示しました。ご覧のように、アンテナのアナログ・フロント・エンドが実装されます。一般的には、周波数変換段や分配回路を実装したレイヤが、これに追加されることになります。ICの集積度を高めれば、アンテナを設計する際に、必要な間隔を非常に確保しやすくなることは容易に理解できるでしょう。より多くの電子部品をより小さな面積で実装できれば、アンテナを小型化できることは明らかです。逆に言えば、適切なソリューションを実現するためには、新たな半導体技術とパッケージング技術が必要になるということです。

図2. フラットパネル型のアレイを構成するプリント基板。上面にはパッチ・アンテナが配置され、背面にはICが実装されます。

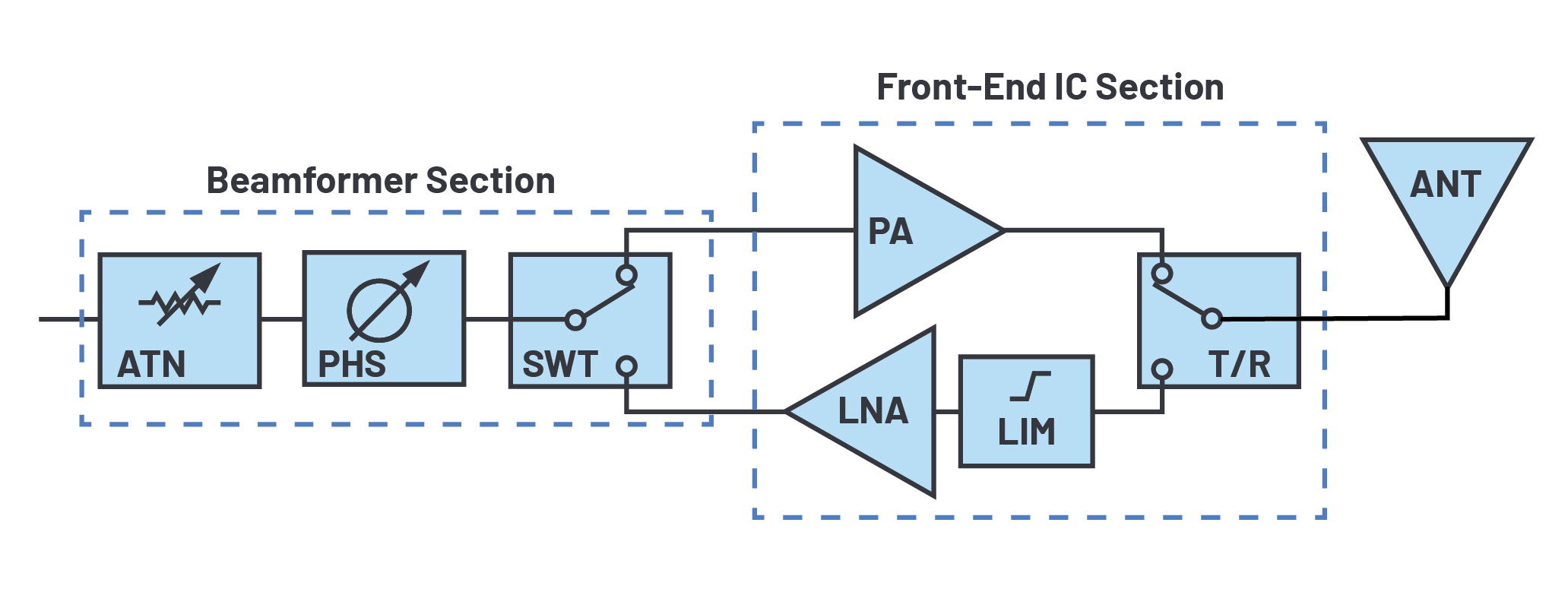

半導体技術とパッケージング技術

図3に示したのは、フェーズド・アレイ・アンテナのRFフロント・エンドです。マイクロ波/ミリ波対応のICによって構成されています。ビームフォーミングのセクションでは、アッテネータ(ATN)によって各アンテナ素子における電力レベルを調整します。それにより、アンテナ・パターンのサイドローブを低減します。続く位相シフタ(PHS)は、各アンテナ素子の位相を調整することで、アンテナのメインのビームを制御します。スイッチ(SWT)は、送信パスと受信パスを切り替える役割を果たします。フロント・エンドICのセクションでは、パワー・アンプ(PA)によって信号が送信され、低ノイズ・アンプ(LNA)によって信号が受信されます。このセクションにもスイッチ(T/R)が存在し、送信と受信の切り替えが行われます。従来は、各ICが個別にパッケージングされたデバイスとして提供されていました。より高度なソリューションでは、集積度が高いシングルチャンネルのモノリシック型GaAs ICが使用されることもあります。図では省略していますが、多くのアレイでは、ビームフォーマの前段にRF対応のパッシブ・コンバイナ、レシーバー/励振器、シグナル・プロセッサが配置されます。

図3. フェーズド・アレイ・アンテナの標準的なRFフロント・エンド

繰り返しになりますが、フェーズド・アレイ・アンテナの近年の普及を支えているのは半導体技術の進化です。SiGe BiCMOS、SOI(Silicon on Insulator)、バルクCMOSの先進的な微細プロセス・ノードにより、デジタル回路とRF回路が1つのICとして統合されるようになりました。そうしたICを使えば、アレイにおいてデジタル処理を実行しながらRF信号パスを制御することにより、位相と振幅に所望の調整を加えることができます。今日では、最大32チャンネルを備えるミリ波対応システムをターゲットとし、ゲインと位相の調整を担う4つのチャンネルを内蔵したビームフォーミング用のICを実現することが可能です。上記すべての機能を備えつつ、消費電力の削減に焦点を絞ったシリコン・ベースのICがモノリシック型のソリューションとして提供されているケースもあります。また、大出力のアプリケーション向けには、電力密度が非常に高く、フェーズド・アレイ・アンテナのユニット・セルに搭載可能なGaNベースのPAが提供されています。従来、この用途には、進行波管(TWT:Traveling Wave Tube)をベースとするPAか、比較的出力の小さいGaAsベースのPAが使われていました。

飛行型のアプリケーションにおいては、GaN技術による電力付加効率(PAE:Power Added Efficiency)のメリットを活かしたフラットパネル型のアーキテクチャが選ばれる傾向があります。GaN技術が進化したことから、大規模な地上配備型のレーダーにおいても、TWTを使用するパラボラ・アンテナからGaNベースのICを採用したフェーズド・アレイ・アンテナへ移行することが可能になりました。現在では、GaNベースのモノリシックICにより、50%を超えるPAEで100Wを超える出力を達成できるようになっています。このレベルのPAEと、レーダー・アプリケーションの低いデューティ・サイクルを組み合わせれば、生成される熱をパッケージの底面から放散できる表面実装型のソリューションを実現することが可能になります。表面実装型のPAを使用できれば、アンテナ・アレイのサイズ、重量、コストを大幅に削減できます。GaNには、純粋に出力が大きいという特徴があります。また、GaNベースのICを採用すれば、GaAsベースの既存のICと比べてサイズを縮小することができます。例えば、出力が6W~8WでXバンドに対応するGaNベースのPAであれば、GaAsベースのものと比べて実装面積を50%以上削減できます。フェーズド・アレイ・アンテナのユニット・セルにこうした電子デバイスを収めたい場合、この実装面積の差は大きな意味を持ちます。

パッケージング技術の進化も、フラットパネル型アーキテクチャにおける実装コストの削減に大きく貢献します。筐体については、信頼性を高めるために金メッキを施したハーメチック・シール筐体が使われることがあります。それにより、チップやワイヤから成る内部のインターコネクトを覆うということです。この種の筐体を採用すれば、過酷な環境に対する堅牢性を高められます。但し、サイズが大きくなり、コストも増大します。これについては、マルチチップ・モジュール(MCM:Multichip Module)が1つの解決策になります。MCMとは、複数のMMICと受動部品を比較的低コストの表面実装型パッケージにまとめて搭載したデバイスのことです。複数の半導体技術を組み合わせられるので、スペースを大幅に削減しつつ、各デバイスの性能を最大限に引き出すことができます。例えば、フロント・エンドICには、PA、LNA、T/Rスイッチなどが含まれています。この種のICでは、パッケージの底面に設けられたサーマル・ビアや銅スラグによって放熱します。現在、民生分野や航空宇宙/防衛分野の多くのアプリケーションでは、コストの削減を目的として非常に低コストの表面実装型パッケージが使われるようになっています。

フェーズド・アレイ・ビームフォーマICの具体例

集積度の高いアナログ・ビームフォーマICはコア・チップとも呼ばれます。この種のICは、レーダー、衛星通信、5Gなどのアプリケーション向けに開発されています。その主要な機能は、各チャンネルの相対的なゲインと位相を正確に設定することです。それにより、信号は所望の方向のアンテナのメイン・ビームにコヒーレントに結合されます。このような機能を実現するICは、アナログ・フェーズド・アレイや、アナログ・ビームフォーミングとデジタル・ビームフォーミングを組み合わせたハイブリッド・アレイ向けに開発されています。

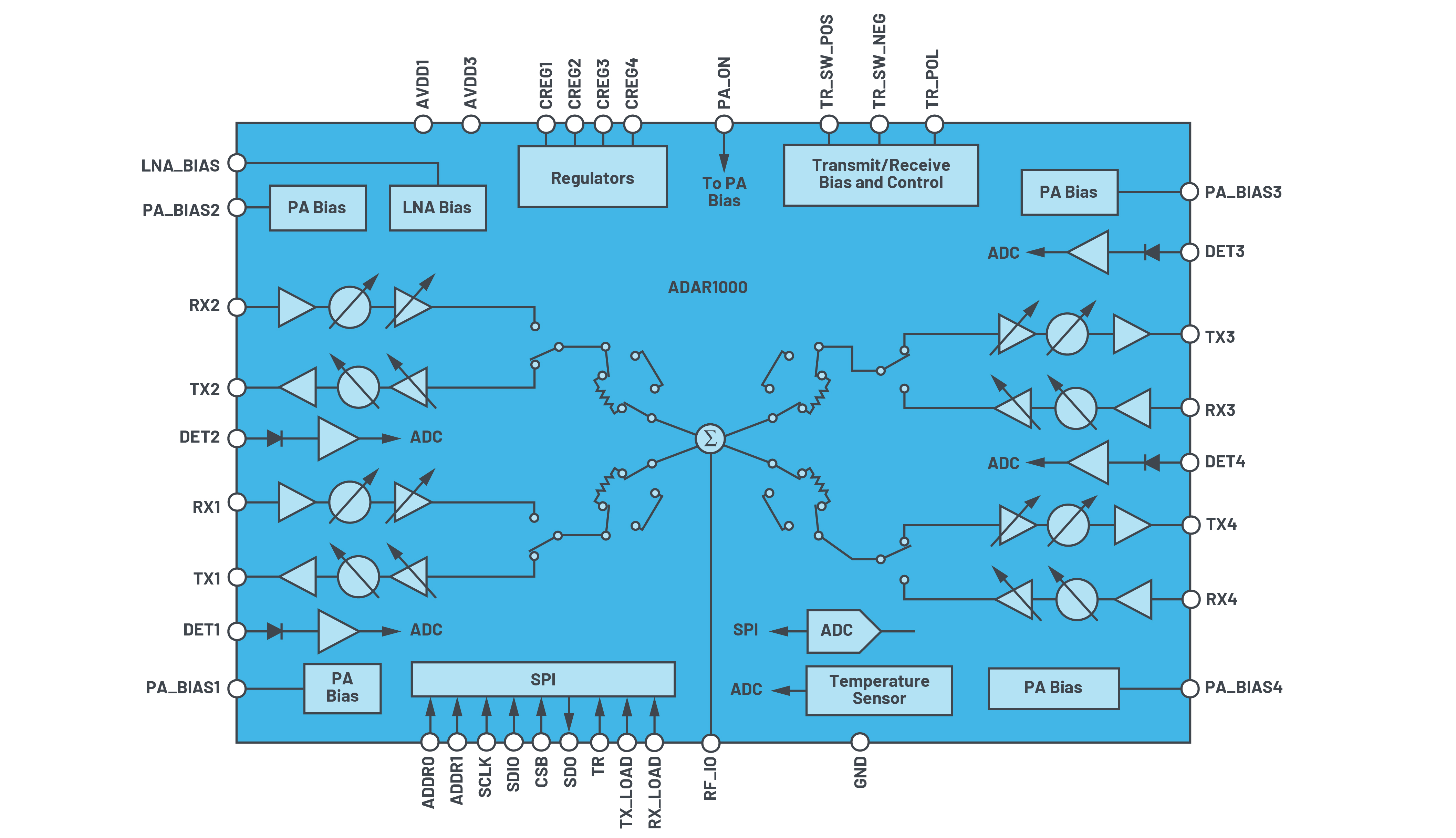

「ADAR1000」は、X/Kuバンドに対応するビームフォーマICです。トランスミッタとレシーバーを集積しており、4チャンネルの送受信に対応します(図4)。TDD(Time Division Duplex)モードにより、8GHz~16GHzの周波数範囲をサポートします。受信モードでは、4つの受信チャンネルを経由した入力信号が合成されます。合成後の信号は、共通のRF_IOピンから出力されます。送信モードでは、RF_IOから入力された信号が4つに分割され、各送信チャンネルから転送されます。

図4. ADAR1000の機能ブロック図

ADAR1000が内蔵するレジスタは、シンプルな4線式のSPI(Serial Peripheral Interface)によって制御できます。また、2つのアドレス・ピンを使うことにより、共通のシリアル・ラインによって最大4つのデバイスをSPIで制御することが可能です。専用の送信ピンと受信ピンにより、同一アレイ内のすべてのコア・チップの同期がとられます。また、1本のピンによって、送信モードと受信モードの迅速なスイッチング制御を実現できます。パッケージは、フラットパネル型のアレイに搭載しやすい7mm×7mmの表面実装型QFNです。このICは、集積度が高くパッケージが小型なので、チャンネル数の多いフェーズド・アレイ・アーキテクチャの課題の解決に役立ちます。つまり、サイズ、重量、消費電力の削減に貢献できるということです。同ICのチャンネル当たりの消費電力は、送信モードで240mW、受信モードで160mWです。送信チャンネルと受信チャンネルは、直接外部と接続することが可能であり、フロント・エンドICに適合するように設計されています。

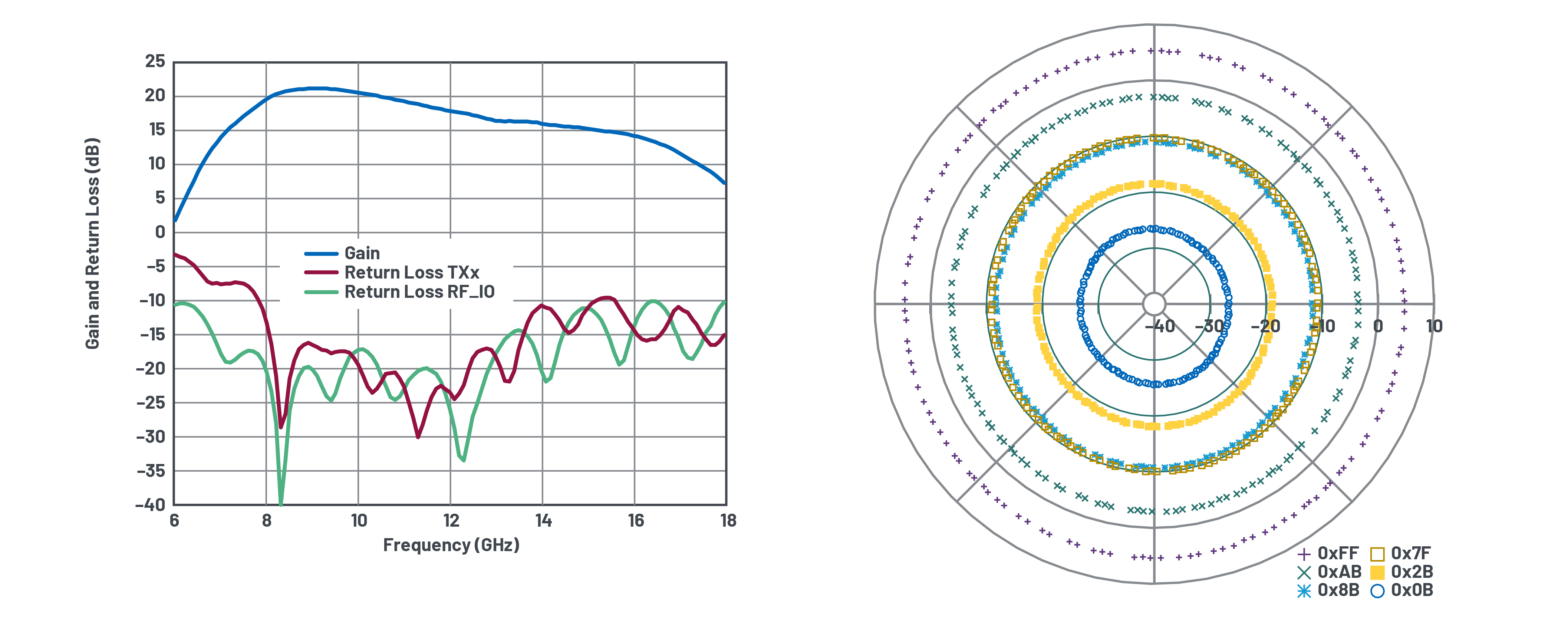

図5は、ADAR1000のゲインと位相について示したものです。同ICは、360°の位相全体を2.8°未満の位相分解能でカバーします。ゲインは30dB以上にわたって調整可能です。また、同ICは、最大121のビームの状態を保存できるだけのメモリを内蔵しています。ここで言う1つの状態には、IC全体のゲイン/位相の設定が含まれます。トランスミッタの飽和電力は15dBm、ゲインは約19dBです。レシーバーのゲインは約14dBとなっています。ゲインの設定に伴う位相の変化は、20dBの範囲で約3°です。同様に、位相の設定に伴うゲインの変動は、360°の位相範囲全体で約0.25dBです。これについては、簡単にキャリブレーションすることができます。

図5. ADAR1000のゲインと位相。左の図は送信側のゲインとリターン損失を表しています。右の図はゲインの設定と位相の変動の関係を表しています(周波数は11.5GHz)。

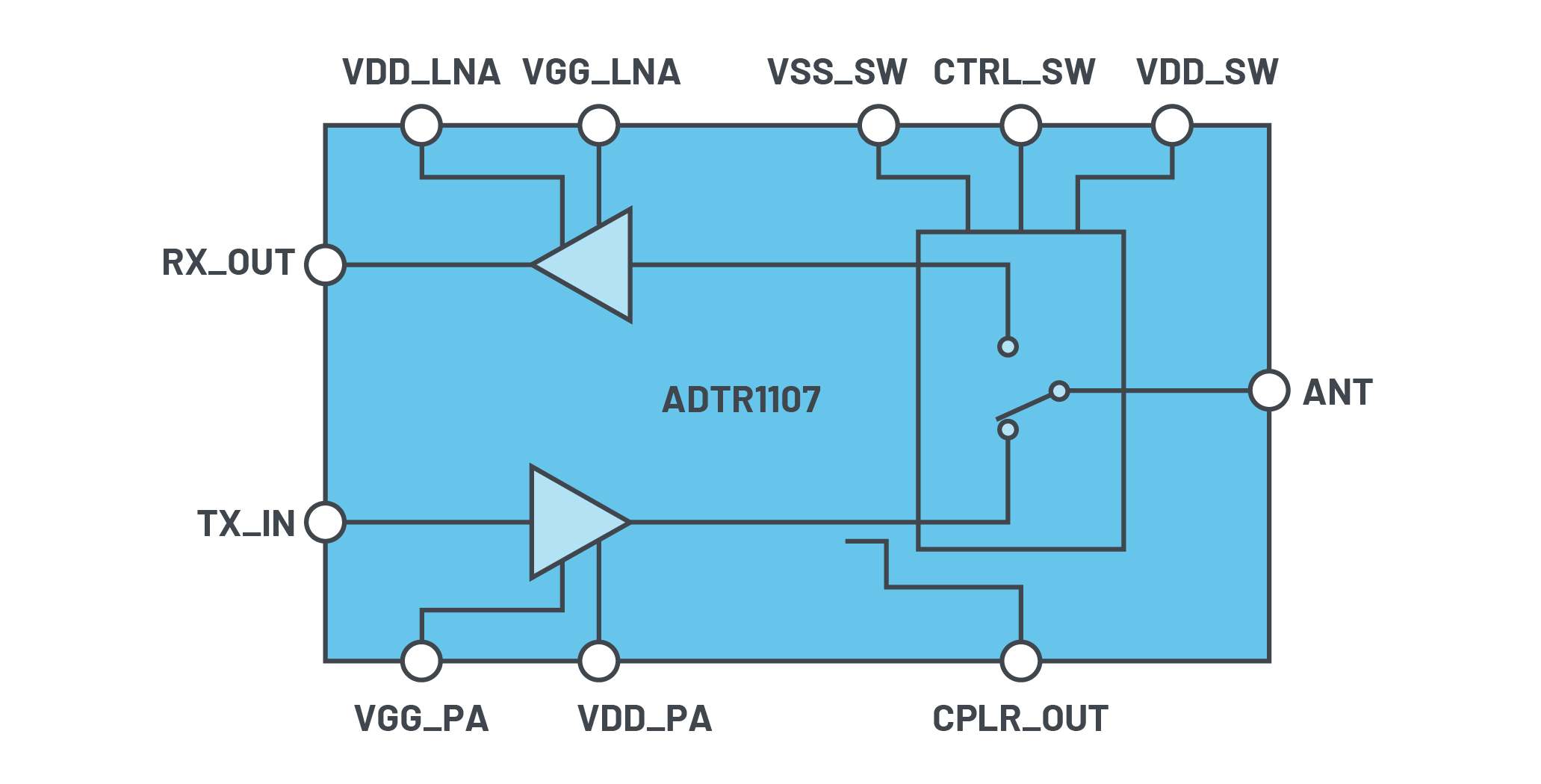

ビームフォーマICであるADAR1000は、フロント・エンドIC「ADTR1107」と組み合わせることができます。ADTR1107は、6GHz~18GHzに対応するコンパクトな製品であり、PA、LNA、SPDT(単極双投)反射スイッチを内蔵しています(図6)。

図6. ADTR1107の機能ブロック図

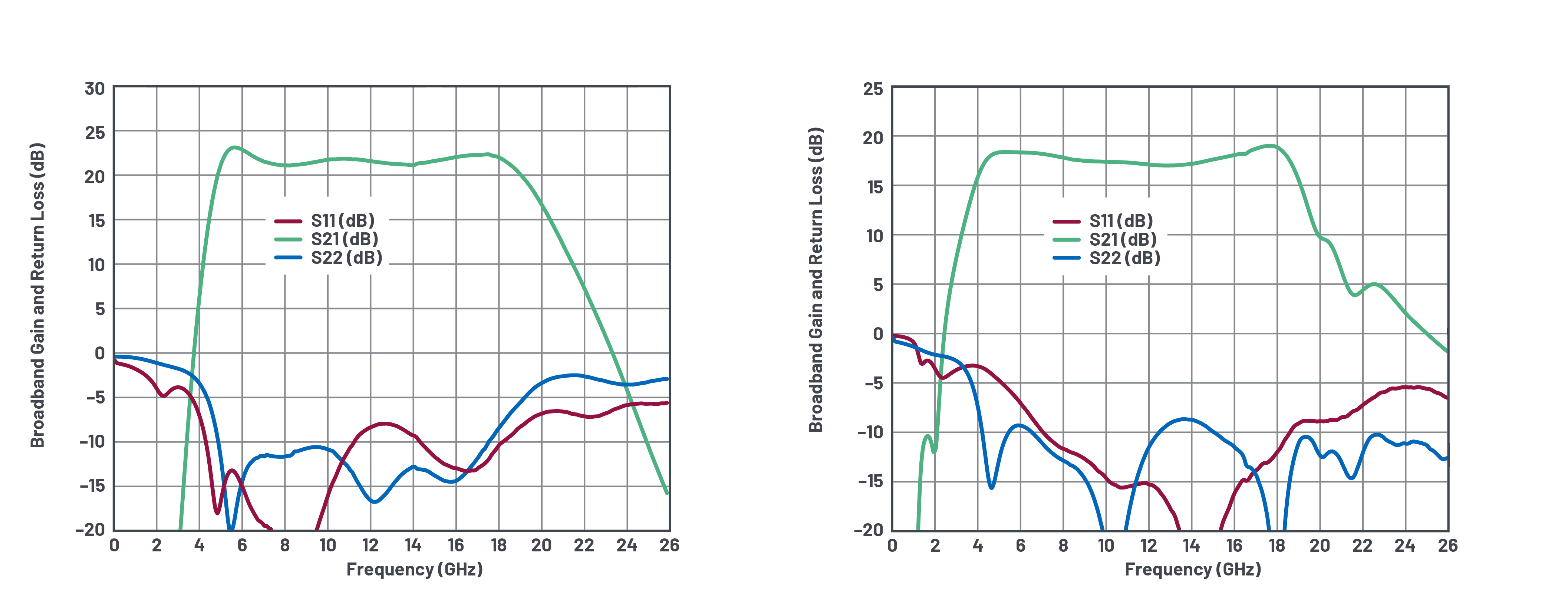

ADTR1107の送信側における飽和出力電力PSATは25dBm、小信号利得は22dBです。受信側における小信号利得は18dBで、(T/Rスイッチを含む)ノイズ指数は2.5dBです。電力の検出に用いるディレクショナル・カプラを備えており、入出力(I/O)は同ICの内部において50Ωでマッチングしています。パッケージは5mm×5mmの24ピンLGAです。図7に、同ICのゲインとリターン損失を示しました。

図7. ADTR1107のゲインとリターン損失。送信側と受信側の周波数特性を示しました。

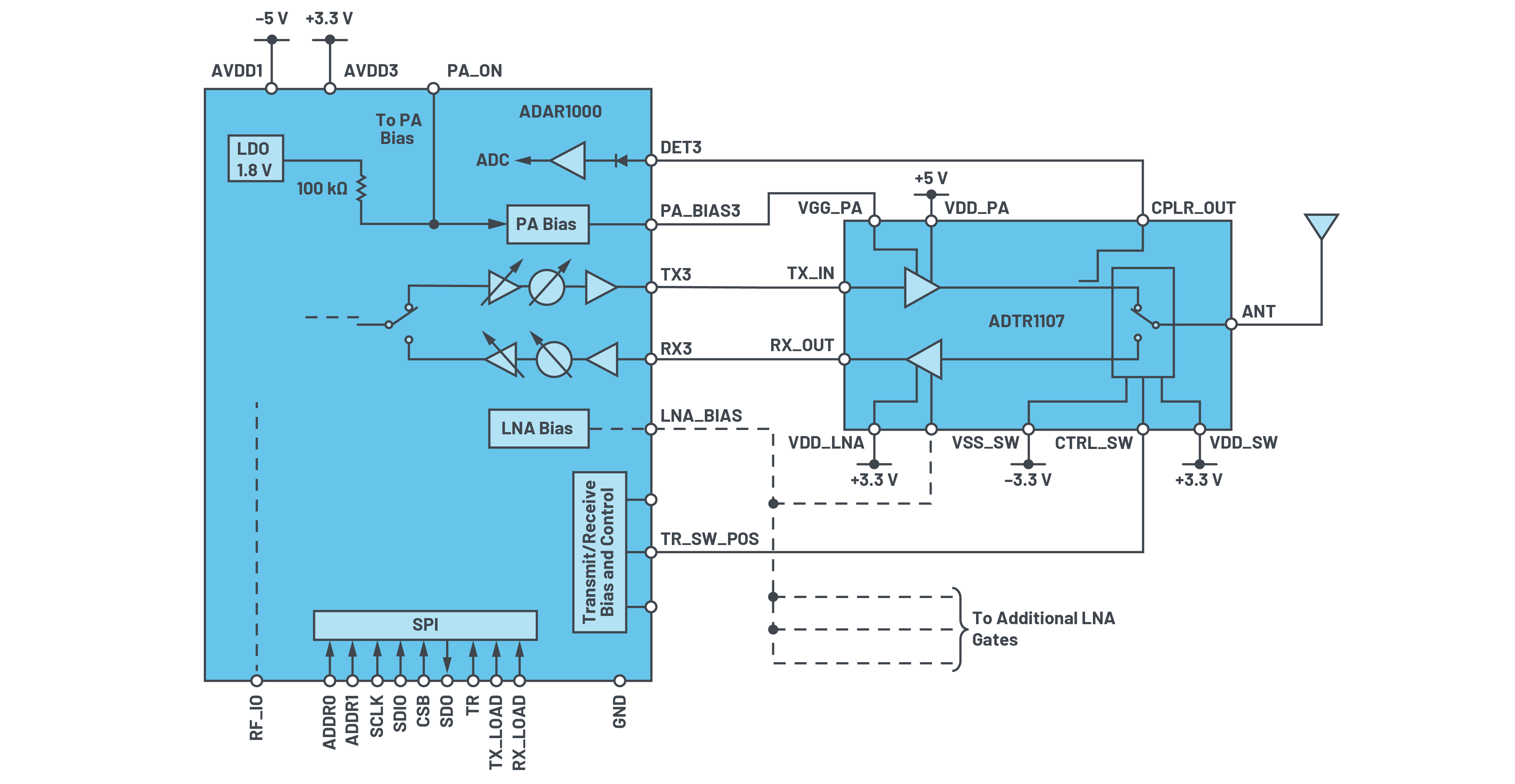

図8に示すように、ADTR1107はADAR1000と簡単に接続できます。コア・チップである1つのADAR1000により、4つのADTR1107を駆動することが可能です。わかりやすくするために、図8では1つのADTR1107との接続だけを示しています。

図8. ADTR1107とADAR1000の接続。前者はフロント・エンドICであり、後者はX/Kuバンドに対応するビームフォーマICです。

ADAR1000は、フロント・エンドICに対するシームレスなインターフェースを備えています。それにより、必要なすべてのゲート・バイアス電圧と制御信号を供給します。ADTR1107自身がLNA用のゲート電圧を供給している場合には、ADAR1000からその電圧を制御することも可能です。ADTR1107のPAに対するゲート電圧もADAR1000から供給できます。1つのADAR1000によって4つのADTR1107を駆動するので、ADAR1000はPAのゲート・バイアス用に4つの独立した負の電圧を生成する必要があります。各電圧は、8ビットのD/Aコンバータを利用して生成されます。それらの電圧は、ADAR1000のTRピンに対する入力か、SPIによる制御データによってアサートされます。ADAR1000がアサートされたら、TRピンによって受信モードと送信モードを切り替えられます。TR_SW_POSピンを使えば最大4つのスイッチのゲートを駆動することが可能なので、ADTR1107が備えるSPDTスイッチの制御に使用できます。

ADAR1000の4つのRFディテクタ入力(DET1~DET4)のうち1つにADTR1107のCPLR_OUTピン(カプラ出力)を接続すれば、送信出力電力を測定することが可能です。RFディテクタはダイオードをベースとしたものであり、-20dBm~10dBmの入力範囲に対応します。ADTR1107が備えるディレクショナル・カプラの結合係数は、28dB(6GHz時)~18dB(18GHz時)です。

ADTR1107へのパルスの印加は、ドレインを一定の値に保ちながらADAR1000によってゲート電圧を駆動することで実現します。この方法は、ドレインにパルスを印加する方法よりも優れています。ドレインにパルスを印加するには、大電力に対応可能なMOSFETとゲート駆動用のデバイスが必要になります。それに対し、ゲートを駆動する方法であれば電流量を抑えられます。なお、ADAR1000は、送信モードではADTR1107を飽和させるほどの電力を出力します。またADTR1107は、アンテナが短絡した場合に総反射電力に耐えられるように設計されています。

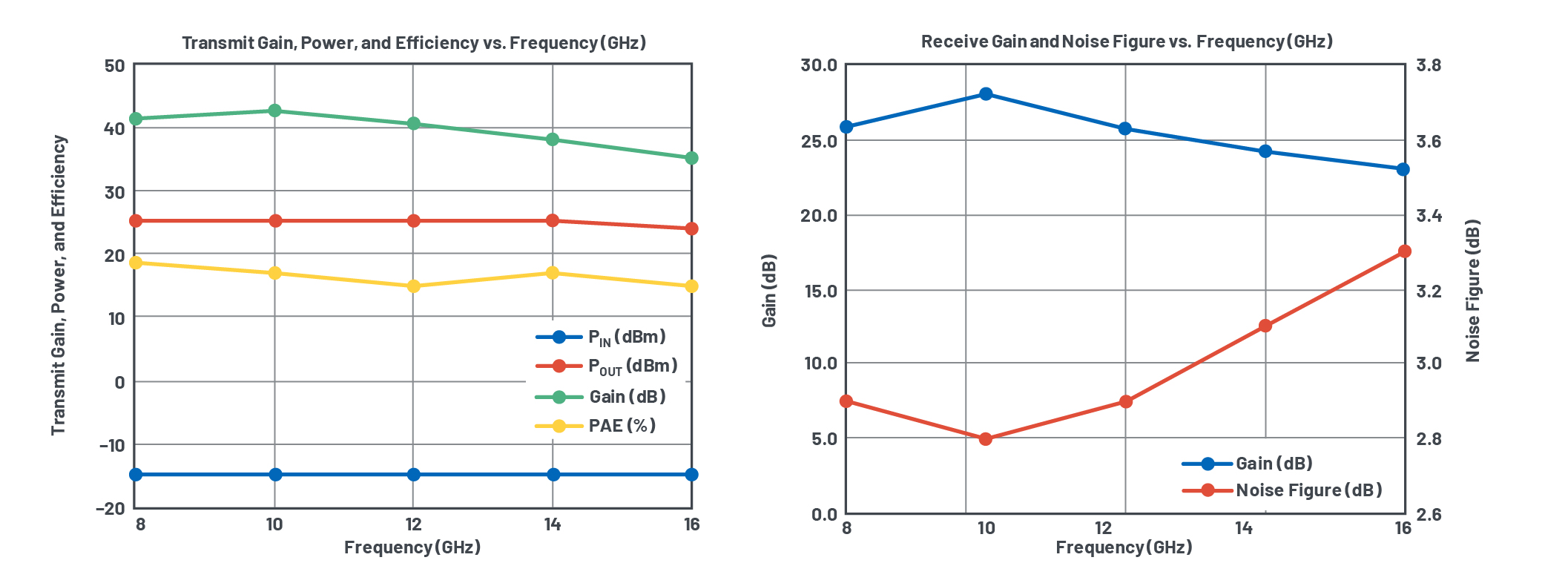

ADTR1107とADAR1000を組み合わせた回路全体では、どのような性能が得られるのでしょうか。それを示したものが図9です。この図は、8GHz~16GHzの周波数範囲における送信/受信モードの性能を表しています。送信モードでは、ゲインが約40dB、飽和電力が26dBmとなります。一方、受信モードでは、ノイズ指数が約2.9dB、ゲインが25dBです。

図9. ADTR1107とADAR1000を組み合わせた回路(シングルチャンネル)の送受信性能

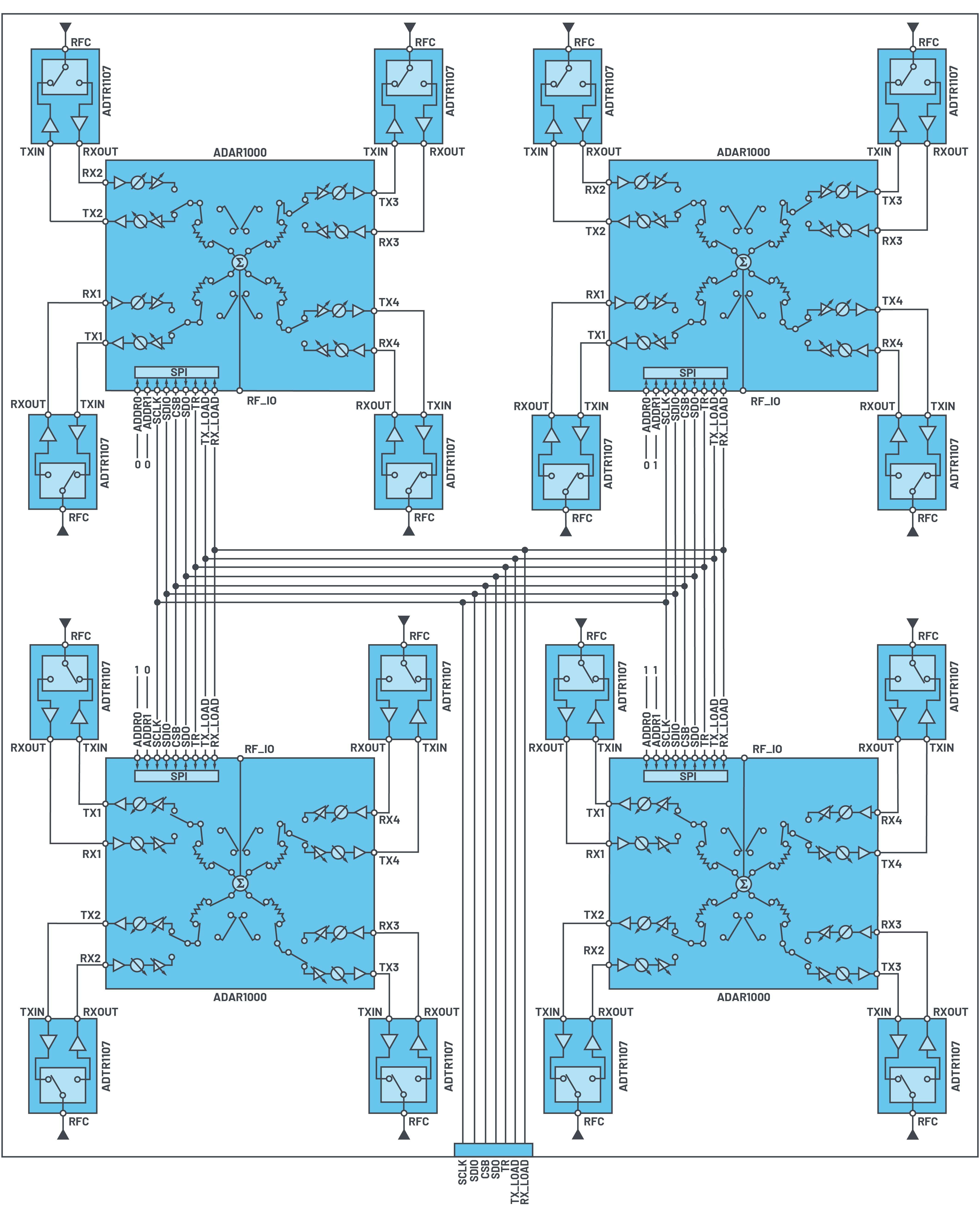

図10に示したのは、4個のADAR1000で16個のADTR1107を駆動する場合の回路例です。ご覧のように、シンプルな4線式のSPIによって、ADAR1000が備えるすべてのレジスタを制御できます。共通のシリアル・ラインによって最大4つのADAR1000のうちどれをSPI制御の対象にするかは、2つのアドレス・ピンによって決定します。また、TX_LOADピンとRX_LOADピンにより、同一アレイ内のすべてのコア・チップの同期がとられます。更に1本のTRピンによって、送信モードと受信モードを迅速にスイッチング制御することが可能です。

図10. 4個のADAR1000で16個のADTR1107を駆動する場合の回路例

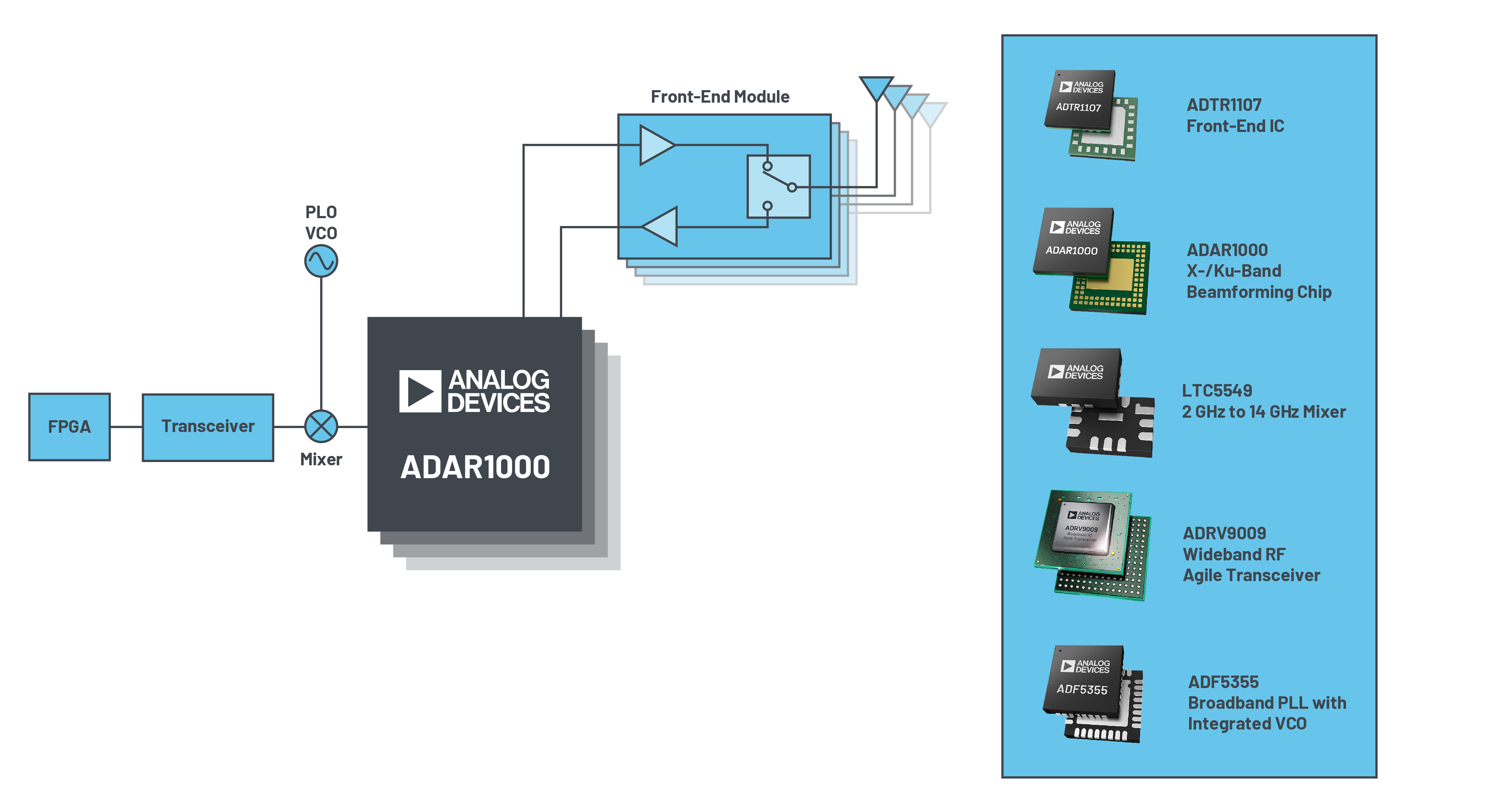

図11. フェーズド・アレイ・アンテナ向けの製品群

トランシーバーのチップセットと関連製品

集積度の高いRFトランシーバーICは、アンテナにおける実装密度の向上に貢献します。「ADRV9009」はそうしたICの一例です。同製品は、トランスミッタとレシーバーを2チャンネルずつ搭載しています。また、シンセサイザ機能とデジタル信号処理機能も集積されています。レシーバーは最先端のダイレクト・コンバージョン方式を採用しています。また、高いダイナミック・レンジ、広い帯域幅に対応し、エラー補正用の回路とデジタル・フィルタも備えています。ADRV9009は、補助機能用のA/DコンバータとD/Aコンバータも内蔵しています。更に、PAとRFフロント・エンドの制御に使用できるGPIO(General Purpose Input/Output)ピンも備えています。トランスミッタとレシーバーの信号パスに対しては、フラクショナルN方式の合成が可能な高性能のフェーズ・ロック・ループ(PLL)により、RF周波数信号が供給されます。通常動作を行っているとき以外の消費電力をより低減するために、包括的なパワーダウン・モードも用意されています。パッケージは、12mm×12mm、196ボールのCSP_BGAです。

アナログ・デバイセズは、フェーズド・アレイ・アンテナの設計に必要なあらゆる製品を提供しています。そのカバー範囲は、アンテナからビット・データまでのシグナル・チェーン全体を網羅しています(図11)。お客様が製品を市場に投入するまでの時間を短縮できるように、各ICはフェーズド・アレイ・アンテナ向けに最適化されています。IC技術の進化は、アンテナの設計に変化をもたらしました。それだけでなく、複数の業界にわたる変化を促進する原動力となっています。

アナログ・デバイセズのフェーズド・アレイ技術については、analog.com/jp/phasedarrayをご覧ください。

著者について

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}