高精度アンプのトポロジを適切に選択する方法

要約

通常、センサーの後段には高精度のシグナル・チェーンが配置されます。多くの場合、その最初のブロックとして使われるのはアンプ回路でしょう。その目的は、対象とする信号を増幅することです。その際には、信号の忠実度が維持されるよう注意を払わなければなりません。では、各種のセンサー・アプリケーションに対してはどのようなトポロジのアンプが適しているのでしょうか。本稿では、その選択方法について詳しく説明します。トポロジとしては、オペアンプ、差電圧アンプ、電流検出アンプ、計装アンプ、完全差動アンプの5つを取り上げることにします。

はじめに

長きにわたり、高精度のセンサーは多種多様な物理的事象の測定を行うためのものとして重要な役割を果たしてきました。現在でも、高精度の計測アプリケーションの種類と数は増え続けています。そのためのシステムは、干渉が存在するような状況においても、信号の忠実度を維持しながら、より振幅の小さい信号を感知できるように設計しなければなりません。当然のことながら、そのためには適切なセンサーを選択することが不可欠です。ただ、必要なのはそれだけではありません。センサーからA/Dコンバータ(ADC)までの完全な信号パスを慎重に設計した上で、アナログ信号をデジタル・データに変換する必要があります。では、各種のセンサー・アプリケーションに対して最適なトポロジのアンプを選択するにはどうすればよいのでしょうか。その選択に当たっては、システムの最終的な目標とアンプ回路の設計上の優先順位について検討する必要があります。

アンプのトポロジを選択する際に最初に行うべきこととは何なのでしょうか。通常、その答えは、センサーの出力信号(つまりアンプの入力信号)はシングルエンドなのか差動なのかを特定することです。各種のアンプの中にはシングルエンドの信号を受け入れるものもあれば、差動信号を受け入れるものもあります。また、どのトポロジが最適なのかは、アンプの出力としてシングルエンドの信号を使用したいのか差動信号を使用したいのかによっても異なります。

シングルエンドのオペアンプのトポロジ

オペアンプ(Operational Amplifier)は、非常に汎用性の高いデバイスです。様々な操作(Operation)に対応するよう構成可能なので、この名前で呼ばれています。アプリケーションの中には、シングルエンドの入力と出力を備えるアンプ回路が最適なものがあります。その場合、抵抗のペアによって適切なフィードバックを得るシンプルなオペアンプ回路を構成することになるでしょう。通常、シングルエンドのオペアンプ回路を使用して信号を高い精度で増幅するには、非反転アンプか反転アンプのトポロジを選択します。図1に示したどちらの回路でも、単一の帰還抵抗と単一のゲイン抵抗を使用しています。

図2に、シングルエンドの入力、シングルエンドの出力を備えるシンプルなアプリケーション回路の例を示します。図中の「TMP35」はアナログ・デバイセズの温度センサーICです。このICは、10mV/℃の感度で温度に比例する電圧を出力します。その出力信号は、シングルエンドの非反転アンプ回路に入力されます。この回路の伝達関数はVOUT = G×VINで表されます。ここで、Gは回路のクローズド・ループ・ゲインです。その値は、1+ (R2/R1) で決まります。例えば、0℃~50℃の温度を検出する場合、センサーのフルスケールの出力範囲は10mV/℃×50℃ =500mVになります。ここで、センサーの出力によってフルスケールの入力範囲が5VのADCを駆動するケースを考えます。その場合、ADCの入力ダイナミック・レンジをフルに活用するには、センサーの出力信号を10V/Vのゲインで増幅する必要があります。図2の非反転オペアンプであれば、G = 1 + (9kΩ/1kΩ) =10V/Vが得られます。

同相モード除去

アンプのトポロジを選択する際に検討すべき重要な指標としては、同相モード除去比(CMRR)が挙げられます。CMRRとは、差動入力電圧を増幅しつつ、コモン・モードの入力電圧を効果的に除去するアンプ回路の能力のことです。つまり、両方の入力に共通する電圧が出力に現れるのを防ぐ能力が重要になります。CMRRを指標として使用すれば、その能力を定量的に評価できます。CMRRが高いほど、出力の誤差は小さくなります。通常、CMRRは2つのゲインの比として表されます。具体的には、差動電圧のゲインADIFFとコモン・モード電圧のゲインACMの比をdB単位で表します(以下参照)。

周知のとおり、理想的なオペアンプでは2つの入力でバーチャル・ショート(仮想短絡)が成立します。つまり、一方の入力(+IN)に印加された信号電圧が、もう一方の入力(-IN)にも現れます。これがオペアンプのコモン・モード電圧です。最近のオペアンプ製品では、120dB~140dBのCMRRが得られます。それ以上の性能を達成している製品も存在します。そのようなレベルのCMRRにより、コモン・モード誤差が最小限に抑えられ、出力の精度が向上します。例えば、CMRRが140dBのオペアンプを使用する場合、オペアンプに入力されたコモン・モード電圧の0.00001%(0.1ppm)しか出力VOUTには現れません。最大入力電圧が5Vという低い電圧で動作するオペアンプの場合、その出力に現れる最大コモン・モード誤差はわずか0.5μVです。但し、入力電圧範囲が広い(例えば50V)オペアンプを使用すると、CMRR性能が同等であっても出力に5μVの誤差が現れることになります。これが問題になるかどうかは、システム設計の要件に依ります。コモン・モード誤差が特定のシステム設計の許容範囲を超える場合には、その誤差の影響を最小限に抑えるための回路を使用する必要があります。

図1(a)に示した非反転アンプでは、オペアンプの+INと-INの電圧は入力信号VINの電圧と等しくなります。そのため、信号の電圧が高くなると、オペアンプの入力ピンのコモン・モード電圧も高くなり、出力のコモン・モード誤差が増大します。そのような場合には、図1(b)の反転アンプの使用を検討してください。このトポロジでは、+INはグラウンドに接続されます。したがって-INの電圧もグラウンドのレベルになります。つまり、入力コモン・モード電圧は0Vです。そのため、入力コモン・モード電圧に伴う出力コモン・モード誤差は生じません。

差電圧アンプ

差動信号を出力するセンサーも少なくありません。その場合、測定される物理的な値は2つの電圧の差で表されます。差動出力のセンサーを使用すると1つのメリットが得られます。それは、両方の出力に含まれるセンサーからの電圧 (コモン・モード電圧)を、差動入力と高いCMRR性能を備えるアンプを使うことで除去できるというものです。

上記のとおり、システムで差動信号を使用すれば、センサーの出力に含まれるコモン・モード電圧を除去できます。ただ、得られるメリットはそれだけではありません。もう1つの重要なメリットは、CMRRが高ければ、電磁干渉 (EMI) に対してシステムが堅牢になることです。外部からのEMIは、差動信号の両方の導体にノイズをもたらします。ただ、このコモン・モード・ノイズは差電圧アンプによって除去されます。一方、もともと対象としている差動信号は保持/増幅されるので、優れたS/N比(Signal to Noise Ratio)が得られます。差動信号を使用すれば、更なるメリットがもたらされます。それは、振幅がシングルエンド信号の2倍になることです。それにより、S/N比が6dB向上することになります。低い電源電圧を使用するアプリケーションでは、電圧範囲が不十分であることから振幅の大きい信号を扱えません。そうしたアプリケーションでは、差動信号を使用することで出力信号の振幅が2倍になることから、差動入力のアンプが非常に役に立ちます。

差動信号を高い精度で増幅するための最も基本的なトポロジは、図3に示したような差電圧アンプです。差電圧アンプは、差動入力信号を受け取ります。そして、コモン・モード電圧VCMを除去しつつ、差動入力電圧VDIFFを増幅します。最終的には、2つの入力電圧の差に比例する形で増幅されたシングルエンドの信号が出力されます。この回路の伝達関数は、単純にVOUT = G×VDIFFとなります。ここで、VDIFFは(V2 - V1)です。Gはアンプ回路のゲインであり、その値はR2/R1になります。

シングルエンドのアンプとは異なり、図3の差電圧アンプのコモン・モード電圧は、オペアンプの入力である+INと-INの電圧とは異なります。回路への入力であるV1、V2に共通して含まれる電圧がコモン・モード電圧になります。この電圧は、2つの入力電圧の平均値として定義されます。つまり、VCM = (V2 - V1)/2となります。例えば、V1が5V、V2が3Vの場合、コモン・モード入力電圧は4V、差動電圧は2Vです。その2Vの差動信号が増幅されて出力されます。

先述したように、差動入力を備えるアンプのCMRRは、20×log10(ADIFF/ACM)で表されます。ここで、差動ゲインADIFFが大きくなり、コモン・モード電圧のゲインACMが小さくなったとします。その場合、差動ゲインに比例してCMRRが向上することに注目してください。これは大きなメリットです。なぜなら、より高いゲインとより高いCMRRの両方が同時に得られるからです。また、周波数が高くなると、CMRRが低下するという点にも注目する必要があります。このことから、対象とする信号の周波数において必要なCMRRが得られる差電圧アンプを選択することが重要になります。

抵抗の許容誤差、アンプの精度

差電圧アンプのCMRRは、図3のR2/R1とR2'/R1'がどの程度マッチングしているのかに大きく依存します。図3からわかるように、アンプ回路をディスクリート部品で構成した場合、それらの抵抗比をマッチさせるのは困難です。例えば、高精度のオペアンプ製品の場合、CMRRは140dB以上に達します。ここで、許容誤差が0.1%の抵抗を4つ使用してゲインが1の差電圧アンプを構成したとします。その場合、オペアンプが理想的なものであっても、差電圧アンプ回路としてはわずか54dBのCMRRしか達成できません1。54dBのCMRRは、分解能がほぼ9ビットのADCの精度に相当します。アプリケーションによっては、それで十分なこともあるでしょう。しかし、高い精度が求められるアプリケーションでは、はるかに優れたCMRRが必要になります。言い換えれば、抵抗比がマッチしていることが極めて重要になります。アンプ回路において高い精度を達成すべきもう1つの仕様は、ゲインの精度です。特定のゲインで信号を増幅するには、R2、R1、R1'、R2'として極めて正確な値の抵抗を選択する必要があります。誤差によって抵抗値が公称値からずれていると、(その誤差が許容誤差の範囲内だとしても)抵抗比のミスマッチが生じます。その結果、ゲインに誤差が生じます。また、すべての抵抗は温度によって値が変化します。そのため、温度に依存するゲイン・ドリフトの形で相応の誤差が発生します。ディスクリート構成のアンプ回路にはこのような問題があります。この問題は、非常に優れたマッチングが実現された抵抗ネットワーク製品を採用することで軽減できます。例えば、アナログ・デバイセズは抵抗比のマッチング精度が0.01%の「LT5400ファミリ」や同0.003%の「LT5401」などを提供しています。

上述したように、CMRRの低下、ゲイン誤差やゲイン・ドリフトの増大はアンプ回路の精度の低下につながります。最高レベルの精度を得るためには、これらすべての課題に加え、プリント基板の温度勾配、寄生容量といった問題にも対処しなければなりません。このような課題の解消に伴う負担を軽減するには、オペアンプと抵抗をモノリシックのIC上に集積した統合型の差電圧アンプ製品を選択するとよいでしょう。それにより、上記の問題は大幅に緩和されます。まず、各ICの抵抗の値は正確に一致するように製造されます。そのため、統合型の差電圧アンプのCMRRは非常に高く、ゲイン誤差が非常に小さく抑えられています。また、各抵抗は同じダイ上にあり、同じ材料で作られています。そのため、各抵抗の温度は近い値になり、同程度の温度係数を示すようになります。つまり、温度による抵抗値の変化も同等になります。結果として、抵抗比の誤差が小さくなり、ゲイン・ドリフトも最小限に抑えられます。多くの場合、統合型の差電圧アンプのCMRRは80dB~90dBまたはそれ以上に達します。ゲイン誤差は0.005%~0.02%、ゲイン・ドリフトはわずか1ppm/℃程度です。

ここで、図4に示す統合型の差電圧アンプ「LT1997-1」について考えてみましょう。このアンプでは、最小CMRRが100dB以上という非常に優れた性能が実現されています。これは、約17ビットの精度に相当します。標準的なゲイン誤差は±0.01%で、温度に対する標準的なゲイン・ドリフトは±0.2ppm/℃と極めて小さく抑えられています。また、値の異なる複数の抵抗を集積しているので、様々なゲインを実現できます。外付け部品を使用することなく、0.141V/V~80V/Vの範囲で24種のゲイン(増幅、減衰)を設定することが可能です。

差電圧アンプによる電流検出

差電圧アンプの非常に一般的な用途は高精度の電流検出です。そのための回路例を図5に示します。負荷には、非常に値の小さいシャント抵抗を介して電流が流れます。つまり、シャント抵抗の両端の電圧は負荷に流れる電流に比例します。その電流によって、シャント抵抗の両端には、それに比例する小さな差動電圧が生成されます。この小さな電圧は、ADCの入力電圧範囲全体を活用するために増幅されます。

負荷とグラウンドの間にシャント抵抗を配置する手法は、ロー・サイドの電流検出と呼ばれます。それに対し、図5の回路では、電源と負荷の間にシャント抵抗を配置することで電流を測定します。この手法は、ハイ・サイドの電流検出と呼ばれます。ハイ・サイドの電流検出にはいくつかの長所があります。その1つは、負荷がグラウンドに短絡している場合にそれを検出できることです。

ハイ・サイドの電流検出を使用する場合、2つの電圧について考慮する必要があります。1つは差動電圧VDIFFです。これは、V2とV1の間の信号電圧(シャント抵抗の両端の電圧)に相当します。もう1つは、コモン・モード電圧VCMです。これは、V2とV1の両方に共通して含まれています。この例では、オペアンプの+INには電圧VSUPPLY(つまりVLOAD + VDIFF)が印加されます。一方、オペアンプの-INにはVLOAD(つまりVSUPPLY - VDIFF)が印加されます。差電圧アンプは差動電圧を増幅しつつ、コモン・モード電圧を除去します。

ハイ・サイドの電流検出を使用する多くのアプリケーションでは、コモン・モード入力電圧が差動電圧の振幅よりはるかに大きくなります。実際、コモン・モード入力電圧はオペアンプの電源電圧よりはるかに高くなることが多く、数百Vに達するケースもあります。出力のコモン・モード誤差は入力のコモン・モード電圧に比例します。そのため、コモン・モード入力電圧が非常に高いシステムで正確なアナログ出力信号を得るためには、それに応じた高いCMRRが必要になります。差電圧アンプの重要な特性の1つは、電源電圧をはるかに超える高いコモン・モード電圧を除去する能力を備えていることです。これが可能なのは、各入力の抵抗ネットワークによって入力電圧V1とV2が減衰し、オペアンプの入力である+INと-INが指定された入力電圧の範囲内に収まるからです。例えば、アナログ・デバイセズの差電圧アンプ「AD8479」は、±15Vの電源電圧で動作させる場合でも、±600Vのコモン・モード入力電圧に対応することが可能です。

レベル・シフト

差電圧アンプにはもう1つ長所があります。それは、非常に簡単に出力電圧のレベル・シフトを実現できるというものです。それに向けて、多くの差電圧アンプにはリファレンス入力ピンが用意されています。そのピンに電圧を印加すると、入力間の差がゼロのときに、印加した電圧が出力されます。つまり、リファレンス電圧を中心とした信号がアンプから出力されるように設定可能です。例えば、図6に示した回路では、検出した信号が単一の電源電圧の1/2を中心として出力されます。

一方、図7の回路では、ADCのダイナミック・レンジを有効に活用するために、ADCの入力電圧範囲の中間点が振幅の中心になるよう設定しています。例えば、振幅が-2.5V~2.5Vに収まる信号があったとします。そして、この信号を入力電圧の範囲が0V~5VのADCに入力したいケースを考えます。その場合、その入力範囲の全体を活用するには、信号の中心がADCのフルスケール入力電圧範囲の1/2に位置するのが望ましいということになります。これを実現する簡単な方法が図7に示した回路です。あるいは、単一の電圧を両方のリファレンス入力ピンに印加することにより、出力の基準になる電圧を直接定めることも可能です。

電流検出アンプ

先述したように、モノリシック型の差電圧アンプは多くのアプリケーションで使用できます。また、最も一般的な用途としては、値の小さいシャント抵抗を使用した電流検出が挙げられます。実際、差電圧アンプを使用するのが最適な電流検出のアプリケーションは数多く存在します。ただ、アプリケーションによっては、電流検出アンプ(CSA:Current-sense Amplifier)として提供されるIC製品を選択した方が大きなメリットが得られることがあります。CSAでは、電流検出の用途に対して機能や仕様が最適化されているからです。通常、その種のICは差電圧アンプとは異なるアーキテクチャを採用しています。多くのCSAは、入力電圧を減衰させる入力抵抗ネットワークの代わりに高い電圧を入力可能なトランジスタを使用しています。それにより、大きく急速に変化するコモン・モード電圧を直接受け入れつつ、わずかな差動電流によってシャント抵抗に生じる電圧を正確に増幅します(図8)。

差電圧アンプにおいて、入力となる差動信号は抵抗ネットワークによってIC内部で減衰されます。その後、ゲインが適用されて元の入力レベルよりも高い所望の出力レベルまで増幅されます。一旦減衰された入力信号を元のレベルまで戻す過程では、アンプ本体のゲイン帯域幅積(GB積)の一部が消費されます。つまり、追加のゲインを得るためにいくらかの帯域幅が犠牲になります。それに対し、ほとんどのCSAが備える高電圧対応の入力トランジスタは入力信号を減衰させるわけではありません。したがって、信号の振幅を復元するためのゲインも不要です。つまり、CSAが内蔵するオペアンプは信号を増幅するためにより広い帯域幅を利用できるということになります。例えば、アナログ・デバイセズの差電圧アンプ「AD8206」の場合、小信号に対する-3dB帯域幅は100kHzです。一方、CSAである「AD8210」の帯域幅は450kHzに達します。このように、CSAでは広い帯域幅を確保できます。そのため、CSAは、高い周波数信号を扱うアプリケーションや高速に遷移する電流を検出するアプリケーションに最適です。

ほとんどの差電圧アンプのCMRRは80dB~100dB程度です。それに対し、CSAのCMRRは100dB~120dBあるいはそれ以上に達することがあります。上述したように、CSAでは広い帯域幅が得られます。これについてはトレードオフが存在します。CSAは、差電圧アンプと比較すると、非常に高いレベルの同相入力電圧は受け入れられません。なぜなら、CSAは減衰用の抵抗ネットワークを内蔵していないからです。とはいえ、CSAも80V~100V程度のコモン・モード電圧に対応できます。

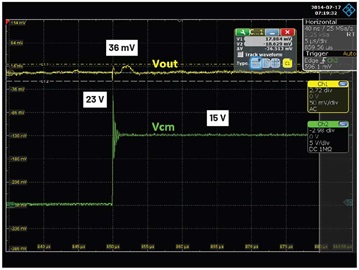

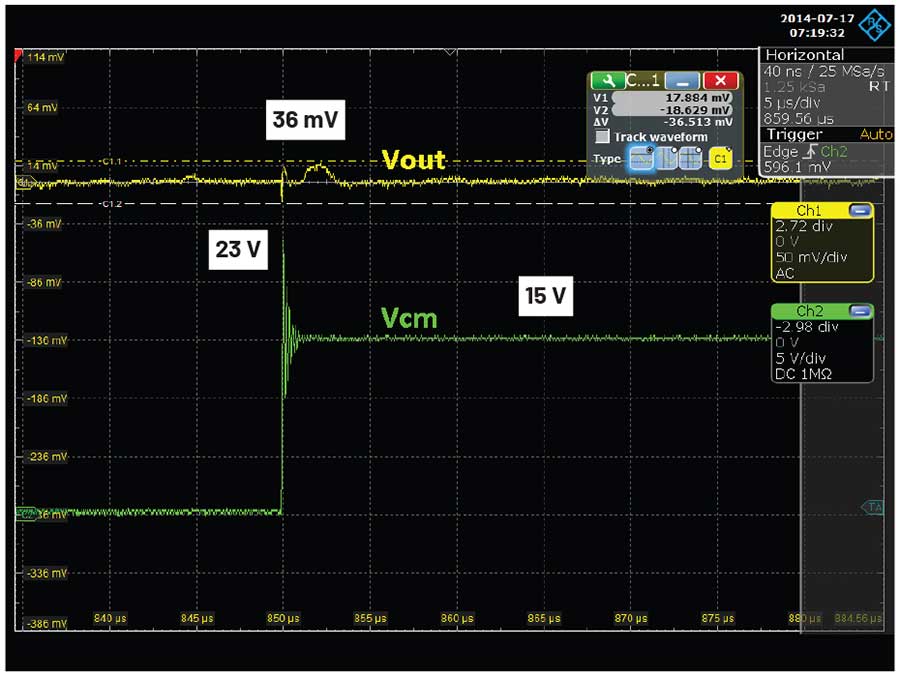

多くの場合、CSAは大きなスイッチング電流の測定に使用されます。ここでは、負荷のハイ・サイドでスイッチング電流 (つまり、シャント抵抗に生じる電位差) を測定するケースを考えます。その場合、シャント抵抗のコモン・モード電圧は、グラウンドと電源電圧の間で急激に変化することがあります。それが原因となって、アンプの入力部には大きなトランジェントが生じる可能性があります。コモン・モード電圧に起因するトランジェントは、信号の振幅よりも大きくなることが少なくありません。理想的に言えば、アンプは、検出された差動電圧だけを反映した出力を生成するべきです。しかし、実際には出力にコモン・モードのステップ応答が現れる可能性があります。CSAは、急速に変化するコモン・モード電圧(ステップ状の信号)が原因で生じるコモン・モードの過渡的なスパイクを除去する性能に優れています。そのため、振幅が急激に変化する電圧(電流量を表す)の検出に最適です。

図9は、アナログ・デバイセズのCSA「AD8418」におけるステップ応答とトランジェント除去の様子を表したものです。コモン・モード入力電圧は15Vで、アンプはコモン・モード電圧を50%以上もオーバーシュートする入力トランジェントを検出しています。ただ、コモン・モードのステップ応答は、短時間にわたるわずか36mVの出力の変動としてしか現れていません。

ここで、コモン・モード電圧の高速な変動が発生する例を挙げましょう。一般的な3相モータ用の制御システムにおいて相電流を測定する際には、そのような変動が生じます。その種の制御システムでは、コントローラによってインバータ段にPWM(Pulse Width Modulation)信号が送信されます(図10)。それを受けたインバータ段がモータの各レッグを駆動します。シャント抵抗は、モータと直列に配置されます。同抵抗の両端に瞬間的に流れる電流の測定値は、差動電圧としてアンプに引き渡されます。その出力となるフィードバック信号を受けて、コントローラは各信号の位相を決定します。各PWM信号のパルスに伴い、シャント抵抗のコモン・モード電圧は、電源であるV-とV+の間の全範囲にわたって急速に変化します。これらの高速なPWMのステップ信号に対応するために必要なアンプとはどのようなものでしょうか。それは、帯域幅が広く、立ち上がりエッジと立下がりエッジに伴う大きなトランジェントによって生じるオーバーシュートを除去可能なアンプです。アナログ・デバイセズの「AD8411A」は、最大70Vのコモン・モード電圧範囲に対応します。その入力部には高精度の抵抗分割ネットワークが集積されています。2.7MHzという広い帯域幅を備えていることが特徴の1つです。また、高速にスイッチングする入力信号の影響を軽減し、高い出力精度を実現するデグリッチ回路を備えています。これらの特徴を備えていることから、AD8411Aは3相モータ用の制御システムのアプリケーションに最適です。

計装アンプ

ここまでに、差動入力型のトポロジを採用したアンプの例として差電圧アンプと電流検出アンプを取り上げました。これらのアンプは、非常に高いコモン・モード電圧が存在する様々なアプリケーションで差動信号を増幅したい場合に適しています。ノイズを含む高いコモン・モード電圧の中には、非常に小さいにもかかわらず非常に重要な信号が含まれているはずです。そうした信号を非常に高い精度で増幅する必要があるアプリケーションでは、精度の高いアンプを使用することが不可欠です。そのような要件の厳しいアプリケーション向けに特別に設計されているのが計装アンプ(in-amp)です。

計装アンプと差電圧アンプの主な違いはどのような点にあるのでしょうか。まず、差電圧アンプには、入力インピーダンスが比較的低いという潜在的な制約があります。また、アンプの各入力のインピーダンスが等しくないことも制約の1つです。これらが問題になるケースについて確認するために、ここでは様々なセンサーで使用されるホイートストン・ブリッジを取り上げることにします。図11の回路から得られる差動信号(V2 - V1)を増幅する方法について考えてみましょう。ブリッジ回路では、出力インピーダンスがかなり高くなります。差電圧アンプを使用する場合、その出力によって比較的低い入力インピーダンスを駆動しなければなりません。これが1つ目の懸念です。例えば、ブリッジ回路の出力インピーダンスが4kΩ、差電圧アンプの入力インピーダンスが200kΩであるとします。その場合、トランスデューサの信号の2%が出力インピーダンスで失われ、正確な測定が行えなくなります。また、差電圧アンプの入力インピーダンスの値が等しくないことから、もう1つの懸念が生じます。それにより、ブリッジの2つのレッグにおける電圧降下に差が生じ、差動電圧に誤差が生じる可能性があるということです。これらの問題を解決するには、入力インピーダンスがはるかに高く、ブリッジの出力に対してバランスのとれた負荷を与え、優れたCMRRを発揮するアンプを使用しなければなりません。これらの要件が、そのまま計装アンプの主な特徴になります。

図12(a)に示したのは、3個のオペアンプから成る典型的な計装アンプの例です。ご覧のように、オペアンプA1、A2が1段目(プリアンプ段とも呼ばれます)を構成しています。そして、オペアンプA3が2段目(減算器と呼ばれます)として使用されています。この減算器は、ここまでに詳しく説明した差電圧アンプだと見なすことができます。オペアンプA1、A2は、バランスのとれた非常に高い入力インピーダンスを提供します。また、差動入力電圧は増幅し、コモン・モード電圧は増幅することなく通過させます。その後段の減算器A3は、コモン・モード電圧を除去し、増幅された差動電圧を出力します。このトポロジにはもう1つの特徴があります。それは、単一の外付け抵抗RGによってゲインを設定できるというものです。つまり、ディスクリート抵抗の比をマッチさせるための配慮が必要ありません。このトポロジは、非常に小さい信号を増幅し、高いコモン・モード電圧を除去したい用途に最適です。計装アンプの伝達関数は、VOUT = G×VDIFF + VREFです。ここで、VDIFFは(V+IN - V-IN)、Gは計装アンプのゲイン、VREFは出力電圧をレベル・シフトするためにREFピンに印加される電圧です。

差電圧アンプと同様に、図12(b)のように表される統合型の製品も提供されています。つまり、ダイ上に正確にマッチングされた抵抗器を集積したモノリシック型の計装アンプICが提供されているということです。集積型の差電圧アンプのCMRRは90dB~100dBです。それに対し、集積型の多くの計装アンプは130dB~140dBまたはそれ以上のCMRRを達成しています。先ほど例にとったホイートストン・ブリッジのソース抵抗は4kΩでした。ここで、入力抵抗が200GΩの計装アンプ「AD8422」を使用したとすると、ソース信号の損失は0.000002%(0.02ppm)まで抑えられます。また、計装アンプでは入力バイアス電流が差電圧アンプよりもはるかに少なくなる傾向があります。そのため、入力バイアス電流がソース抵抗を流れる際に生成される電圧誤差を小さく抑えられます。

完全差動アンプ

ここまで、シングルエンド入力と差動入力のトポロジについて解説してきましたが、それらはすべてシングルエンドの出力を備えていました。ただ、高い精度で信号を扱う必要がある場合、アンプ回路の出力としても差動信号が求められることがあります。差動入力と差動出力を備えるアンプは、完全差動アンプ(FDA:Fully Differential Amplifier)と呼ばれます。またはdiff-ampと呼ばれることもあります。統合型のFDAは、シングルエンドの入力信号も差動の入力信号も増幅できます。そのため、広範な用途で使用可能です。FDAは、入力コモン・モード電圧の除去、差動入力電圧の増幅、差動出力信号の供給という面で優れています。出力コモン・モード電圧(VOCM)は、リファレンス入力ピン(VOCMピン)に所望の値の電圧を印加することによって決まります。

FDAの非常に一般的な用途は、高性能のADCの差動入力を駆動することです。つまり、FDAはADCの入力電圧範囲を有効に活用するために、小さな入力信号を増幅したり、大きな入力信号を減衰したりするために使用されます。図13は、アナログ・デバイセズのFDA「AD8475」の活用例です。この例では、同FDAがセンサーから差動信号を受け取り、後段のADCの差動入力を駆動します。ADCとしては、分解能が24ビットで変換レートが250kSPSのシグマ・デルタ(ΣΔ)型ADC「AD7176-2」を使用しています。この例の場合、アンプのVOCMピンはADCのリファレンス出力によって駆動します。それにより、コモン・モード電圧をADCの入力ダイナミック・レンジに対して最適なレベルに設定します。

FDAの非常に一般的な用途はもう1つあります。それは、シングルエンドの入力信号を差動の出力信号に変換するというものです。多くのセンサーは、高い精度でシングルエンドの信号を出力します。それを増幅/減衰した信号によってADCの差動入力を駆動する場合には、シングルエンドの信号を差動信号に変換するのが望ましいということになります。FDAは、この用途に最適なトポロジです。図14に示した回路では、アンプの1つの入力をグラウンドに接続し、もう1つの入力をシングルエンドの信号で駆動しています。つまり、ADCの差動入力に対応するようシグナル・コンディショニングを行っています。また、差動出力に変換することにより、信号の振幅が2倍(6dB)になるというメリットも得られます。その結果、S/N比が高くなり、デジタル化されたデータの有効分解能が向上します。

まとめ

高精度のシグナル・コンディショニング回路に最適なアンプのトポロジを選択する際には、多くの事柄について検討する必要があります。優先度の高い検討事項としては、信号の種類(シングルエンドか差動か)、信号源(センサーなど)のインピーダンス、必要なCMRR、ゲインの精度などが挙げられます。本稿では、様々なトポロジを紹介しましたが、アナログ・デバイセズは各トポロジに対応するアンプ製品を提供しています。業界を牽引する多種多様な製品が用意されているので、どのようなアプリケーションを設計する場合でも、必ず最適なものが見つかるはずです。その結果、最適なシステム性能を実現することが可能になります。

参考資料

1 Ramón Pallás-Areny、John G. Webster.「Common Mode Rejection Ratio in Differential Amplifiers(差動アンプのCMRR)」IEEE Transactions on Instrumentation and Measurement、Vol. 40、 No. 4、1991年8月

Paul Blanchard、Anna Fe Briones「AN-1308:電流検出アンプの同相ステップ応答」Analog Devices、2015年10月

Kristina Fortunado「AN-1321: Common-Mode Transients in Current Sense Applications(AN-1321:電流検出アプリケーションのコモンモード・トランジェント)」Analog Devices、2014年10月

Harry Holt「差電圧アンプ回路の“ 落とし穴”」Analog Dialogue、Vol. 48、No. 1、2014年2月.

Walt Jung「Op Amp Applications Handbook(オペアンプ・アプリケーションのハンドブック)」Analog Devices、2005年

Walt Kester「MT-068: Difference and Current Sense Amplifiers( 差電圧アンプと電流検出アンプ)」AnalogDevices、2008年10月

Walt Kester「MT-074: Differential Drivers for Precision ADCs(高精度A/Dコンバータ用の差動ドライバ)」Analog Devices、2008年10月

Charles Kitchin、Lew Counts「A Designer's Guide to Instrumentation Amplifiers, third edition(計装アンプの設計ガイド 第3版)」Analog Devices、2006年

Henri Sino「ハイサイド電流の検出 差動アンプ対電流検出アンプ」Analog Dialogue、Vol. 42、No. 1、2008年1月

著者について

この記事に関して

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}