41%のPAEで3.6Vから+27dBmを出力する1.9GHzのDECTパワーアンプ

要約

MAX2242は、内蔵バイアス回路、ロジックレベルのシャットダウン、およびパワーディテクタを備えた、超低コストのシリコンバイポーラパワーアンプ(PA)です。1.9GHzの周波数帯域でのDECTアプリケーション用に最適化すると、MAX2242 PAは41%のPAEで3.6Vから+27dBmの出力電力を供給し、電力利得は27dBとなります。4.5Vの電源で動作させると、出力電力は+29dBmまで増大することができます。

MAX2242は、バイアス回路、ロジックレベルのシャットダウン、及びパワーディテクタを内蔵した、超低コストのシリコンバイポーラパワーアンプ(PA)です。MAX2242 PAは、1.5mm × 2.0mmの超小型UCSP™パッケージで提供されています。1.9GHzの周波数帯域でのDECTアプリケーション用に最適化すると、このPAは41%のPAEで3.6Vから+27dBmの出力電力を供給し、電力利得は27dBとなります。4.5Vの電源で動作させると、出力電力は+29dBmまで増大することができます。電源電圧と周波数の変動に対するPAの性能については、表1を参照してください。PAの高調波抑制対電源電圧の概要については、表2を参照してください。PAの出力電力対入力電力と電源電圧の変動の概要については、図1を参照してください。

表1. MAX2242の出力電力と消費電流

(入力電力 = 0dBm)

| 1880MHz | 1905MHz | 1930MHz | ||||

| VCC (V) | POUT (dBm) | ICC (mA) | POUT (dBm) | ICC (mA) | POUT (dBm) | ICC (mA) |

| 3.24 | 26.1 | 325 | 26.3 | 324 | 26.4 | 322 |

| 3.60 | 26.8 | 352 | 27.0 | 350 | 27.1 | 348 |

| 4.50 | 28.9 | 443 | 29.0 | 442 | 29.1 | 437 |

表2. MAX2242の高調波抑制対電源電圧

(f = 1905MHz、入力電力 = 0dBm)

| VCC (V) | 2x (dBc) | 3x (dBc) | 4x (dBc) | 5x (dBc) | 6x (dBc) |

| 3.24 | -37.0 | -52.0 | -54.3 | -43.2 | -47.0 |

| 3.60 | -36.8 | -52.0 | -55.3 | -42.7 | -47.2 |

| 4.50 | -36.2 | -52.7 | -57.7 | -42.2 | -59.2 |

MAX2242 1.9GHz DECTの出力電力対入力電力

図1. MAX2242 1.9GHz DECTの出力電力対入力電力

MAX2242 PAは、3段のアンプ設計を採用しており、最適性能を得るには、入力、中間段、及び出力のマッチング部品を必要とします。必要なマッチング部品の回路図については、図2を参照してください。PAの入力は内部でバイアスがかけられているため、デバイスの入力端でDCブロックが必要です。2素子LCマッチングが、1.9GHz用での入力リターンロスを最適化します。段間マッチングを最適化するため、VCC1とVCC2上に少量の直列インダクタンスが必要です。VCC1では、これは、直列の1.8nHインダクタと短い伝送ラインで達成できます。VCC2では、短い伝送ラインで達成することができます。出力段には、DCバイアス用にプルアップインダクタが必要です。負荷に合わせて出力電力を最適化するため、直列LとシャントCが必要です。直列L素子は、短い伝送ラインと、約0.5nHのインダクタンスを示す直列0Ωで達成されます。段間マッチングと出力マッチングの正確なインダクタンス量は、ボードレイアウト、ボード厚、及び誘電率によって異なります。部品の値については図2を参照してください。また、VCC1、VCC2バイパスコンデンサの配置、及びMAX2242 EVキット上のトレースのインダクタンス量を設定する出力シャントコンデンサの配置については、図3を参照してください。

MAX2242 EVキットをご利用の際はご購入ください。また、MAX2242 EVキット用のレイアウトファイルはご請求に応じて提供しております。

図2. MAX2242 1.9GHz DECTの回路図

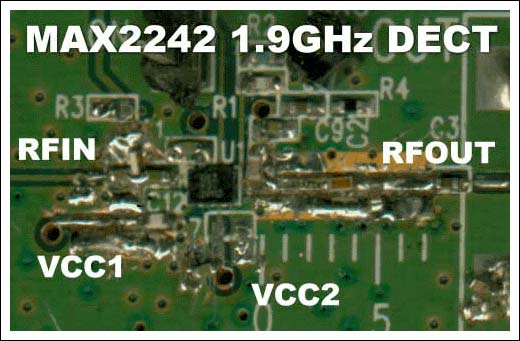

図3. MAX2242 1.9GHz DECT EVキットの部品配置