MAX5977の重要な部品の配置と配線のガイドライン

要約

このアプリケーションノートは、高性能、ホットスワップ、電子ヒューズ、ハイサイド電流検出コントローラのMAX5977の標準設計における最も重要な部品およびトレースの配置と配線のガイドラインを示します。

はじめに

MAX5977Aは、汎用、高性能ホットスワップコントローラで、電子ヒューズ、およびハイサイド電流検出出力を備えています。MAX5977の完全な性能を実現する上で、適切な部品の配置と配線が非常に重要です。ここでは、特定のレイアウト/配置技法の利点と欠点について解説します。

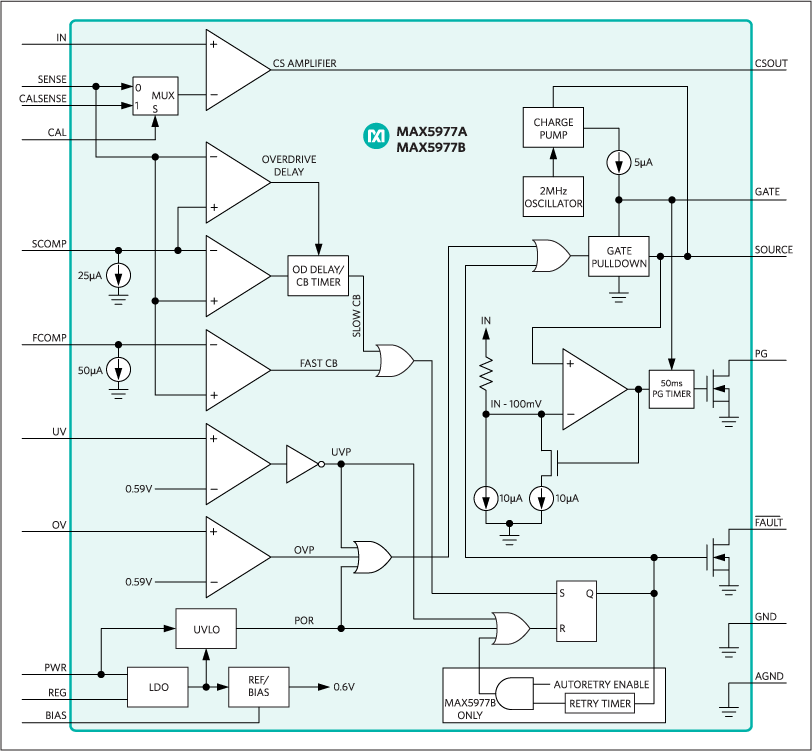

MAX5977のアプリケーション図と動作

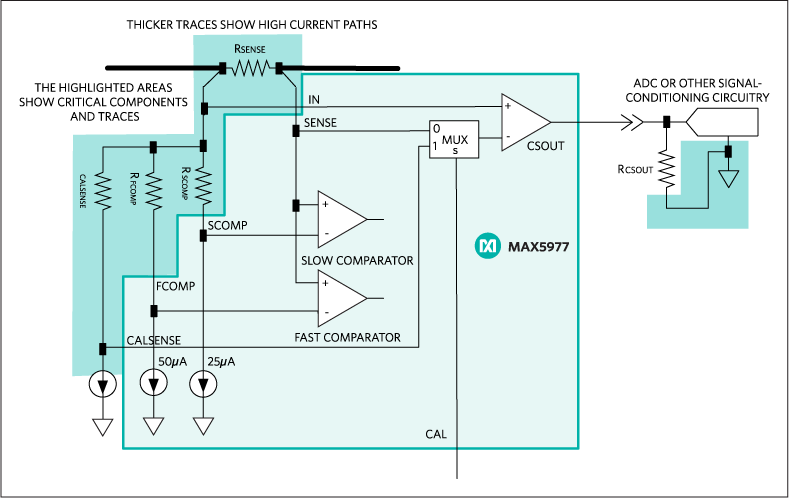

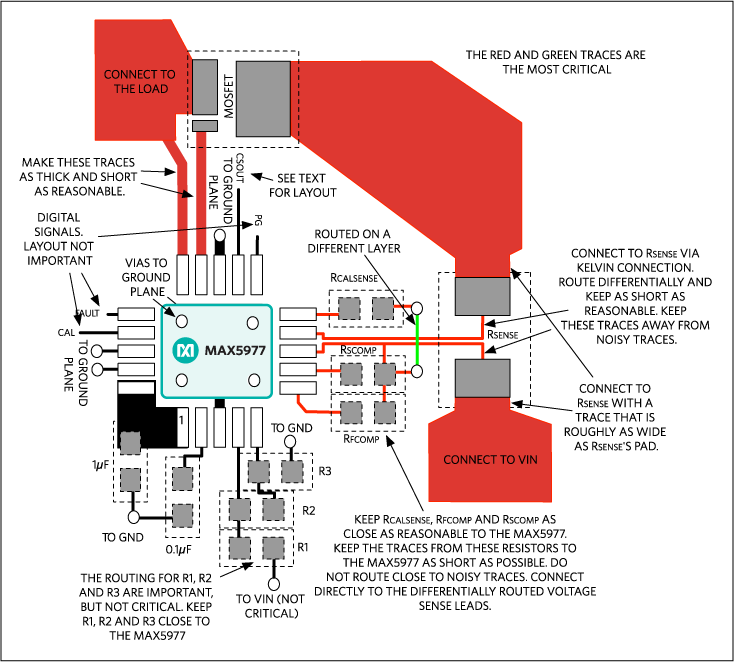

MAX5977の動作とレイアウトの要件をより良く理解するため、アプリケーション図で重要なノードを確認してください。図1を参照してください。図に示されていないトレースには、標準レイアウト技法を使用することができます。

図1. MAX5977の回路の重要な部品およびトレースを示すアプリケーション図

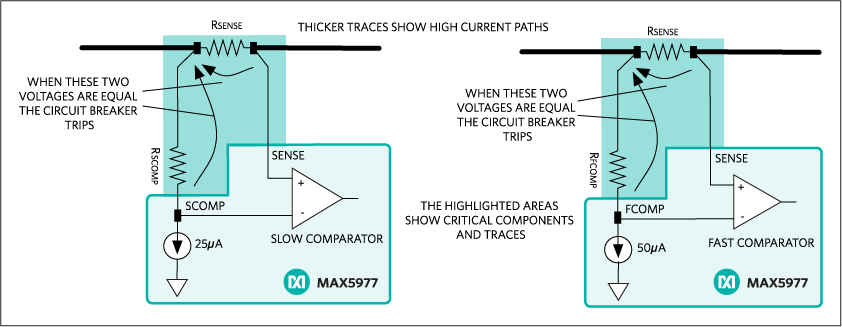

回路ブレーカ機能は、RSENSE両端の電圧をRSCOMPおよびRFCOMP両端の電圧と比較します。図2を参照してください。RSENSE両端の電圧がRSCOMPまたはRFCOMPいずれかの両端の電圧を超えた場合、回路ブレーカが作動します。比較される電圧は、通常は25mV~100mVの範囲です。部品の配置とレイアウトが不適切な場合、ある種の障害状態において誤作動や作動不良につながる可能性があります。

図2. MAX5977の高速および低速回路ブレーカ機能の簡略アプリケーション図

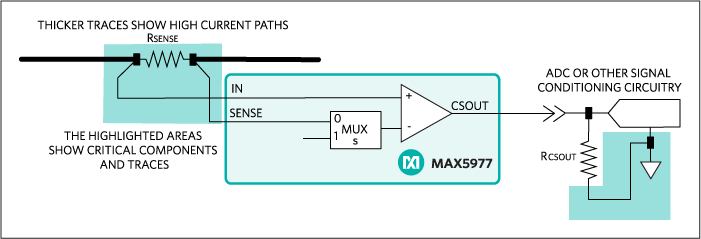

MAX5977の電流レポート機能は、INおよびSENSE端子を介してRSENSE両端の電圧を検出します。図3を参照してください。内部的には、2500µSの利得を備えたトランスインピーダンスアンプがCSOUT端子に電流を出力します。外付けの抵抗RCSOUTはこの電流を電圧に変換し、RSENSEとともに回路全体の利得を設定します。回路ブレーカ機能と同様に、RSENSE両端で測定される電圧は非常に小さく、通常は数mV~50mVの範囲です。図3に示す部品の配置または配線が不適切な場合、RCSOUT両端の精度が低下します。

図3. MAX5977の電流レポート機能の簡略アプリケーション図

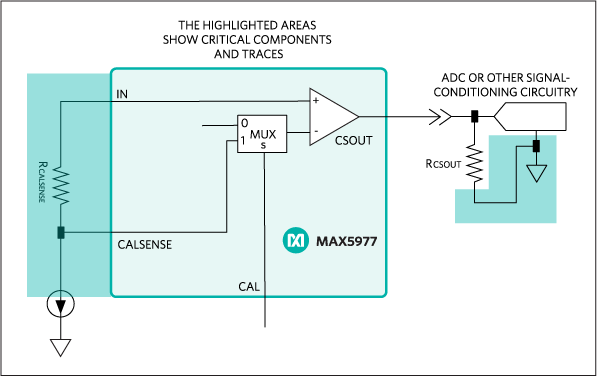

CALSENSE端子によって、電流レポート機能のシングルポイント較正が可能です。図4を参照してください。外部電流ソースがRCALSENSE両端に既知の電圧を生成します。この較正電圧は、CAL端子を介して外部ADCに多重化されます。較正電圧は、通常は25mV~50mVの範囲です。配置と配線が不適切な場合、較正中に誤差が発生し、以後の全測定に悪影響を及ぼします。

図4. 電流レポート機能のシングルポイント較正用回路を示す簡略アプリケーション図

レイアウトのガイドライン

この項では、適切な配置および配線の大まかなガイドラインを示します。これらのガイドラインは厳格なルールではなく、MAX5977の性能を最大限に高めるために役立つ枠組みを提供するものです。適切な配置と配線を使用することは常に良い考えですが、より高いRSENSEの値を使用する回路は、誤差の影響を受けにくくなります。そのため、RSENSEの値が高い回路は、性能への悪影響なしにある程度の自由な変更が可能です。逆に、より低いRSENSEの値を使用する場合は、示されたガイドラインをより厳密に遵守する必要があります。

RSENSEの接続

- RSENSEに接続する負荷電流搬送用トレースは、RSENSEの側面ではなく端面に接続してください。これらのトレースの幅は、接続点のパッドの幅とほぼ同じにしてください。図5を参照してください。これらのトレースを適切に接続することによって、不均一な電流密度を防止することができるため、パッド両端の電圧差がなくなります。

図5. 大電流トレースは、RSENSEの側面ではなく端面に接続する。トレース幅は、接続点におけるパッドの幅とほぼ等しくする。

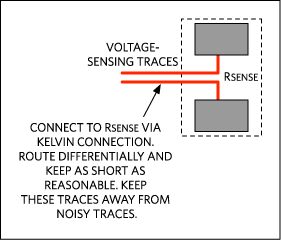

- より低い抵抗値を使用する場合、4端子(または6端子)の検出抵抗が推奨されます。2端子の検出抵抗を使用する場合は、ケルビン接続によって電圧検出リードをRSENSEに接続してください。図6を参照してください。

図6. 2端子のRSENSEへのケルビン接続を示す図

- RSENSEに接続する電圧検出リードは、できる限り差動で配線し、できる限り短くしてください。

- 電圧検出リードは、ノイズの多いトレースから遠ざけてください。

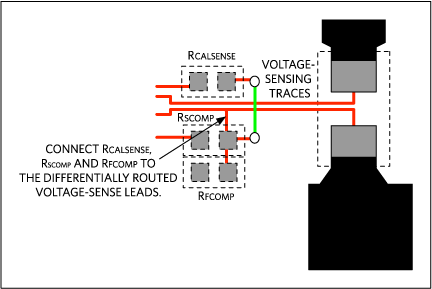

RCALSENSE、RSCOMP、およびRFCOMP

- RCALSENSE (使用する場合)、RSCOMP、およびRFCOMPは、できる限りMAX5977の近くに配置してください。これらの抵抗からMAX5977へのトレースは、できる限り短くしてください。

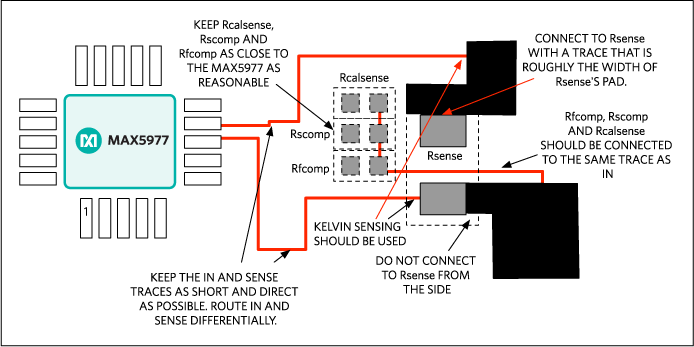

- RCALSENSE、RSCOMP、およびRFCOMPからRSENSEへの接続は、差動で配線されたケルビン検出トレースに直接行ってください。図7を参照してください。

図7. RCALSENSE、RSCOMP、およびRFCOMPは、差動で配線された電圧検出リードに接続する。

- RCALSENSE、RSCOMP、およびRFCOMP、およびそれらに関連するトレースは、ノイズの多いトレースから遠ざけてください。

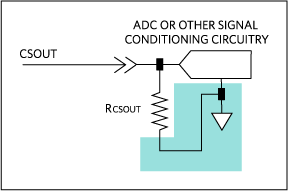

RCSOUT

- 重大性は下がりますが、RCSOUTの配置およびグランド処理も重要です。RCSOUTは、通常はADCまたはその他の信号調整回路に接続されます(この例ではADCを使用します)。このADCは、MAX5977から遠く離れた位置や、場合によっては別の基板上に配置されている場合もあります。MAX5977とADC間にグランドの差があると、測定精度が低下します。そのため、RCSOUTの配置およびグランドはADCに隣接させることが重要です。図8を参照してください。

図8. RCSOUTのグランド接続は、ADCまたは信号調整回路に直結する位置で行う。これは、ADCまたは信号調整回路がMAX5977とは別の基板上にある場合、特に重要となる。

- CSOUTのトレースは、ノイズの多いトレースから遠ざけてください。

グランド処理

- MAX5977には、AGNDとGNDの2つの異なるグランドがあります。AGND (ピン3およびエクスポーズドパッド)は、MAX5977内部の高精度信号に接続されます。FCOMPおよびSCOMPに接続される電流ソースは、図9に示すように、いずれも他の高精度信号とともにAGNDにグランド接続されます。GND (ピン13)は、同じ図9に示すデジタル信号およびゲートプルダウンドライバに使用されます。

図9. MAX5977のブロック図。AGND (ピン3およびエクスポーズドパッド)は、高精度または低ノイズ回路に使用される。GND (ピン13)は、デジタル回路およびゲートプルダウンに使用される。

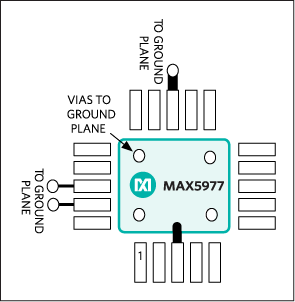

- 図10に示すように、ピン3とエクスポーズドパッド(いずれもAGND)を、短いトレースを介して相互に接続してください。1つまたはそれ以上のビアを使用して、エクスポーズドパッドをグランドプレーンに接続してください。MAX5977の消費電力は100mWより大幅に低いことに注意してください。放熱のために多数のビアをエクスポーズドパッドに接続する必要はありません。

- GND (ピン13)は、図10に示すように専用のビアによってグランドプレーンに直接接続してください。

図10. ピン3 (AGND)はエクスポーズドパッドに直接接続する。エクスポーズドパッドは1つのビアまたは複数のビアによってグランドプレーンに接続する。GND端子(ピン13)は1つのビアによってグランドプレーンに接続する。

GATEおよびSOURCE

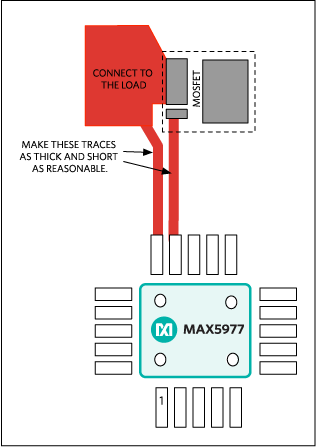

- 過電流事象が発生すると、MAX5977はFETのゲートとソースを短絡させることによって外部MOSFETをオフにします。ハード短絡の場合、外部FETをできる限り素早くオフにすることが重要です。FETを素早くオフにすることによって、ハード短絡がバスに伝播するのを防ぐことができます。MAX5977は、非常に高速な200ns (typ)の応答時間と、500mAの短絡電流を備えています。この大短絡電流は、外部FETのゲート-ソース間容量(CGS)を素早く放電するために必要です。FETのターンオフ時間をできる限り短くするため、GATEおよびSOURCEを適切に配線してください。

- 寄生インダクタンスを最小限に抑えるため、GATEおよびSOURCE端子と外部FETを接続するトレースは無理のない範囲で短くしてください。同じようにインダクタンスを最小限に抑え、500mAの放電電流に対応するため、より厚いトレースを使用してください。図11を参照してください。

図11. 短く太いトレースでGATE端子およびSOURCE端子を外部FETに接続する。これによってトレースのインダクタンスが最小限に抑えられ、短いターンオフ時間が維持される。

すべてをまとめた例

図12は、上記のすべてのアドバイスをその他のガイドラインとともに取り入れたレイアウトの1つの例を示します。

図12. MAX5977の配置と配線のガイドラインのまとめ

不適切な配線の影響

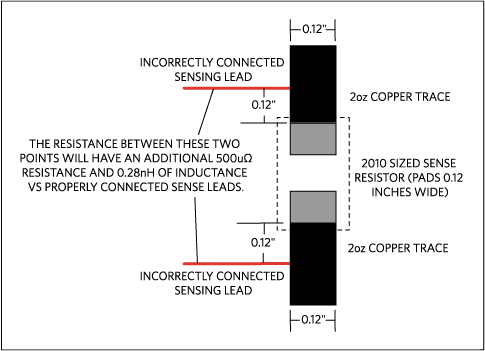

図13で、RSENSEは2010サイズの2.5mΩ抵抗で、パッド幅は0.12インチだとします。また、検出ポイントは検出抵抗のパッドから0.12インチ離れた不適切な位置で接続されているとします。

図13. 検出抵抗への不適切な接続は大幅な誤差につながる可能性がある。

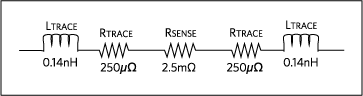

検出ポイントとRSENSE間の個々の0.12インチ × 0.12インチのトレースによって、およそ250µΩの抵抗と0.14nHのインダクタンスが追加されます(注1)。図14は、その等価回路を示します。

図14. 図13に示した不適切に接続されたRSENSEの等価回路

電流レポートおよび低速トリップ回路ブレーカはフィルタを備えているため、追加されたインダクタンスの影響を受けることはありません。しかし、追加された500µΩの抵抗は、2.5mΩの検出抵抗に関して+20%の誤差を発生させます。参考として、データシートに記載された電流レポートの誤差は、ワーストケースで±4.1%です(注2)。このわずかな配線の誤りによって、全体的な誤差が約±4%から+16%/+24%に増大します。完全に4倍~6倍の誤差の増大です。

高速トリップコンパレータにはフィルタがないため、追加された抵抗とインダクタンスの両方が影響します。RSENSEを通る10A/µsの電流過渡によって、20%の抵抗誤差に追加される形で2.8mVの誤差が発生します。スルーレートが高速であるほど、それに比例して誤差が大きくなります。

低速および高速回路ブレーカのスレッショルドに誤差が生じると、MAX5977が下流の回路を不要なタイミングでオフにする可能性があります。これらの誤作動のひどさによっては、設計が使用に適さないことになります。

不適切な配置と配線の例

図15は、不適切な配置と配線の例を示します。

図15. MAX5977の回路に対する不適切な配置と配線の例

注

注1

- トレースとグランドプレーン間の間隔は5 milと仮定します。

- 簡素化のため、パッド自体によって生じる誤差は無視しています。

- 2mV < (VIN - VSENSE) < 25mV (-40°C to +85°C),

- %誤差 = (ICSOUT - (VIN - VSENSE) × 0.0025)/(25mV × 0.0025)