資料ライブラリ

アプリケーション・ノート使用上の注意

本アプリケーションノートの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、リビジョンが古い場合があります。最新の内容については、必ず最新の英語版をご参照ください。

なお、日本語版のアプリケーションノートは基本的に「Rev.0」(リビジョン0)で作成されています。

AN-86:研究所標準グレードのドリフト0.1ppm/°C 20ビットDAC

1ppmの専用デジタル変換技術

はじめに

近年、高精度、計装グレードのD/A変換は長足の進歩を遂げました。10 年前、12ビットのD/Aコンバータ(DAC)は、高級なデバイスと考えられていました。現在では16ビットDACが市販され、システム設計への普及が加速しています。これらは真に高精度のデバイスであり、直線性誤差は1LSB未満、ドリフトは1ppm/°Cを達成しています。1それでも更に高い性能を要求するDACアプリケーションがあります。自動テスト機器、計測器、較正装置、レーザー・トリマ、医療電子機器、その他のアプリケーションは、しばしば16ビットを超えるDAC精度を必要とします。18ビットDACも回路アセンブリという形態で生産されているものの、高価であると同時に、頻繁な較正が必要です。手動切り替えのケルビン・バーレイ分圧器に代表される、20ビットや23+ビット(0.1ppm!)DACさえ存在します。これらのデバイスは驚くべき精度を持つものの、大型、低速かつきわめて高価です。その用途は通常、標準研究所に限られます。2 有意義な開発は、容易に構築でき、頻繁な較正を必要としない、実用的な20ビット(1ppm)DACと思われます。

20ビットDACのアーキテクチャ

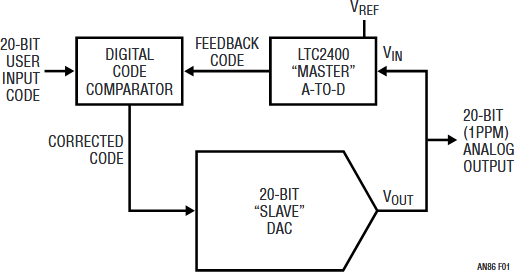

図1は20ビット(1ppm)DACのアーキテクチャを示したものです。この方式は、スケール・ドリフトおよびゼロ・ドリフトが0.02ppm/°C未満の、真の1ppm A/Dコンバータが入手可能であることを前提としています。このデバイスLTC®2400は、20ビットDACを実現するためのデジタル補正ループ内の帰還用部品として使用します。3

図1.ループに基づく20ビットDACの概念図。デジタル比較を用いてA/DコンバータによるDACの誤差補正が可能。LTC2400 A/Dコンバータの低い不確実性が1ppmの出力精度を実現

実際には、「スレーブ」の20ビットDAC出力を「マスタ」のLTC2400 A/Dコンバータによってモニタし、このマスタがデジタル情報をコード・コンパレータに供給します。コード・コンパレータはユーザーが入力したワードとLTC2400の出力の差を求め、補正済みのコードをスレーブDACに入力します。この方法により、スレーブDACのドリフトと非直線性は、A/DコンバータとVREFによって決定される精度まで、ループによって連続的に補正されます4。DACに求められる唯一の要件は、単調であることです。ループ内の他の部品は、いずれも安定である必要はありません。

このループは数々の好ましい特徴を備えています。前述のとおり、精度の限界はA/Dコンバータとそのリファレンス電圧によって決まります。それ以外の部品はいずれも安定である必要がありません。更にループ動作は下位ビットのインデクシングとジッタを平均化するため、ループ固有の小信号不安定性を除去します。最後に、A/Dコンバータを負荷に配置することで、従来のリモート・センシングを使用したり、デジタル信号に基づくセンシングを実現したりすることも可能です。A/DコンバータのSO-8パッケージと、外付け部品が不要であることが、デジタル化されたケルビン・センシング方式を実用的なものにしています。5

回路の詳細

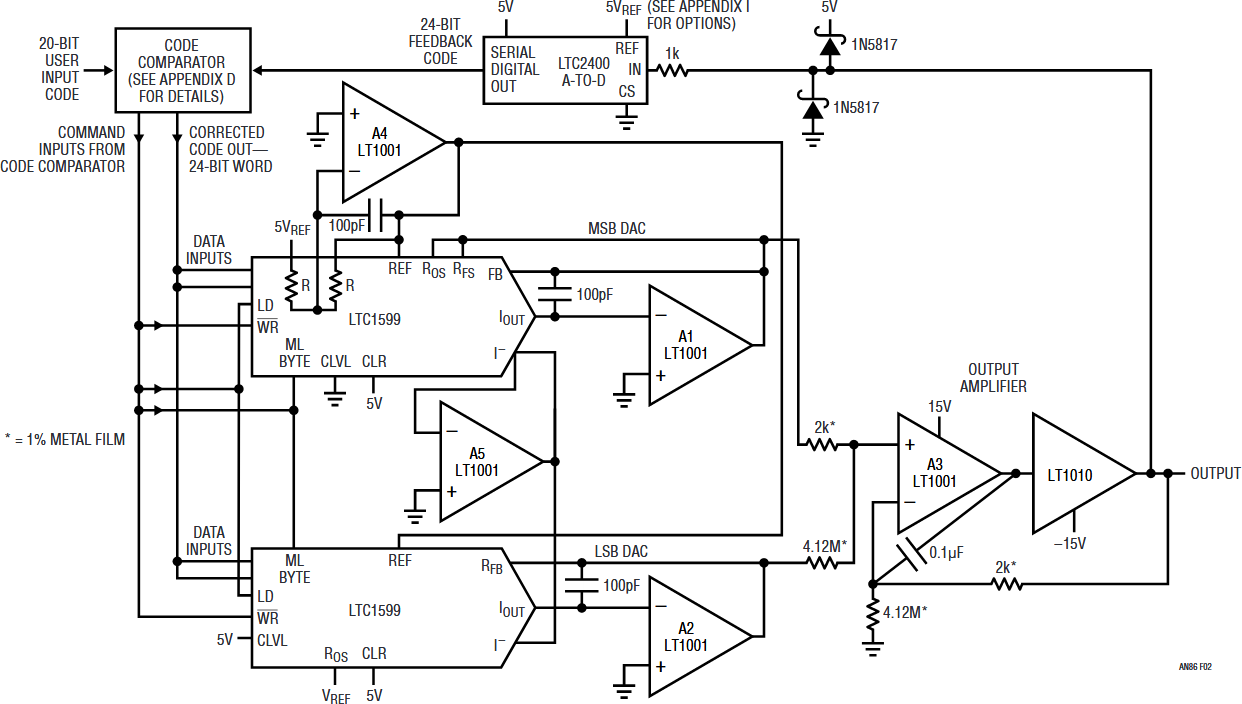

図2に1ppm DACの詳細な回路図を示します。スレーブDACは2つのDACから構成されます。コード・コンパレータ出力の上位16ビットは16ビットDAC(「MSB DAC」)に入力され、下位ビットはこれとは別のDAC(「LSB DAC」)によって変換されます。2つのDACには合計32ビットが入力されるものの、そのうち8ビットは重複しており、あらゆる状況でループ動作を確保できるようにしています。2つのDAC結果を合成して得られる24ビットの分解能は、20 番目のビットより下位に4ビットのインデクシング・レンジを提供し、スケールの1ppmに相当する安定したLSBを保証します。A1とA2はDACの出力電流を電圧に変換し、これがA3で加算されます。A3のスケールは、補正ループがゼロ誤差とフルスケール誤差のあらゆる組み合わせを捕捉および補正できるように調整されます。A3の出力、この回路の出力がLTC2400 A/Dコンバータに供給されます。LT®1010は負荷とケーブルを駆動するバッファ機能を提供します。A/Dコンバータのデジタル出力と入力ワードとの差をコード・コンパレータによって求め、これにより補正済みコードを生成します。この補正済みコードをMSBおよびLSB DACに入力することで帰還ループが閉じます。6ループの完全性はA/Dコンバータと電圧リファレンスの誤差によって決まります。7 5V電源で動作するA/Dコンバータに接続された抵抗とダイオードは、A3の偶発的な出力(電源投入、過渡現象、電源遮断など)からコンバータを保護します。A4はリファレンス・インバータ、A5は両方のDACにクリーンな接地電位を与えます。

図2.1ppm DACの詳細。合成DACは2つのDAC値を出力アンプで加算することで構成される。LTC2400 A/Dコンバータとコード・コンパレータによって安定化帰還を実現する

直線性に関する検討事項

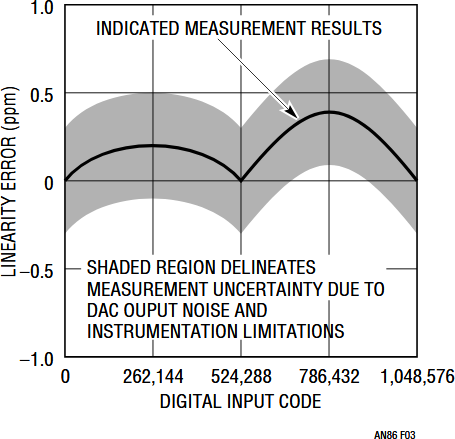

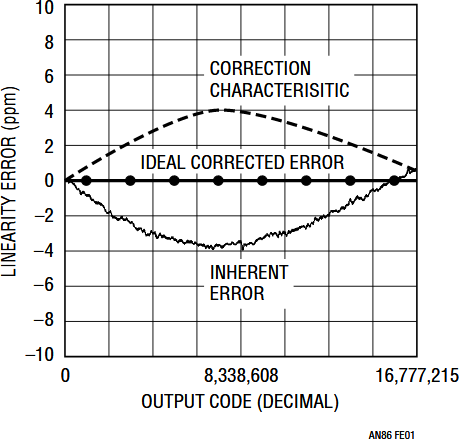

A/Dコンバータの直線性がDAC全体の直線性を決定します。A/Dコンバータの非直線性は約±2ppmです。この誤差を許容できるアプリケーションならば、この値は無視してかまいません。1ppmの直線性が必要な場合は、ソフトウェア手法によって直線性の残留誤差を補正します。LTC2400の直線性およびこの特長の詳細は、付録DとEに記載されています。

DC性能特性

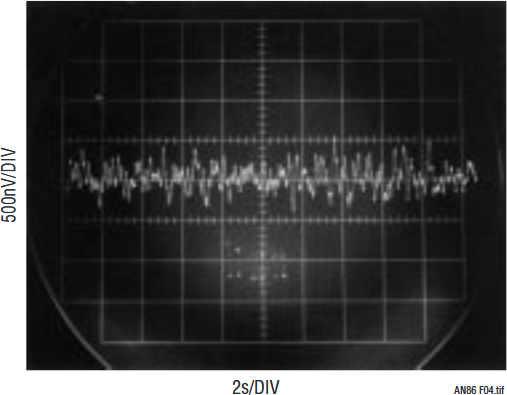

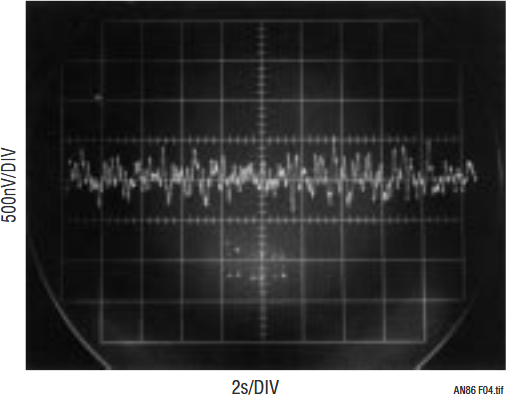

図3は直線性と出力コードのプロットです。このデータから、直線性が全コード範囲で1ppm以内であることがわかります。8 0.1Hz ~10Hzの帯域で測定した出力ノイズは約0.2LSBです(図4)。9この測定は、機器の制約による若干の誤差を含み、約0.2μVのノイズ・フロアが発生しています。

図3. 全コードで±1ppmを上回る誤差が発生していないことを示す直線性のプロット

図4.1μV未満、約0.2LSBの出力ノイズ。機器の制約による測定ノイズ・フロアは0.2μV

ダイナミック性能

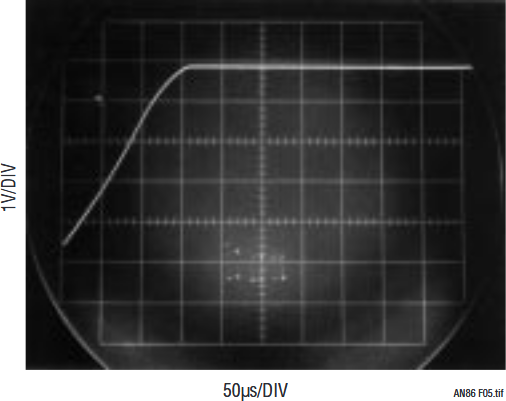

A/D変換レートおよびループのデータ・サンプリング特性と低速のアンプの効果が相まって、DAC応答は比較的低速です。図5のスルー応答には約150μsを要しています。

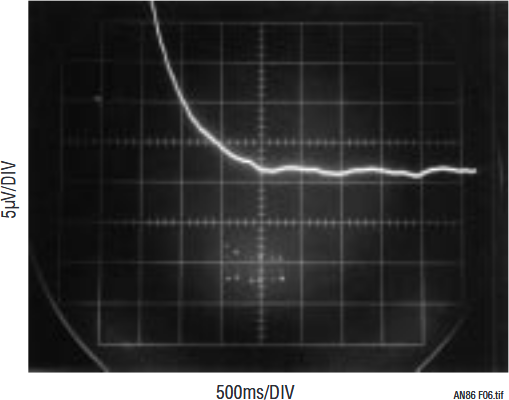

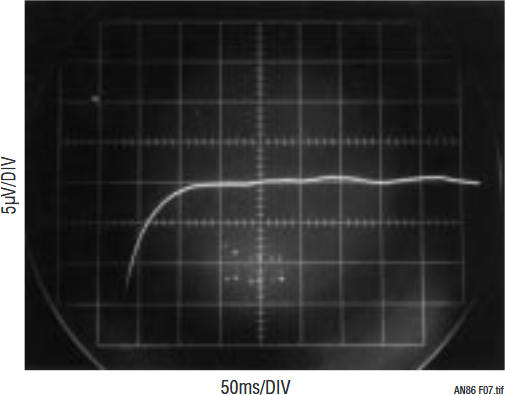

図6からは、フルスケールから1ppm (±5μV)以内へのDACセトリング時間に約1400msを必要とすることがわかります。一方、より小さなステップ(図7)である500μVから1ppmへのセトリングには、わずか100msしかかかりません。10

図5.DACフルスケール出力のスルー特性

図6.フルスケール・ステップ遷移後のセトリング動作の高分解能詳細図。1ppm以内(±5μV)へのセトリング時間は1400ms

図7. 小ステップ(500μV)遷移後の1ppm(±5μV)以内へのセトリング時間は100ms

| パラメータ | 規定値 |

| Resolution | 1ppm |

| Full-Scale Error | 4ppm of VREF(Trimmable to 1ppm by VREF Adjustment) |

| Full-Scale Error Drift | 0.04ppm/°C Exclusive of Reference(0.1ppm/°C with LTZ1000A Reference1) |

| Offset Error | 0.5ppm |

| Offset Error Drift | 0.01ppm/°C |

| Nonlinearity | ±2ppm, Trimmable to Less Than 1ppm2 |

| Output Noise | 0.2ppm(≈0.9μV, 0.1Hz to 10Hz BW) |

| Slew Rate | 0.033V/μs |

| Settling Time—Full-Scale Ste | 1400 Milliseconds |

| Settling Time—500μV Step | 100 Milliseconds |

| Output Voltage Range | 0V to 5V. For Other Ranges See Note 3 |

| Note 1: 付録I参照。 Note 2: 付録E 参照。 Note 3: 付録EおよびF参照。 |

|

図8.20ビットDACの仕様のまとめ

まとめ

1ppm DACの仕様の概要を図9に示します。DACの性能は、注記されたオプションや変動の影響を受けるため、以下の仕様はガイドラインと見なしてください。設計の詳細とトレードオフについては、該当する付録を参照してください。

Notes

このアプリケーションノートは、当初EDN誌に掲載するために作成されたものに加筆変更を加えたものである。

Note 1: 高精度D/A 変換を復習するには、付録Aの「高精度D/A 変換の歴史」を参照のこと。

Note 2: ケルビン・バーレイ分圧器の検討については、付録Cの「1ppmに達するデータ・コンバータ直線性の検証」を参照のこと。更に、付録Aの「高精度D/A 変換の歴史」も参照のこと。

Note 3: LTC2400 A/Dコンバータの特徴は、付録Bの「LTC2400 ― モノリシック24ビットA/Dコンバータ」を参照のこと。

Note 4: D/AコンバータはA/Dコンバータを構成するために、長年にわたってループ内に配置されてきた。このシステムではA/Dコンバータがループに帰還信号を供給し、D/Aコンバータを構成する。このように、今回の開発には合理的な対称性があるように思われる。D/AとA/Dの役割を逆転させた開発である。

Note 5: ケルビン卿は、氏の成果がデジタル化されているのを見て何と言うだろう。進歩の陰に隠れた謎である。

Note 6: コード・コンパレータについては、付録Dの「プロセッサに基づくコード・コンパレータ」で詳述する。

Note 7: 電圧リファレンスのオプションについては、付録Iの「電圧リファレンス」で検討している。LTC2400のチュートリアルは、付録Bを参照のこと。

Note 8: 1ppmの直線性測定の信頼性を確立し、維持することは恐ろしくなるほど最新技術の限界に近づく行為である。測定に使用した手法を、付録Cの「1ppmに達するデータ・コンバータ直線性の検証」に示した。

Note 9: ノイズ測定に関する検討事項は、付録Hの「マイクロボルト・レベルのノイズ測定」に記載されている。

Note 10: 1ppmでDACのセトリング時間を測定することは、今回のように比較的低速の場合であっても一筋縄ではいかない。付録Gの「DACのセトリング時間測定」を参照のこと。

付録A

高精度D/A 変換の歴史

デジタル量をアナログ量に変換する技術の歴史は古く、おそらく最も早くにこの技術が応用された分野の1つが、計量アプリケーションにおける較正済み分銅(図A1、左中央)の加算と思われます。初期の電気D/A変換では、スイッチやさまざまな値の抵抗を使わざるを得なかったでしょう。それらの抵抗値は通常デケード系列に設定されていました。アプリケーションは、多くの場合、ヌル検出による較正されたブリッジの平衡動作または読み出し動作によって未知の電圧を測定するものでした。抵抗を用いたこの種のDACのうち、最も精度の高いものがケルビン卿のケルビン・バーレイ分圧器(図内の大きな筐体)です。スイッチによって切り替え可能な抵抗比によって、比率の精度は0.1ppm(23ビット超)を達成し、標準研究所では現在でも広く使われています。1 高速のD/A変換では、抵抗ネットワークを電子スイッチによって切り換えます。初期の電子式DACはディスクリートの高精度抵抗とゲルマニウム・トランジスタを用いて、基板レベルで構築されました(写真中央の前列は、ミニットマン・ミサイルD-17Bの慣性航法システムに使われていた(1962 年頃)12ビットDACです)。標準製品として出回るようになった最初の電子スイッチ式DACは、おそらくPastoriza Electronics 社が1960 年代中頃に製造した製品でしょう。その他のメーカも追随し、1970 年代までにはディスクリートおよびモノリシック部品によるモジュール式DAC(写真右と左)が一般化しました。ユニットは堅牢性と性能を向上するとともに、(願わくば)専有知識を保護できるように、しばしばポッティングされていました。やがて、ハイブリッド技術により、更に小型のパッケージ(写真左前)が製造されるようになります。シリコン・クロム抵抗の開発により、LTC1595(写真最前列)などの高精度モノリシックDACが可能になります。全てをモノリシック化することに伴う、現在の高分解能IC DACのコスト・パフォーマンス・トレードオフはきわめてお買い得な状況です。考えてもみてください。16ビットDACが8ピンのICパッケージに収まるのです。ケルビン卿にクレジット・カードを渡し、LTCの電話番号を教えたら、何をおいても発注したことでしょう。

図A1.歴史的意義の大きいD/Aコンバータ:分銅(中央左)、23+ビットのケルビン・バーレイ分圧器(大きな筐体)、ハイブリッドの基板およびモジュール式コンバータとLTC1595 IC(前列)。いったい、どこまで発展するのだろうか

Note

Note 1: ケルビン・バーレイ分圧器の詳細は、付録Cの「1ppmに達するデータ・コンバータ直線性の検証」を参照のこと。

付録B

LTC2400―モノリシック24ビットA/Dコンバータ

LTC2400はオシレータ内蔵のマイクロパワー24ビットA/Dコンバータで、4ppmの非直線性と0.3ppmのRMSノイズを実現しています。そのきわめて高い安定性は、ΔΣ技術によるものです。デバイスは50Hzまたは60Hz±2%において110dBを超える遮断率に設定するか、外部オシレータによって駆動することによって、1Hz~120Hzの範囲でユーザー定義の遮断周波数を使用することができます。

このSO-8ピン・パッケージに収められた超高精度A/Dコンバータは、本文で解説した20ビットDACの心臓部をなすものです。このデバイスが従来のスタンドアローン的な役割を与えられた高精度A/Dコンバータではなく、回路中の1つの部品として使われていることは、大きな意味を持ちます。その自由度は、ICの経済性や使いやすさと相まって、特筆すべきチャンスをもたらします。目ざとい設計者ならば、この開発を高く評価し、十分に活用するでしょう。A/Dコンバータの主な仕様を図B1に示します。

| パラメータ | 条件 | |

| Resolution (No Missing Codes) | 0.1V ≤ VREF ≤ VCC | 24 Bits |

| Integral Nonlinearity | VREF = 2.5V VREF = 5V |

2ppm of VREF 4ppm of VREF |

| Offset Error | 2.5V ≤ VREF ≤ VCC | 0.5ppm of VREF |

| Offset Error Drift | 2.5V ≤ VREF ≤ VCC | 0.01ppm of VREF/°C |

| Full-Scale Error | 2.5V ≤ VREF ≤ VCC | 4ppm of VREF |

| Full-Scale Error Drift | 2.5V ≤ VREF ≤ VCC | 0.01ppm of VREF/°C |

| Total Unadjusted Error | VREF = 2.5V VREF = 5V |

5ppm of VREF 1ppm of VREF |

| Output Noise | 1.5μVRMS | |

| Normal Mode Rejection 60Hz ±2% | 110dB (Min) | |

| Normal Mode Rejection 50Hz ±2 | 110dB (Min) | |

| Input Voltage Range | 0.125V • VREF to 1.125V • VREF | |

| Reference Voltage Range | 0.1V ≤ VREF ≤ VCC | |

| Supply Voltage | 2.7V ≤ VCC ≤ 5.5V | |

| Supply Current Conversion Mode Sleep Mode |

CS = 0V CS = VCC |

200μA 20μA |

図B1.LTC2400 A/Dコンバータの主な仕様。優れた直線性と高い安定性によって1ppm DACを実現

付録C

1ppmに達するデータ・コンバータ直線性の検証

19 世紀からの助っ人

はじめに

DACおよびこれを構築するために使われるA/Dコンバータの直線性を1ppmに至る精度で検証するには、特別な配慮が求められます。テストには、デジタル入力のインクリメントに合わせて等分の振幅出力ステップを発生する、何らかの形の電圧源が必要です。更に、測定の信頼性を得るには、この電源が1ppmの要件よりもはるかに高い直線性を備えていることが望まれます。当然これは、最新技術の限界に肉薄する、厳しい要求です。

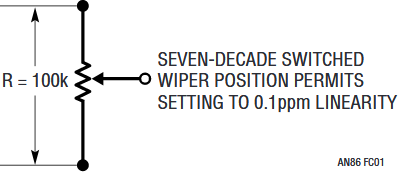

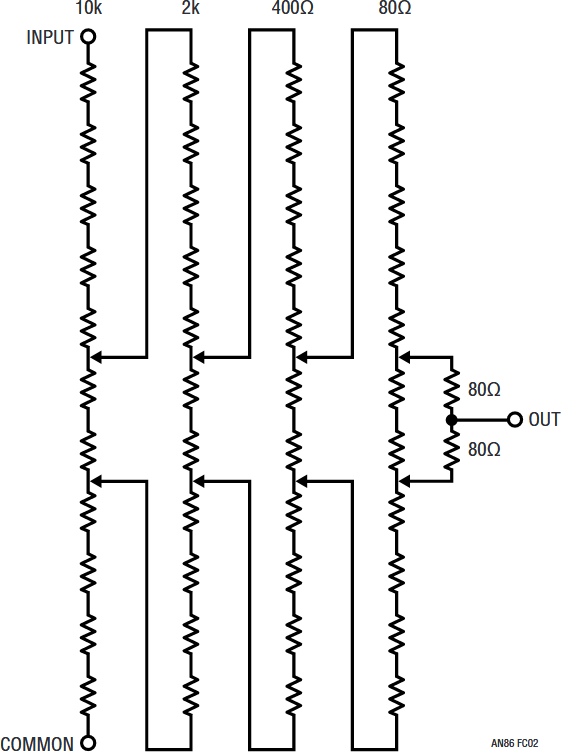

しかし、最も直線性のよい「D/A」コンバータは、きわめて歴史あるコンバータでもあります。ケルビン卿の、ケルビン・バーレイ分圧器(KVD)の最も発展した形式では、0.1ppmに及ぶ直線性を達成しています。この手動切り替え型のデバイスは、7デケードにわたって個別に1000 万通りの設定が可能なダイアルを備えています。「エンド・ツー・エンド」抵抗が一定で7デケードの設定位置があるスイッチ型ワイパを持った、3 端子ポテンショメータと考えればよいでしょう(図C1)。

図C1.ケルビン・バーレイ分圧器の概念

0.1ppm KVDを実際に構築する作業は、科学よりも芸術や魔法に近い領域かも知れません。市場は比較的小さく、ベンダ数が少ないことから、価格も高くなります。大量のスイッチと抵抗だけに13,000ドルという価格が納得できない方は、ご自分でKVDを作り、認証を受けてみてください。図C2に詳細な回路図を示します。

図C2.4デケードのケルビン・バーレイ分圧器。更に多くのデケード数を実装するには、最後のスイッチを開放して、そこに接続されている2つの80Ω抵抗を取り除いた上で、引き続き5 分割の抵抗チェーンを必要な段数だけ接続する

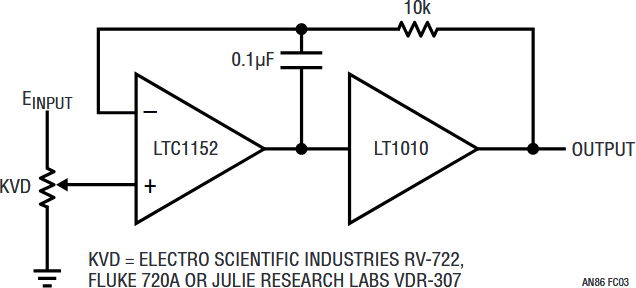

ここに示したKVDの入力インピーダンスは100kΩです。そのため、ワイパ出力の抵抗が高くなり、設定によって変動します。したがって、大きな誤差を発生させずにKVDの負荷を軽くするには、バイアス電流が非常に小さい電流フォロワが必要です。リニアテクノロジーのKVDは図C3のように構成されています。出力バッファのLT1010によってケーブルと負荷を駆動できるとともに、より微妙な特徴として、アンプの高い開ループ利得を保つことができます。

図C3.バッファ付きKVDによる出力駆動機能

手法と誤差に関する検討事項

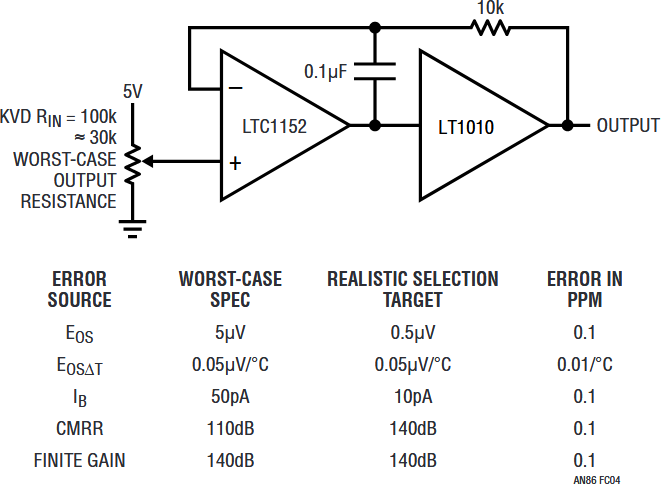

この回路図は一見単純そうに見えます。しかし、実際には回路構成上の細かい部分がきわめて重要です。寄生熱電対(ゼーベック効果)、レイアウト、接地、シールド、ガード・リング、ケーブル選定、その他の要因が到達性能に影響を与えます。1実際、ドリフト、オフセット、バイアス電流、CMRRについてはチョッパーによって安定化したLTC1152でも同等の性能が得られますが、1ppm未満の非直線性性能を追求する場合、選択が必要です。図C4の誤差予算解析から、一部の選択基準の詳細がわかります。

図C4.KVDバッファの誤差予算分析。上記の選択により約0.4ppmの予想直線性誤差を実現可能

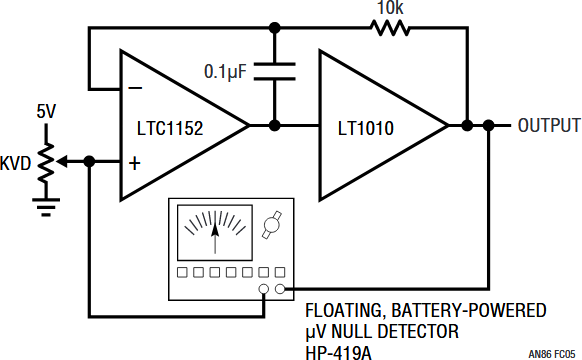

バッファは図C5の回路によってテストされます。KVDを全レンジにわたって動作させる際、フローティングのヌル検出器は余裕を持って1ppm(5μV)以内、可能ならば0.5ppm未満を保つ必要があります。このテストは、全ての誤差要因、特に動作点によって影響度が変動するIBとCMRRを考慮しています。測定によって得られた性能は、図C4の下に示した誤差の合計が必要な制限値を十分に満たしていることを示しています。

図C5.フローティング・マイクロボルト・ヌル検出器による入力-出力偏差の測定からバッファ誤差を決定する。この手法により固定誤差および動作点に起因する誤差の評価が可能

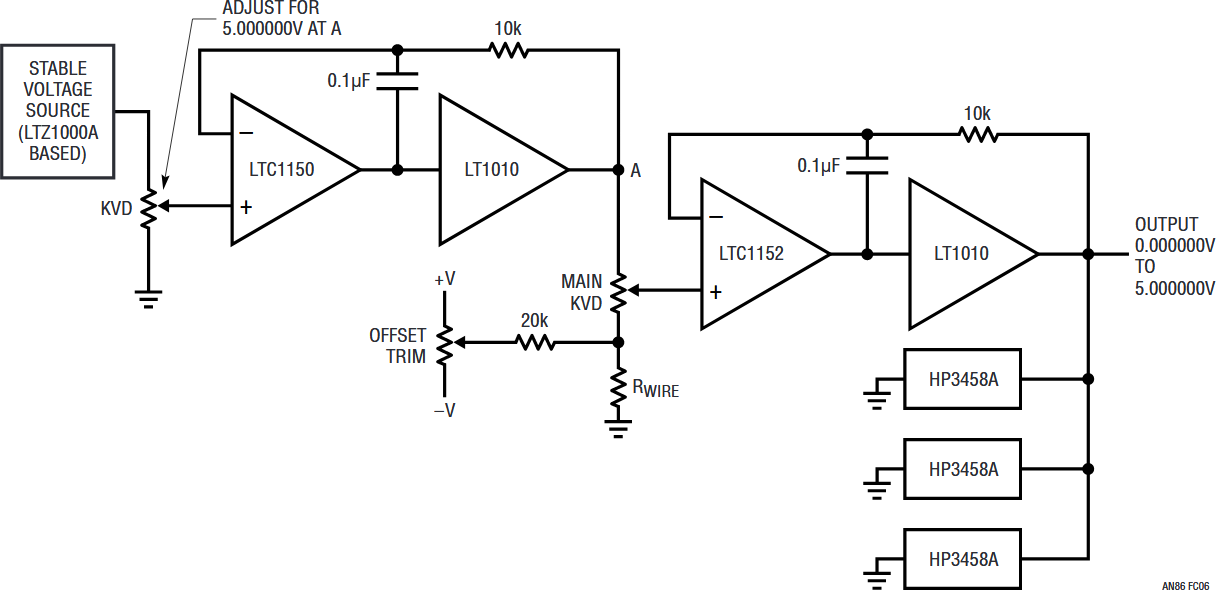

図C6は、オフセットのトリマ、安定な電圧源、メインKVDを駆動する第2のKVDを追加した構成です。更に、3つのHP3458A電圧計を組み合わせて出力をモニタしています。

図C6.サブppmの直線性を備えた電圧源(簡略図)

オフセット・トリマを介してメインKVDのグランド・リターンに小電流が流れ、数マイクロボルトのオフセット・トリマ・レンジを発生させます。これが機能的にトリミング動作となり、全てのゼロ誤差の要因(アンプのオフセット、寄生熱電対の不一致など)を排除します。これによって、メインKVDがオール・ゼロに設定されたときに真のゼロボルト出力が可能になります。

10Vレンジで0.1ppm未満の非直線性仕様を持つ電圧計が、電源出力を決定します。

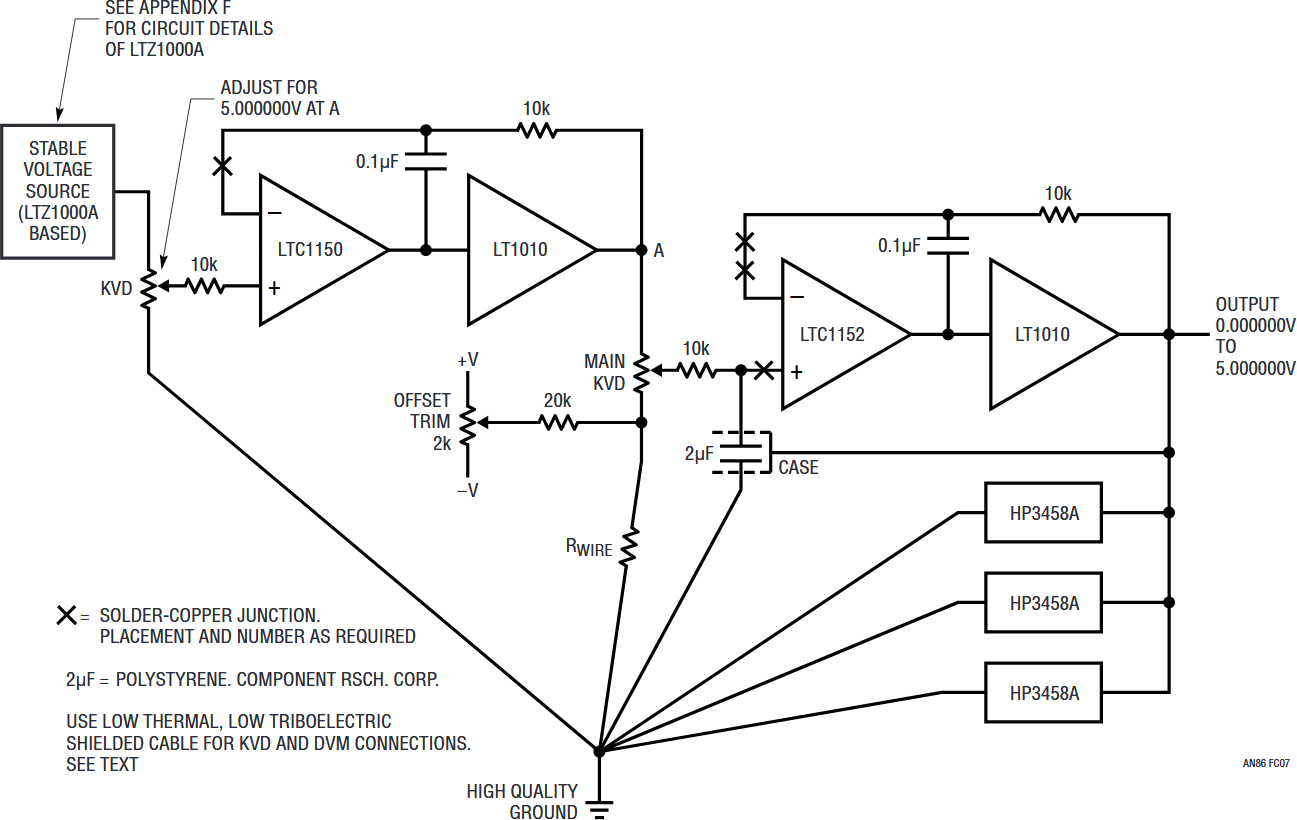

回路の詳細

図C7に、より詳細な回路図を示します。図C6に似た図ですが、課題と懸念事項を指摘しています。1 点接地方式が、リターン電流と付随する誤差が混合することを防ぎます。KVDと電圧計間の相互接続に使用するシールドされたケーブルは、熱活性が低い仕様のものを使用する必要があります。KeithleyタイプSC-93およびGuildline #SCWが適しています。ハンダ付けタイプではなく圧着タイプの端子を使用することで、KVDとDVMの接点における寄生熱電対の効果を抑えます。ただし、これらの端子は清浄に保って酸化を防ぎ、熱電圧の過剰な発生を予防する必要があります。2 このような清浄性を維持するには、銅脱酸素剤(Caig Labs 「Deoxit」 D100L)がきわめて有効です。低熱活性の、ケーブル終端済みの端子やジャックも市販されており(Hewlett-Packard 11053、11174A)、便利です。

図C7.サブppmの直線性を備えた電圧源(詳細図)

KVDとDVMの接続部を熱バッフル内に収納すると、関連するバナナ・ジャック端子を熱平衡状態に導く効果があり、残留する寄生熱電対効果を最小限に抑えることができます。また信号経路内の接続の数を制限してください。差動動作による相殺効果をねらって、必要な接続数は一致させます。このガイドラインに従おうとすると、最適な差動相殺を実現するために、意図的にハンダ- 銅接合を追加する必要が生じる場合があります(図C7の「X」印)。3 これは、単に該当するワイヤまたは基板トレースを切断した上で、それらをハンダ付けすれば実現できます。この措置によって追加される熱電対の温度が、相殺しようとする接合部の温度に追随することを確認してください。追随させるには、通常全ての接合部を物理的に近接させて配置します。

メインKVDのノイズ・フィルタ用コンデンサは漏れ電流の小さいタイプとし、その金属ケースを出力バッファによって駆動することで表面リークから保護します。

今回使用した手法を検討する場合、直線性と絶対精度を区別することが重要です。これによって、絶対標準を懸念する必要がなくなり、測定方式にある程度の自由度が得られます。具体的には、1 点接地は使用したものの、リモート・センシングは使用しなかった点が挙げられます。これは、誤差を生む可能性がある信号経路内の寄生熱電対の数を最小限に抑えるための意図的な選択です。同様に、KVDのLTZ1000A電圧源と電圧計間にレシオメトリックなリファレンス接続を用いなかったのも同様の理由からです。理論的にはレシオメトリック接続の方がドリフトは小さくなります。しかし、実際にはこの接続方法が招く寄生熱電対効果が、本来目的とするメリットを打ち消してしまいます。LTZ1000Aリファレンスと電圧計のリファレンス(偶然にも、こちらもLTZ1000Aを使用)を合わせた総安定性は、10 分間の期間で0.1ppm以内を十分に達成しています。4 10 分間もあれば、直線性の10 点測定には十分です。

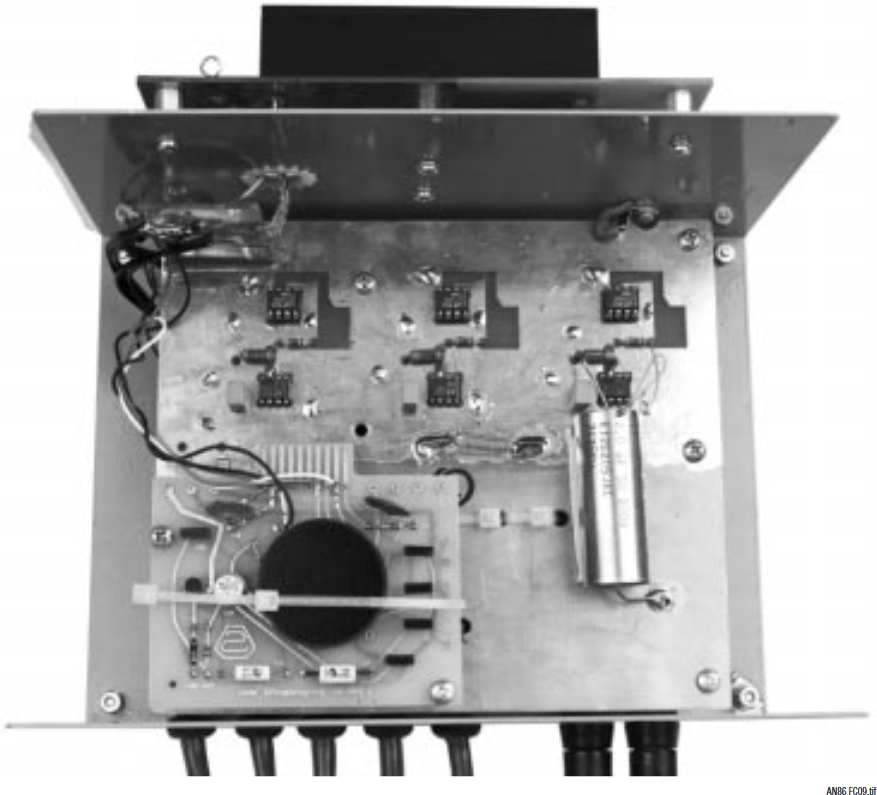

構造

図C8とC9は、電圧源およびリファレンス・バッファ筐体の内部構造の写真です。図のキャプションに主な特徴を併記してあります。

図C8.サブppmの直線性を備えた電圧源。右上の筐体はLTZ1000Aを用いたリファレンスとバッファ。左上はオフセット・トリマ。リファレンスとメイン・ケルビン・バーレイ分圧器は写真中央のそれぞれ上と中央。3 台のHP3458デジタル電圧計(DVM)(写真下)が出力をモニタする。コンピュータ(写真左前列)を使って直線性を計算する

図C9.リファレンス・バッファ筐体の内部構造。LTZ1000Aリファレンス回路は写真左下、バッファ・アンプは写真中央。コンデンサ・ケースのブートストラップ接続(写真中央~右)に注目のこと。1 点接地している箇所が写真左上に見える。電源(写真上)は筐体外部に取り付けられ、磁界の外乱を最小限に抑えている

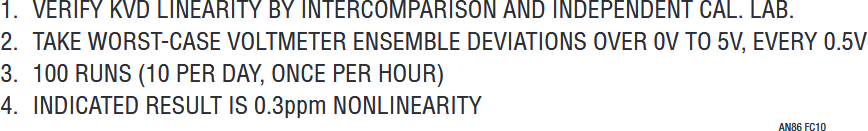

結果

KVDに基づいた、この高い直線性を備えた電圧源は、筆者らの実験室で2 年近く使われてきました。この間、電圧源とそのモニタ用電圧計によって規定される直線性の総不確実性はわずか0.3ppmでした(図C10の測定方法参照)。これは目標性能である1ppmよりも3 倍も優れた特性であり、筆者らの測定に対する信頼を更に高めるものです。5

図C10.高直線性電圧源のテスト方法

謝辞

筆者はケルビン卿、および標準研究所であるC. S. Draper Laboratory( 旧M. I. T. Instrumentation Laboratory)のWarren Little 氏に感謝します。Warren 氏は、およそ30 年前、KVDの魅力を辛抱強く教えてくれた人物であり、筆者は現在でもそのときの彼の努力を仕事の糧としています。

Notes

Note 1: 関連するチュートリアルは、付録Jの「ケーブル、接続、ハンダ付け、レイアウト、部品選定、隠れた危険と奥義」を参照のこと。

Note 2: 上記の脚注を参照のこと。

Note 3: 詳細な検討は、付録Jの「ケーブル、接続、ハンダ付け、レイアウト、部品選定、隠れた危険と奥義」を参照のこと。

Note 4: LTZ1000Aリファレンスの詳細は、付録Iの「電圧リファレンス」を参照のこと。

Note 5: ウェブ・サーフィンには何の魅力も感じない筆者であるが、「ケルビン卿サーフィン」は何時間も楽しむことができた。これは、ケルビン・バーレイ分圧器で数々のダイアル設定を試し、モニタ用A/Dコンバータとの一致度が1ppm以内であることを確認する活動である。驚くほどのオタク的行動であるが、ある種の人々にとっては胸躍らされる瞬間なのである。

付録D

プロセッサに基づくコード・コンパレータ

コード・コンパレータは、スレーブDACの入力を、ユーザー入力とLTC2400 A/D出力を一致させるコードに設定することで、ループを制御します。この動作は、本文の1ページで詳述しています。

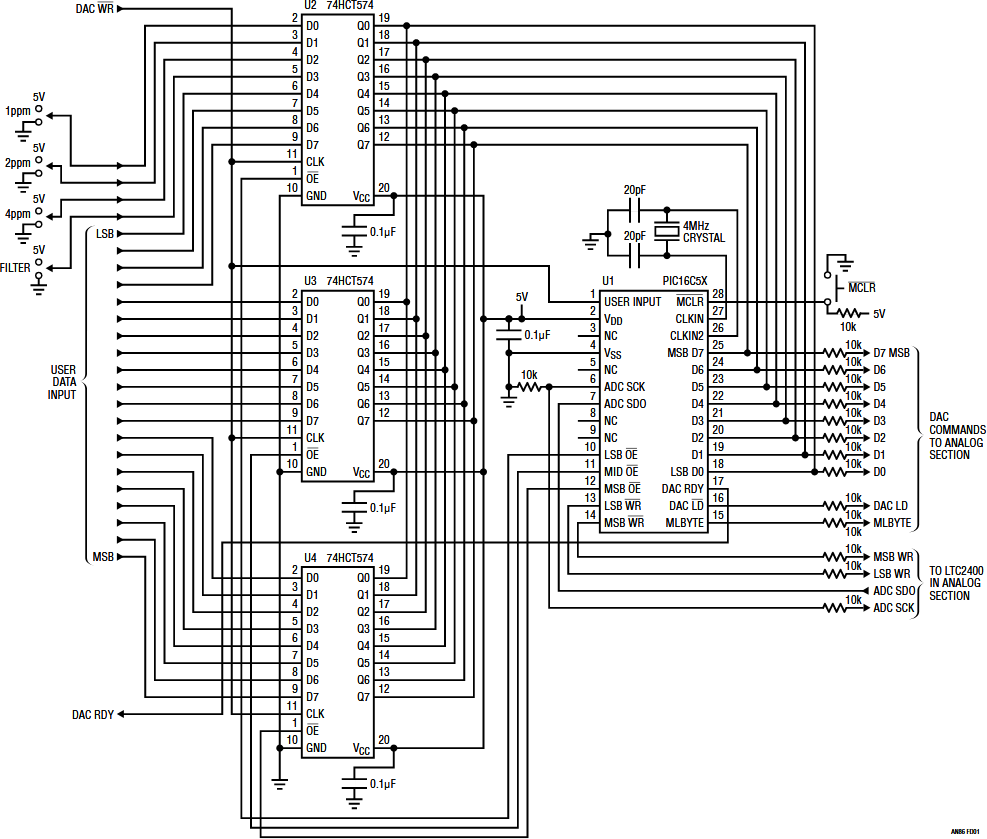

図D1は、コード・コンパレータのデジタル・ハードウェアです。3つの入力データ・ラッチとPIC-16C5Xプロセッサから構成されます。入力には、ユーザー・データ(例:DAC入力)、直線性曲率補正(DIPスイッチによる)、変換コマンド(「DA WR」)、選択可能なフィルタ時定数などがあります。出力(「DACRDY」)は、DAC出力がユーザーの入力値へのセトリングを完了したことを示します。その他の出力と入力がアナログ部分(本文の図2)を制御およびモニタし、閉ループ動作に影響を与えます。2つの16ビット・スレーブDACには合計32ビットが入力されているものの、8ビットは重複しているため、総ダイナミック・レンジは24ビットです。これによって20 番目のビットより下位に4ビットのインデクシング・レンジを提供し、スケールの1ppmに相当する安定したLSBを保証します。8ビットの重複部分によって、ループは常に適切な出力値を取得できます。

図D1.コード・コンパレータのハードウェア。ユーザー制御ラインは左側、アナログ部分の接続は右側にある。

プロセッサはFlorin Oprescuが作成したソフトウェア・コードによって動作します。このコードを以下に示します。

;20bit DAC code comparator

;

;***************************************************

; *

; Filename: dac20.asm *

; Date 12/4/2000 *

; File Version: 1.1 *

; *

; Author: Florin Oprescu *

; Company: Linear Technology Corp. *

; *

; *

;***************************************************

;

; Variables

;============

; uses 17 bytes of RAM as follows:

;

; {UB2, UB1, UB0} user input word buffer

;———————————————————————————————————————

; 24 bits unsigned integer (3 bytes):

;

; The information is transferred from the external input register

; into {UB2, UB1, UB0} whenever a “user input update” event

; is detected by testing the timer0 content. Following the data

; transfer, the UIU (“user input update”) flag is set and the DAC

; ready flags RDY and RDY2 are cleared. UB0 uses the same physical

; location as U0. The user input double buffering is necessary

; because the loop error corresponding to the current ADC reading

; must be calculated using the previous user input value.

; The old user input value can be replaced by the new user input

; value only after the loop error calculation. Read full article

付録E

直線性と出力レンジのオプション

帰還A/D部品としてDACで用いられているLTC2400には、±2ppm(代表値)の残留非直線性があります。図E1の下側の曲線がこれを示したものです。図には非直線性を1ppm以内(中央の曲線)にするために必要となる1 次補正(上側の曲線)を併記してあります。真の1ppm性能が必要な場合は、付録Dで解説したソフトウェアによる補正を使用できます。ソフトウェアによって必要な「反転ボウル型」の補正特性を生成します。あらゆるLTC2400単体について残留非直線性を補完するために、コード・コンパレータのDIPスイッチによって補正条件を設定することも可能です。

図E1.LTC2400 A/Dコンバータの固有残留直線性誤差(下)、補正特性(上)、補正後の直線性(中央)。補正により1ppm未満の非直線性を保証

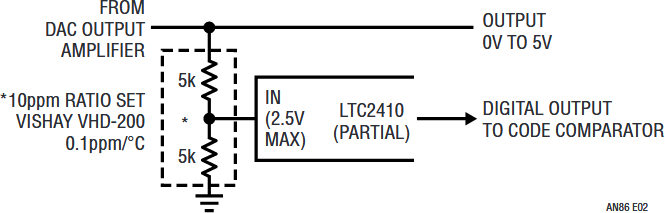

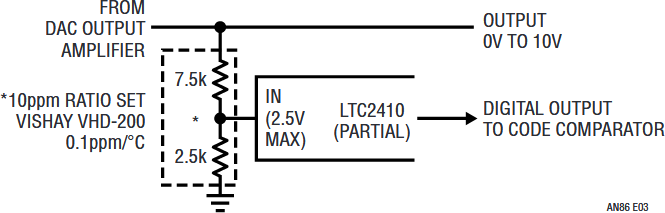

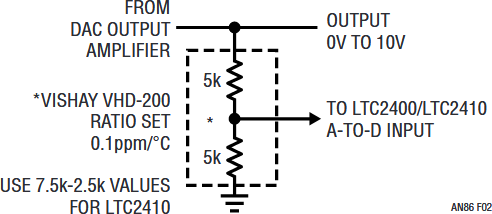

LTC2410には、直線性を改善するもう1つの方法が用意されています。このLTC2400のバリアントは直線性が改善されているものの、最大入力レンジの仕様が2.5Vです。図E2では、高精度抵抗の比率設定によりDAC出力を分圧することで、フルスケール出力の5Vを保ちつつ、LTC2410を使用できるようにしています。この手法の不利な点は、比率設定によって誤差が0.1ppm/°Cおよび5ppm/年だけ増加することです。1 図E3も同様の回路ですが、比率設定に新たな値を用いることでフルスケール出力10Vへの対応を可能としています。

図E2.高精度抵抗の比率設定がDAC出力を分圧し、固有直線性が強化されたLTC2410の適用を可能とする。デメリットは5ppm/年および0.1ppm/°Cのドリフト増加である

図E3.図E5と同様。ただし、比率設定を3:1とすることでLTC2410の2.5V 入力に対応しつつ、10V出力を使用できるようにする

Note

Note 1: 「誤差への寄与」が1ppm未満および年間ドリフト率が上記の値で表されるようになり、層はより薄くなりつつある。

付録F

出力段

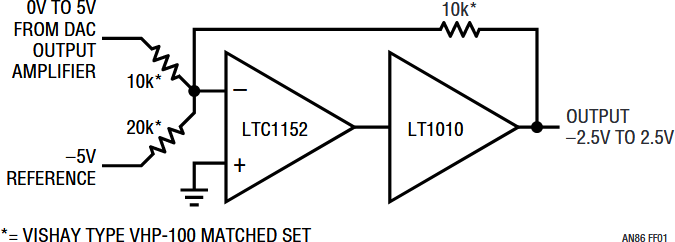

アプリケーションの中には、本文に示した回路の0V~5Vレンジ以外の出力を必要とするものもあるでしょう。最も簡単な変形例が、図F1に示すバイポーラ出力です。この加算インバータの回路は、リファレンスからDAC出力を差し引いてバイポーラ出力を得ています。抵抗およびリファレンスの値を変更して、異なる出力レンジに設定することも可能です。LT1010出力バッファが駆動能力を提供し、チョッパーによって安定化されたアンプが0.05μV/°Cの安定性を保持します。抵抗によって、0.3ppm/°Cの誤差が生じます。1

図F1.高精度抵抗とチョッパー安定化出力アンプによりバイポーラDAC出力に対応。トレードオフ:抵抗追加による約0.3ppm/°Cの誤差増加

図F2では、DAC出力を帰還A/Dコンバータに印加する前に分圧することで電圧利得を得ています。この場合、分圧比を1:1に設定すると出力は10Vになります(A/Dコンバータのリファレンスが5Vの場合)。図F1に示すとおり、抵抗によって温度誤差がわずかに増加します。規定の比率設定の場合、約0.1ppm/°Cです。2

図F2.A/Dコンバータにおける帰還分圧によって×2の電圧利得を実現。その結果、総温度係数が若干増加する

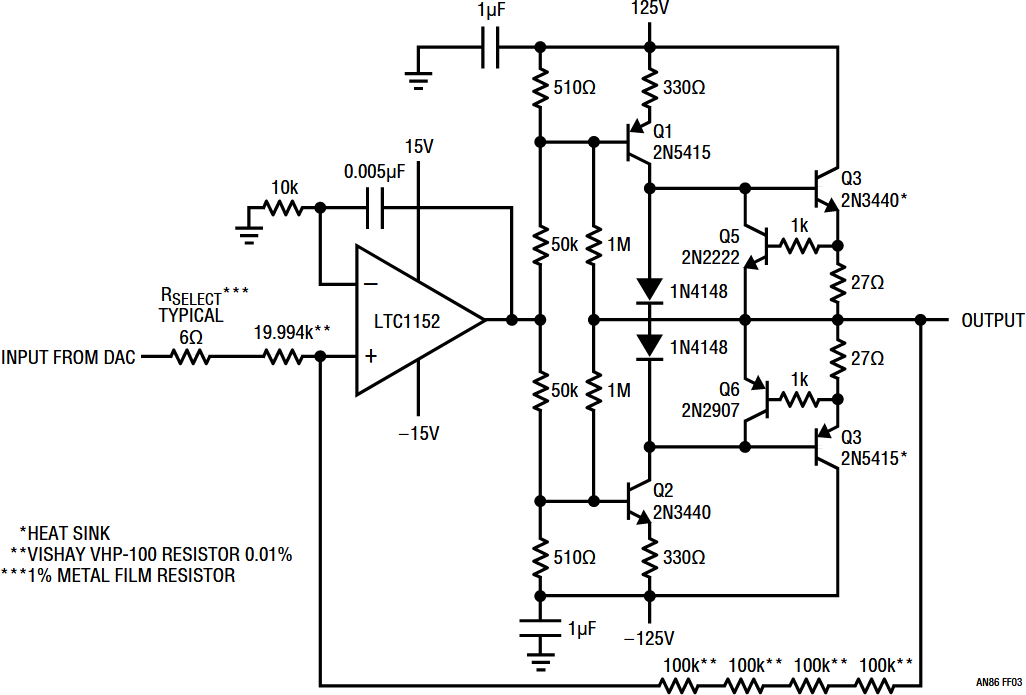

図F3では、±100Vに達する電圧出力に対応するために、能動デバイスを使用しています。ディスクリートな高電圧段は、チョッパー安定化アンプにより閉ループ方式で駆動されます。Q1とQ2が電圧利得を与えるとともに、Q3-Q4のエミッタ・フォロワ出力を供給します。Q5とQ6は、27Ωのシャント抵抗両端の電圧が過度に高くなると出力駆動を迂回させ、電流を25mAに制限します。1M-50kのローカル帰還抵抗のペアが、この出力段の利得を20に設定し、LTC1152の駆動によって±120Vのフル出力振幅が得られるようにします。ローカル帰還によって、出力段の利得帯域幅が小さくなり、動的制御が容易になります。電圧利得に寄与する部品がQ1とQ2だけであることから、この段の周波数補償は比較的簡単に実現できます。更に、高耐圧トランジスタは接合部が大きいため、ftsが小さく、高周波におけるロールオフに対して特別な注意は不要です。反転出力段であることから、帰還はアンプの正側入力に戻します。周波数補償は、0.005μF-10kΩのローカルによってアンプをロールオフすることで実現します。

図F3.高電圧出力段による±100V/25mAの供給。複数の帰還抵抗によって消費電力と電圧係数の効果を最小化する

4つの独立した抵抗を使用することで、帰還の項に含まれる発熱および電圧係数による誤差を最小限に抑えます。トリミングは、DACのフルスケール出力が正確に100.0000Vになるように、図示した抵抗を選択して行います。

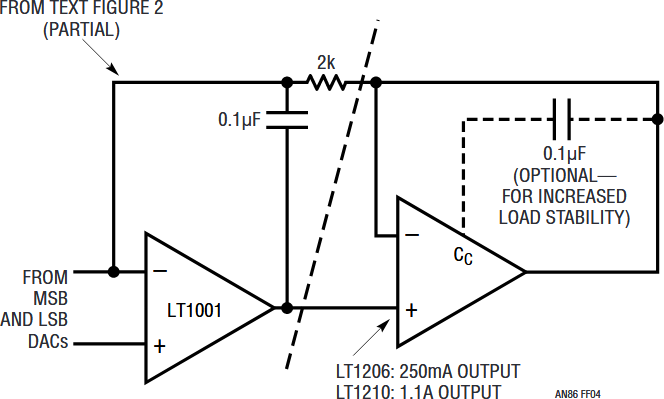

図F4はDAC出力アンプの帰還ループ内に電流利得段を設けることで出力電流能力を強化しています。この出力段を、本文に示した150mA出力のLT1010バッファと置き換えます。図には、出力能力の異なる2 通りのオプションを示しました。出力電流が増加すると、配線抵抗が大きな潜在的誤差の項になることを指摘しておくのは無駄ではないでしょう。例えば、わずか10mAの出力と配線抵抗0.001Ωでも10μVの電圧降下が生じ、これは2ppmの誤差に相当します。このため、大きな負荷には短く導電性の高い経路によって給電し、リモート・センシングを適用する必要があります。

図F4.LT1206/LT1210による出力段が、それぞれ250mAおよび1.1A負荷を駆動。通常、IR 電圧降下を補償するためにリモート・センシングが必要

Notes

Note 1: 付録EのNote 1 参照。

Note 2: 上記の脚注参照。

付録G

DACのセトリング時間測定

20ビットDACの出力セトリング時間を測定するのは困難な作業です。使用する時間軸は比較的低速であるものの、5μVというLSBのステップ・サイズが問題になります。この課題は、モニタ用オシロスコープでオーバードライブが発生しないようにしつつ、大きな利得を実現するという課題に還元できます。このようなオーバードライブは測定値を乱し、表示される結果を無意味なものにします。

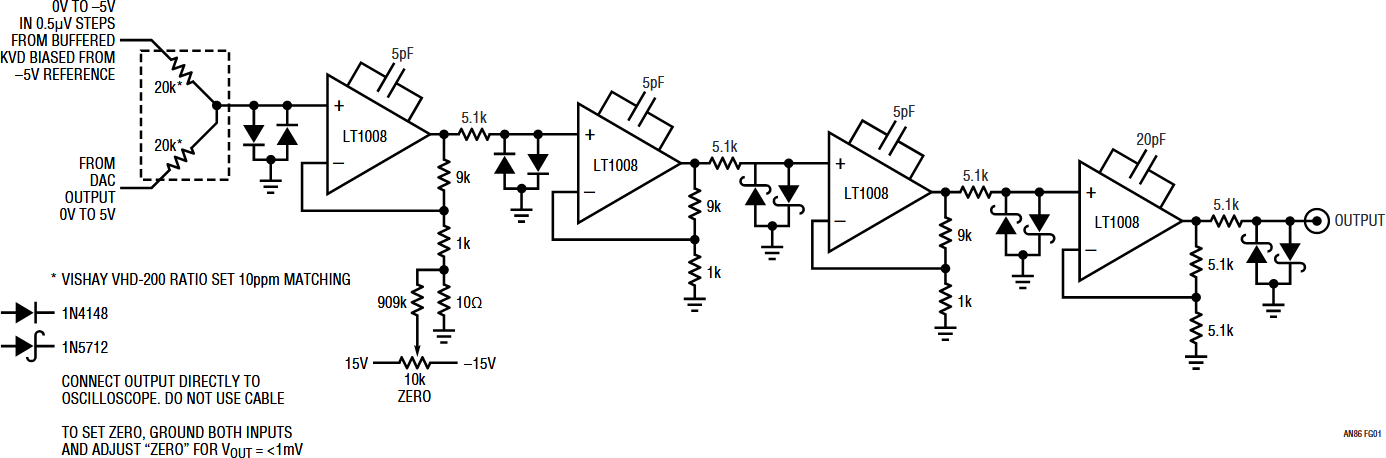

図G1が、この課題の解決策です。DACの出力と、0.5μVステップで調整可能な高精度可変リファレンス電源を、抵抗によって平衡させます。1 回路の残りの部分は、クランプされ、利得2000を分散させたアンプを構成します。各利得段の入力に配置されたダイオード・クランプは、DACとリファレンス電源のアンバランスが大きい場合でも飽和が発生しないようにします。また、利得を分散させることで、クランプの効果を保ちつつ10kHzの帯域幅を可能とします。モニタ用オシロスコープは5mV/DIVまたは10mV/DIV(DAC出力部分では5μV~10μV)で動作し、有害なオーバードライブを生じることなく、5μVのセトリングを十分に識別できます。

図G1.クランプされた分散利得2000のアンプによって飽和の影響を受けずにDACのセトリング時間測定が可能

この回路のレイアウトと構造には注意が必要です。図G2に詳細な構造を示します。直線状のレイアウトによって、寄生帰還経路を最小限に抑え、発振を防止します。DAC入力ステップ信号は完全にシールドされ、アンプ内のさまざまな高感度ノードへのフィードスルーを防止します。最後に、回路全体をシールドされた筐体に収め、浮遊RFやピックアップ・ノイズの効果を最小化します。

図G2.セトリング時間アンプの構造利得が2000でありながら帯域幅はわずか10kHzであることから、寄生帰還による発振を予防する注意深いレイアウトが必要。入力(写真左下)は完全にシールドされ、アンプへの放射フィードスルーを防止している。筐体は回路を浮遊RFとピックアップ・ノイズからシールドする

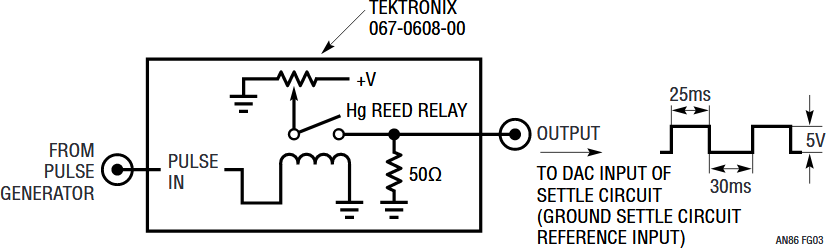

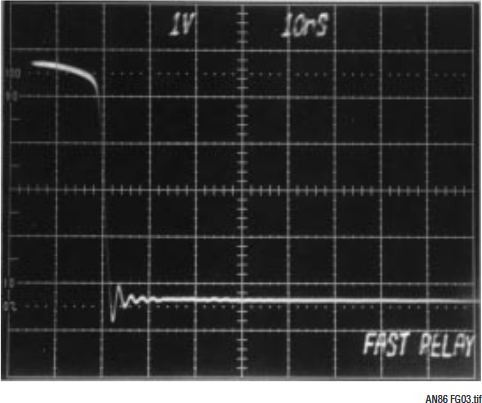

この回路は、DACよりもはるかに短時間でセトリングするテスト・ステップを印加することでテストします。図G3では、水銀リード・リレーを用いたパルス・ジェネレータによってステップ信号を供給しています。図に示したユニットは、市販品として生産されています。ただし標準の水銀リード・リレーでも同様の結果を得ることができます。リレーが開くと、この回路の出力は、DACのスピードやアンプ帯域幅のセトリング時間に比べれば、基本的に瞬時にセトリングします(図G4)。

図G3.リード・リレーを用いたパルサはセトリング時間テスト回路にクリーンなステップ信号を供給する

図G4.水銀リード・リレーは5nsで開放され、即座にゼロにセトリングする。500MHzのリングオフはソース終端インピーダンスの不整合によって生じたものである

図G1の応答は、入力の一方を接地し、もう一方をパルス・ジェネレータによって駆動することでテストしたものです。図G5は、1ppm (±5μV)以内へのセトリング時間が2msであることを示しています。これはDACのセトリングよりもはるかに高速であり、本文の図6および図7に示した結果の信憑性を高めます。

図G5.テスト・ステップ信号に対するセトリング時間測定回路の応答。±1ppm(±5μV)に2msでセトリングしている

Note

Note 1: このような電源の詳細は、付録Cを参照のこと。

付録H

マイクロボルト・レベルのノイズ測定

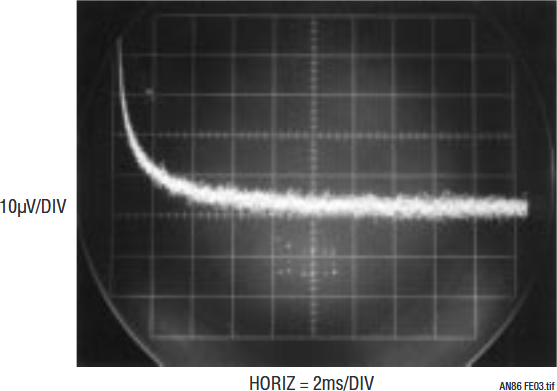

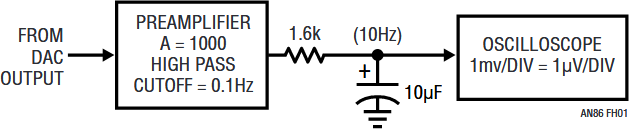

DAC出力ノイズの検証には、オシロスコープ部分にノイズの少ない、高利得のアンプが必要です。図H1に、このような測定に適用される1つの方法を示します。信号は、利得1000で動作する入力プリアンプによって0.1Hzでハイパス遮断され、10Hzのディスクリート・ロー・パス・フィルタを通過してオシロスコープを駆動します。1mV/DIVに設定されたオシロスコープに、信号はプリアンプ入力を基準として1μV/DIVで表示されます。図H2より、DACの出力ノイズが、約0.9μVのLSBよりも十分に小さいことがわかります。機器の制約により、測定のノイズ・フロアが0.2μVに設定されます。

図H1.マイクロボルトのノイズ測定にはオシロスコープ用に高利得のプリアンプが必要である。プリアンプとディスクリート・フィルタが0.1Hz ~10Hzの測定帯域を設定する

図H2.写真に示された0.1Hz~10Hz帯域のDAC出力ノイズは約0.2LSBに相当する1μV未満である。機器の制約により、測定のノイズ・フロアが0.2μVに設定される

図H3は、ノイズ測定のテスト装置です。関連する信号レベルが、完全にシールドされた同軸経路でブレッドボードからオシロスコープまで配線されていることに注意してください。

図H3.シールドされたDACブレッドボード(前列)、プリアンプ(左)、オシロスコープに接続されたローパス・フィルタ(中央)を含むノイズ測定テスト装置。測定信号経路は、全て同軸

図H4にノイズ測定に適した高感度アンプの例を示します。現世代のオシロスコープが2mV/DIVより高い感度を備えていることは稀ですが、旧式の測定器はより高い能力を提供しています。図には、ノイズ測定に適した代表的なプリアンプとオシロスコープ・プラグインの一覧を示してあります。これらのユニットは、高帯域、低ノイズの性能を提供します。これらの測定器の多くに共通する顕著な特徴は、もはや製造されていないということです。これは、アナログ測定能力よりもデジタル信号の取得に重点を置いた、現在の測定器のトレンドを裏付ける現象でしょう。

| 計測器のタイプ | メーカ | モデル番号 | 最大帯域幅 | 感度/ 利得 | 供給状態 | 注釈 |

| Differential Amplifier | Tektronix | 1A7/1A7A | 500kHz/1MHz | 10μV/DIV | Secondary Market | Requires 500 Series Mainframe, Settable Bandstops |

| Differential Amplifier | Tektronix | 7A22 | 1MHz | 10μV/DIV | Secondary Market | Requires 7000 Series Mainframe, Settable Bandstops |

| Differential Amplifier | Tektronix | 5A22 | 1MHz | 10μV/DIV | Secondary Market | Requires 5000 Series Mainframe, Settable Bandstops |

| Differential Amplifier | Tektronix | ADA-400A | 1MHz | 10μV/DIV | Current Production | Standalone with Optional Power Supply, Settable Bandstops |

| Differential Amplifier | Tektronix | AM-502 | 1MHz | 100,000 | Secondary Market | Standalone with Optional Power Supply, Settable Bandstops |

| Differential Amplifier | Preamble | 1822 | 10MHz | Gain = 1000 | Current Production | Standalone, Settable Bandstops |

| Differential Amplifier | Stanford Research Systems | SR-560 | 1MHz | Gain = 50000 | Current Production | Standalone, Settable Bandstops, Battery or Line Operation |

図H4.適用可能な高感度、低ノイズのアンプの例。互換性、感度、供給状態などのトレードオフがある

モニタ用オシロスコープのトレースはずば抜けた明瞭さを備えていなければなりません。トレースの明瞭性という性能に関しては、高品質アナログ・オシロスコープに並ぶものはありません。これらの測定器のきわめて小さな輝点は低レベルのノイズ測定に最適です。1 DSOに伴うデジタイズの不確実性とラスタ・スキャンの制約が、表示分解能を劣化させます。多くのDSO表示は、ノイズ波形の微細構造を記録することさえできません。

Notes

Note 1: 筆者らの研究から、Tektronixのタイプ453、453A、454、454A、547、556が優れた選択であることが明らかになった。信号本来の状態を保ったトレース表示は、測定対象の小信号を、ノイズ・フロアによって制限されるバックグラウンドと区別するのに最適です。

付録I

電圧リファレンス

図I1にDACで使用する電圧リファレンスのオプション例を示します。自己完結式のものが便利で適用も簡単でしょう。LM199AとLTZ1000Aには外付け回路が必要ですが、より高い性能が得られます。いずれを選択した場合もDACの絶対精度を確立するためにトリミングが必要です。ここでは、最大の安定性を提供するLTZ1000Aについて説明します。

| 型番 | 電圧 | 初期精度 | 温度ドリフト | 長期安定性 | 注釈 |

| LTZ1000A | 7.2V | Minimum 7V Maximum 7.5V |

0.05ppm/°C | 4ppm/Yr Typical | Highest Stability Zener Available. Requires External Heater Control and Reference Buffer Circuitry |

| LM199A | 6.95V | 2% | 0.5ppm/°C | 10ppm/Yr Typical | Self-Contained, Including Heater Control Circuitry. Zener Output Is Unbuffered |

| LT1021 | 5V, 7V, 10V | 0.05V (7V) | 2ppm/°C (7V) | 20ppm/kHr Noncumulative | Fully Self-Contained. Trimmable |

| LT1027 | 5V | 0.02% | 2ppm/°C | 20ppm/kHr Noncumulative | Fully Self-Contained. Trimmable |

| LT1236 | 5V, 10V | 0.05% | 5ppm/°C | 20ppm/kHr Noncumulative | Fully Self-Contained. Trimmable |

図I1.リファレンス・オプションの出力電圧、精度、安定性による比較。最高の安定性が得られるオプションには外付け回路が必要

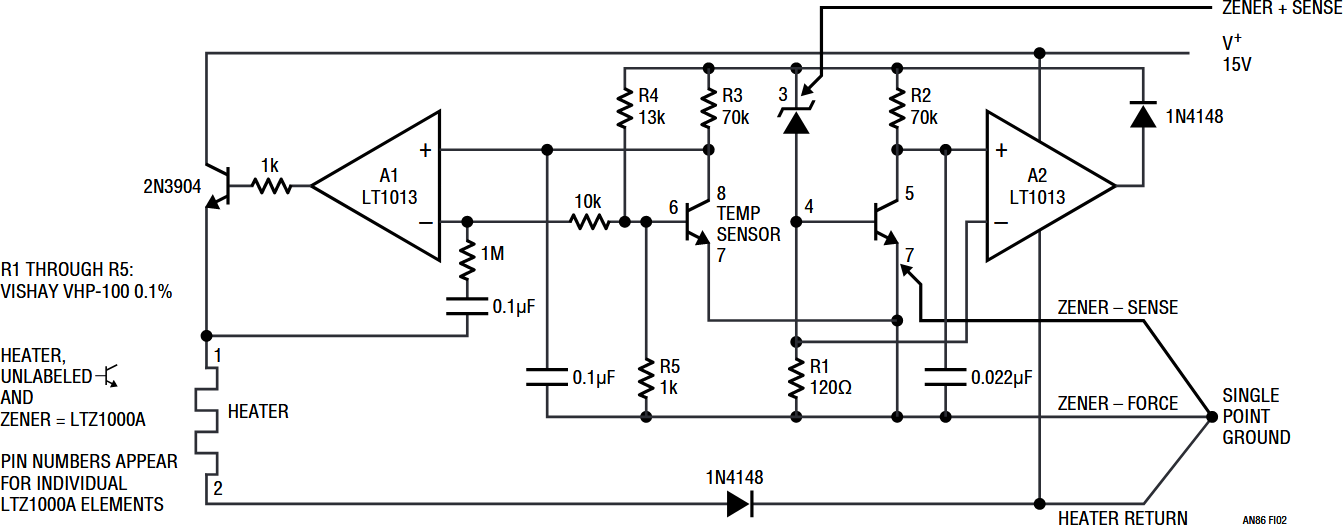

図I2は、LTZ1000Aと、そのサポート回路です。A1はLTZ1000Aのダイ温度を検出し、2N3904を介してICヒーターを適宜制御します。A2はリファレンス電流を制御します。ツェナー・リファレンスの検出にはケルビン接続を使用し、電圧降下の影響を最低限に抑えます。1 点接地によってリターン電流の混合と、生じる可能性のある付随誤差を排除します。

図I2.7VリファレンスはA1:ヒーター制御アンプ、A2:ツェナー電流レギュレータとLTZ1000Aツェナーを含む。ツェナーのケルビン接続と1 点接地に注目のこと

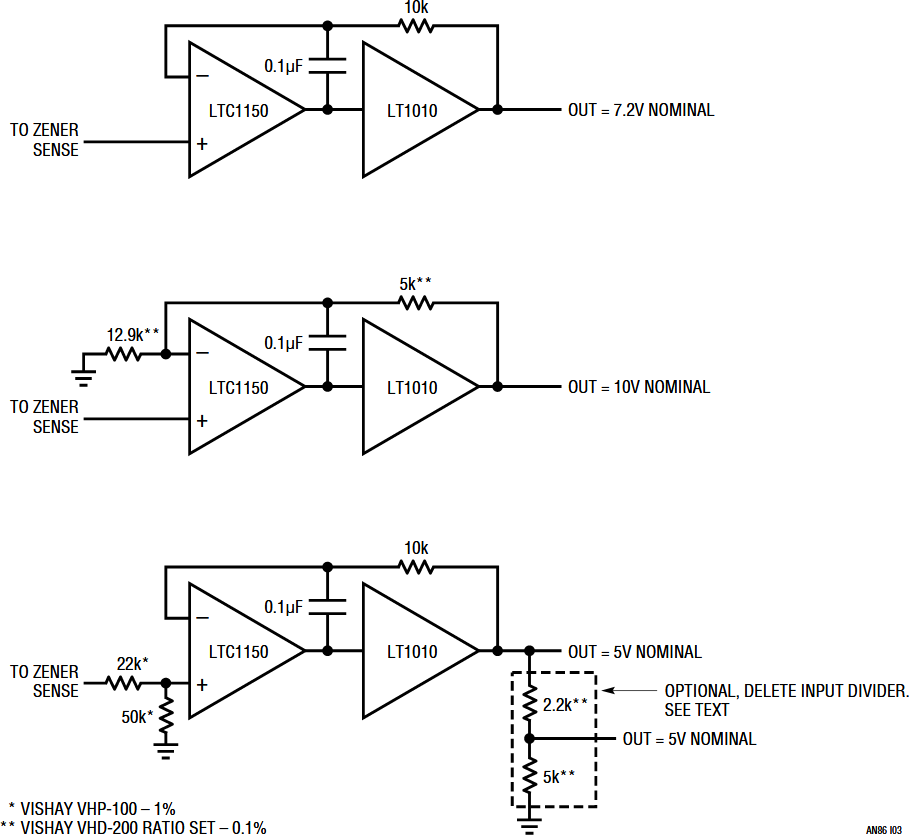

図I3は、リファレンスのバッファ駆動のオプションです。いずれもバッファ出力段によって強化されたチョッパー安定化アンプを採用しています。バッファの誤差は、付録Cで検討しているとおり、ごくわずかです。I3aは単純なユニティ・ゲイン段であり、誤差を小さく、リファレンスへの負荷を最小限に抑えて、入力を出力に伝達します。I3bは中程度の利得を持ち、7Vのリファレンス入力から(この場合)、10Vを出力します。I3cでは、公称7V入力から5Vを得る2つの方法を示しています。一方の方法では、高精度分圧器が若干リファレンスの負荷となり、5V出力はLT1010から取ります。リファレンスの負荷増加は、出力に分圧器を配置し(図にはオプションとして表示)、分圧器の出力からA/Dコンバータのリファレンス入力を駆動することで防止できます。

図I3.チョッパー安定化リファレンス・バッファには(a)ユニティ・ゲイン、(b)10V、(c)5Vの3つの出力オプションがある。絶対精度を確立するためにトリミングが必要である

付録J

ケーブル、接続、ハンダ付け、レイアウト、部品選定、部品選定、隠れた危険と奥義

低レベルの回路の性能では、わずかな寄生効果が顕著で一見説明しがたい影響を及ぼす場合があります。マイクロボルト・レベルの回路に見られる、おそらく最も一般的な障害の原因は、意図せぬ熱電対でしょう。熱電対に関する詳細な議論は付録Cに収録されているため、このセクションの内容の予備検討として目を通してください。

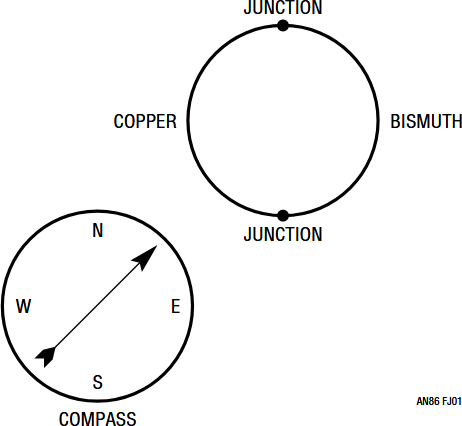

1822年、エストニアの物理学者トーマス・ゼーベックは、ガルバニック配列の熱効果の研究中に偶然、半円形のビスマスと銅の線材を接続して、近くの方位磁石が磁界による外乱を受けることを発見しました(図J1)。ゼーベックは別の金属の組み合わせについても温度をさまざまに変えて実験を繰り返し、相対磁界強度を記録しました。興味深いことに、ゼーベックは電流が流れているとは考えず、この効果を「熱磁界」として説明することを好みました。彼はこの成果を「Magnetische Polarisation der Metalle und Erze durch Temperatur-Differenz」と題する論文に発表します(参考文献参照)。

図J1.ゼーベック博士が「熱磁気」を偶然発見したときに使った実験装置

その後の研究で、「ゼーベック効果」は基本的に電気的な特性であり、再現性があることからきわめて有用であることが明らかになりました。これよりはるかに広く知られたトランスデューサである熱電対は、ゼーベックの末裔です。残念ながら、意図せぬ、好ましくない熱電対も、ゼーベックの血を引いています。

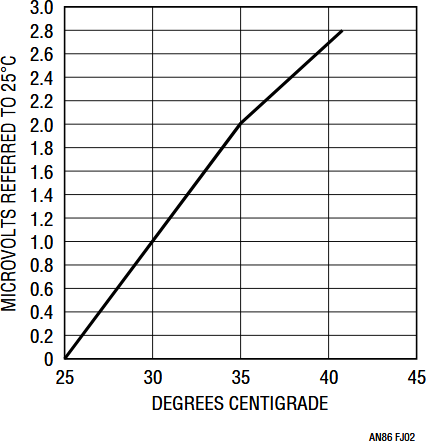

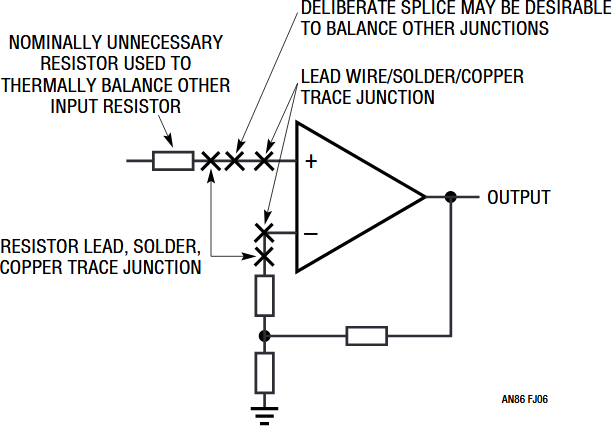

低ドリフト回路では、無用の熱電対がおそらく最も主要な誤差要因になります。コネクタ、スイッチ、リレー接点、ソケット、ワイヤ、そしてハンダまでもが、いずれも熱EMF発生の候補となりえます。コネクタやソケットが熱接合を形成する可能性があることはそれなりに納得できるものの、異なるメーカのワイヤを接続するだけで簡単に200nV/°Cが発生する事実は当たり前では片づけられません。この値は高精度アンプのドリフト仕様の4 倍にも達します。図J2は、このようなワイヤ接続から得られたプロットです。ハンダでさえ、銅、コバール・ワイヤ、PCトレースと接合を形成して低レベル回路では誤差項となります(図J3参照)。図J4に、電子回路アセンブリに使われるいくつかの一般的な材料の熱電対電位を示します。

図J2.2つの「まったく同一」の銅ワイヤであるにもかかわらず酸化と不純物によって発生した熱EMF

図J3.ハンダ- 銅接続による熱EMF。Cd/Snは活性が著しく低いものの毒性があるため入手できず推奨もできない

| 材料 | 熱電位(μV/°C) |

| Cu-Cu | < 0.2 |

| Cu-Ag | 0.3 |

| Cu-Au | 0.3 |

| Cu-Cd/Sn | 0.3 |

| Cu-Pb/Sn | 1 to 3 |

| Cu-Kovar | 40 |

| Cu-Si | 400 |

| Cu-CuO | 1000 |

| 出典:Low Level Measurements,Keithley Instruments, 1984(「参考文献」参照) | |

図J4.各種材料の熱電位から、信号経路に異なる材料を混用すべきでないことがわかる。銅- 銅(表の1 行目)接点は清浄に保たないと酸化によって5000:1の劣化が発生する(表の最後の行)

Cu-CuOの組み合わせが示す著しい反応から、付録Cに述べた(図C7と本文の関連部分)DVMとケルビン・バーレイ分圧器の接点に対するクリーニング措置が必要になります。この図の示す情報が学術的すぎると感じる読者でも、図J5を見ればピンと来るものがあるでしょう。この図は広く普及している実験室用コネクタの熱電位です。一部の種類の熱電対動作は、他の種類の20 倍以上に達します。注意してください。

| 接続タイプ | 説明 | 熱電位(μV/°C) |

| BNC-BNC Mate |  |

0.4 |

| BNC-Banana Adapter |  |

0.35 |

| BNC-BNC "Barrel" Adapter |  |

0.4 |

| Male/Female Banana Mate Sample #1 |  |

0.35 |

| Male/Female Banana Mate Sample #2 |  |

1.1 |

| Male/Female Banana Mate (Type Specified for Low Thermal Activity) Sample #3 |  |

0.07 |

| Copper Lug-Copper Banana Binding Post |  |

0.08 |

| Copper Lug-Standard Banana Binding Post |  |

0.5 |

| Plated Lug-Copper Banana Binding Post |  |

1.7 |

図J5.一般的な実験室用コネクタの熱電位測定値。「バナナ」系のサンプル間で大きな差があるのはメーカの材料選定による。銅製端子/ 銅製バナナ・ポストはメッキ済み端子/ 銅製バナナ・ポストに比べて20×活性が低いことに注目

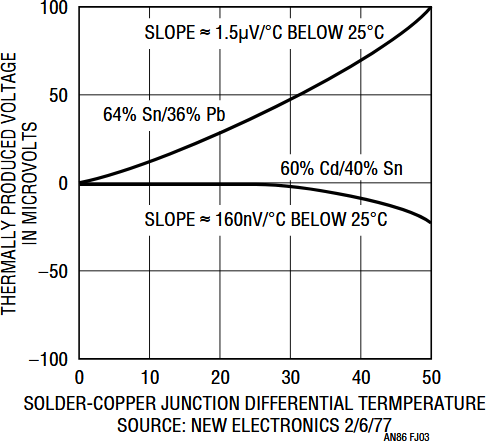

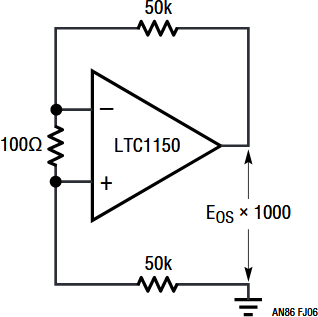

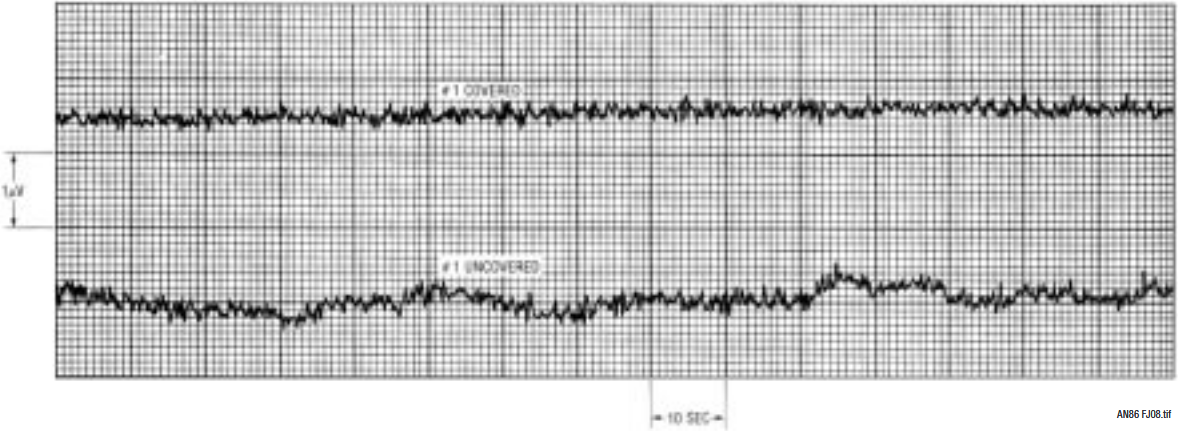

熱EMF起因の誤差は、回路基板レイアウトに十分な注意を払えば最小限に抑えることができます。通常、信号経路内の接点の数を少なくすることは、優れた方針です。コネクタ、ソケット、スイッチ、その他の潜在的誤差要因をできるだけ避けます。しかし、これが不可能な場合もあります。その場合は、信号経路内の接点の数と種類を揃えるように努め、差動動作によって誤差が相殺されるようにします。それには、不可欠な接点によって生じる誤差をオフセットするために、意図的に接点を作る場合もあります。これには微妙な匙加減が必要になることがあります。追加する接点の最適な数と位置を決めるために、繰り返し意図的に温度を変動させる必要があるかも知れません。健全な忍耐力と豊富な時間を注ぎ込んだ実験が不可欠です。標準研究所で使われる手順を借りたこの手法は、熱EMF起因のドリフト低減にきわめて有効です。図J6に、このような熱的バランスを促進するために公称上は必要ない抵抗を導入した簡単な例を示します。離れた場所にある信号源についてはコネクタの使用が不可避な場合もあるでしょう。その場合は、熱EMF効果の仕様値が比較的小さなコネクタを選定し、コネクタから回路基板、回路までの信号配線が同様にバランスの取れたものになるようにします。アンバランスが避けられない場合は、これを相殺する意図的な接点を設けます。いずれの場合も、差動動作する接点は物理的に近接させ、両者が同じ温度になるようにします。空気流や温度勾配を避けてください。これらは、熱のアンバランスを生み、問題を招くおそれがあります。図J7にLTC1150の温度安定性を測定するためのテスト回路における同チップの接続を示します。アンプの入力に接続される抵抗のリード長は同じ長さに揃えてあります。更に、これらの抵抗は対称に接続され、サイズも同一であることから、アンプの各入力側から見た熱容量のバランスも取られています。したがって、熱EMF起因の変位は位相と振幅が等しいため、相殺されます。これだけの措置を講じても、依然としてごくわずかな空気流による影響が現れる場合があります。図J8は、出力ノイズを、小さな発泡スチロールのカップ(HANDI-KUP™社、モデルH8-S)で回路をおおって測定した場合と、カップなしの「静止」空気中で測定した場合の測定記録紙です。このデータは、低レベルの回路では、多くの場合、何らかの形の熱バッフルで囲む慎重さが求められる理由を示しています。

図J6.代表的な熱レイアウト検討項目では寄生熱電対の形成抑制と信号の差動化が重点課題である。アンプ入力部の熱質量を等しくすることで、差動化された寄生熱電対出力を同じ位相と振幅で到達させることができる

図J7.アンプのドリフト・テスト回路。各入力の熱EMFと熱容量は相殺させるために等しくする必要がある

図J8.「静止」空気中での低周波アンプ・ノイズに対する熱バッフルの効果。上側のトレースでは小型のカップでアンプをおおい、下側のトレースではカップでおおっていない。空気の動きが増せば不安定性は悪化する

熱EMFは低レベル誤差要因の第1候補ですが、他にも誤差を生む原因はあります。静電気と電磁界のシールドが必要になる場合もあります。電源トランスの磁界は、アンプのDCドリフトやノイズに間違われることが多い、悪名高い誤差要因です。トランスのPCトレースに注入される磁界は、よく知られた磁界理論に従って、その導体の両端に簡単にマイクボルト・レベルの電圧を発生させます。回路はこのスプリアスな信号と、目的とする入力を見分けることができません。回路応答をロールオフさせることでこの問題を回避する試みは、成功する場合もありますが、好ましくないピックアップ・ノイズのフィルタ後の波形は、しばしばDC成分が不安定であるかのように振る舞います。最も直接的な対策はシールドされたトランスを使用することですが、慎重なレイアウトによっても同程度の効果が得られ、コストを低く抑えることができる可能性があります。高品位の接地方式を実現するために、トランスを近接させて配置する必要がある回路は、トランスの磁界による外乱を受けるおそれがあります。スコープ・プローブの両端にRFチョークを接続することで、トランス磁界の有無やその相対的強度を判断でき、レイアウト試行の参考になります。

寄生誤差のもう1つの要因が浮遊漏れ電流です。このような漏れ電流が回路動作に影響を与えないようにする必要があります。最も単純な対策は、漏れ電流に敏感なノードをテフロン・スタンドオフ越しに接続することです。このノードはPC基板に決して接触しないため、浮遊漏れ電流の影響を受けません。効果的な対策ではあるものの実装は量産向きとは言えない可能性があります。ガード・リングは基板の漏れ電流の影響を抑えるもう1つの手法です。ガード・リングとは漏れ電流に敏感なノードを完全に取り囲むPCトレースです。このトレースは保護対象のノードと同じ電位に駆動し、ガード・リングから「ガードされる」ノードへの漏れ電流が発生しないようにします。PC基板上で、ガード・リングは保護するノードを囲みます。ガード・リングの手法は、付録Cの図C7でコンデンサの表面漏れ電流の影響を排除するために使われています。

参考資料

1. Linear Technology Corporation, “LTC2400 Data Sheet,”Linear Technology Corporation, January 1999.

2. Linear Technology Corporation, “LTC2410 Data Sheet,”Linear Technology Corporation, April 2000.

3. Keithley Instruments, “Low Level Measurements,” Keithley Instruments, 1984.

4. Williams, J., “Testing Linearity of the LTC2400 24-Bit A/D Converter,” Linear Technology Corporation, Design Solution 11, November 1999.

5. Seebeck, T. Dr., “Magnetische Polarisation der Metalle und Erze durch Temperatur-Differenz,” Abhaandlungen der Preussischen Akademic der Wissenschaften (1822–1823),pp. 265–373.

6. Williams, J., “Component and Measurement Advances Ensure 16-Bit DAC Settling Time,” Linear Technology Corporation, Application Note 74, July 1998.

7. Lee, M., “Understanding and Applying Voltage References,” Linear Technology Corporation, Application Note 82, November 1999.

8. Williams, J., “Applications Considerations and Circuits for a New Chopper-Stabilized Op Amp,” Linear Technology Corporation, Application Note 9, August 1987.

9. Huffman, B., “Voltage Reference Circuit Collection,”Linear Technology Corporation, Application Note 42, June 1991.

10. Spreadbury, P. J., “The Ultra-Zener̶A Portable Replacement for the Weston Cell?”IEEE Transactions on Instrumentation and Measurement, Vol. 40, No. 2, April 1991, pp. 343–346.

11. Williams, J., “Thermocouple Measurement,” Linear Technology Corporation, Application Note 28, February1988.

12. Hueckel, J. H., “Input Connection Practices for Differential Amplifiers,” Neff Inst.Corporation, Duarte, California.

13. Gould Inc., “Elimination of Noise in Low Level Circuits,” Gould Inc., Instrument Systems Division, Cleveland, Ohio.

14. Williams, J., “Prevent Low Level Amplifier Problems,” Electronic Design, February 15, 1975, p. 62.

15. Pascoe, G., “The Choice of Solders for High Gain Devices,” New Electronics (Great Britain), February 6, 1977.

16. Pascoe, G., “The Thermo-E.M.F. of Tin-Lead Alloys,”Journal Phys.E, December 1976.

17. Brokaw, A. P., “Designing Sensitive Circuits?Don’t Take Grounds for Granted,” EDN, October 5, 1975, p. 44.

18. Morrison, R., “Noise and Other Interfering Signals,” John Wiley and Sons, 1992.

19. Morrison, R., “Grounding and Shielding Techniques in Instrumentation,” Wiley-Interscience, 1986.

20. Vishay Inc., “Vishay Foil Resistors,” Vishay Inc., 1999.