資料ライブラリ

アプリケーション・ノート使用上の注意

本アプリケーションノートの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、リビジョンが古い場合があります。最新の内容については、必ず最新の英語版をご参照ください。

なお、日本語版のアプリケーションノートは基本的に「Rev.0」(リビジョン0)で作成されています。

AN-1320: ADuCM360/ADuCM361 の自己診断機能

はじめに

ADuCM360/ADuCM361 はCortex™-M3 をベースとした32 ビットのマイクロコントローラで、24 ビットのΣ-Δ 型A/D コンバータ(ADC)を内蔵し、どちらもフル・プログラマブル計装アンプをフロントエンドに内蔵しています。これらのマイクロコントローラは、工業用制御装置や計測器を含む幅広いアプリケーションをターゲットとしています。このようなターゲット・アプリケーション多くは、安全が重視される環境下や故障モードから速やかに復帰するための自己診断機能が重視されます。

このアプリケーション・ノートでは、ADuCM360/ADuCM361とその周辺回路に関する問題を診断するためのADuCM360/ADuCM361 のいくつかの機能について述べます。

診断用電流源

ADuCM360/ADuCM361 には50μA の診断用電流源が組み込まれています。これらの電流源はプログラム可能な励起用電流源とは別のものです。ADC0 とADC1 は別々の独立した診断用電流源を備えています。

診断用電流源は、正入力チャンネル選択(ADCxCON レジスタのビット[9:5])と負入力チャンネル選択(ADCxCON レジスタのビット[4:0])を介してADC 変換用に選択されているアナログ入力チャンネルへ、内部的に接続されます。表1 に示すように、ADCxCON レジスタのビット[11:10]は、正および負のADC 入力への電流源をイネーブルまたはディスエーブルします。

| Bits | Bit Name | Description |

| [11:10] | ADCDIAG | 診断用電流の制御ビット。 00:電流源オフ。 01:選択された正入力で50μA の電流をイネーブル。たとえばAIN0。 10:選択された負入力で50μA の電流をイネーブル。たとえばAIN1。 11:選択された入力で50μA の電流をイネーブル。たとえばAIN0 とAIN1。 |

| 診断テスト | 正常な結果 | 異常な結果 | 異常に関する検出値 | |||

| Register ADCxCON, Bits[11:10], Setting | 電流源の状態 | 内容 | ||||

| 00 | 電流源オフ | 診断用電流をディスエーブルし、AINxとAINy を正常として変換 | 正常な結果 | 該当せず | 該当せず | |

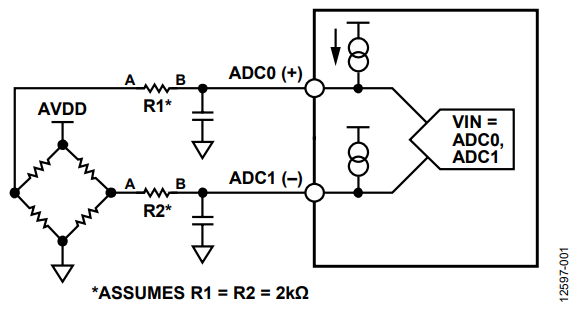

| 01 | AINx の50μA診断用電流源をイネーブル | AINx とAINy を変換 | ADC の電圧がΔV =50μA × R1 だけ変化(たとえばR1 = 2kΩ の場合は~100mV) | AINx とAINy 間の短絡(R1_A とR1_B 間の短絡) | プログラマブル・ゲイン・アンプ(PGA)の設定に関わらずADC 指示値≈0 V | |

| 01 | AINx の50μA診断用電流源をイネーブル | シングルエンドモードで AINx を変換 | AINx の期待される電圧 | AINx の断線または R1 の断線 | PGA が最小設定の場合でも、ADC の指示値は正のフルスケール | |

| 11 | AINx とAINyの両方で50μAの診断用電流源をイネーブル | AINx とAINy を変換 | ADC 指示値がΔV =50μA × (R1 − R2)だけ変化、つまり許容差10%で~10 mV | R1 とR2 の不整合 | ADC 指示値 >予想値の10mV | |

| 1 AINx は正入力チャンネル、AINy は負入力チャンネルです。 | ||||||

たとえば、ADCxCON レジスタのビット11 が0x1、ADCxCON レジスタのビット[4:0]が0x1 の場合は、AIN1 から50μA の電流が流れます。

同様に、ADCxCON レジスタのビット10 が0x1、ADCxCONレジスタのビット[9:5]が0x0 の場合は、AIN0 から50μA の電流が流れます。

図 1 に回路例を示します。

図 1. 診断用電流源を使用した回路例

極めて柔軟なアナログ入力マルチプレクサ

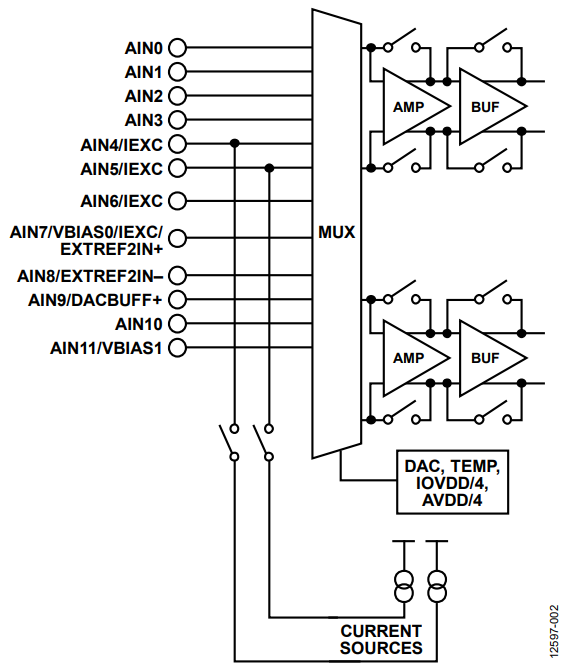

ADuCM360/ADuCM361 に内蔵されているADC は、極めて柔軟なアナログ入力マルチプレクサを備えています。この柔軟なアナログ入力マルチプレクサが、ADC 測定において固定された差動入力ペアによる制約を解消します。任意の外部アナログ入力ピンを差動ペアとして設定することができます。さらに、ADC1 を使用して、差動ADC1 測定用に内部ADC チャンネルの1 つと外部アナログ入力ピンを組み合わせることができます。ADC0 とADC1 は、ともに任意の外部アナログ入力ピンに接続可能です。

極めて柔軟なこのアナログ入力マルチプレクサは、以下のシステム異常のチェックに使用できます。

- アナログ入力ピンの電圧チェック。既知の電源電圧、VDAC 電圧に対するクロスチェック、またはいずれかのAINx ピンに接続した固定外部電圧を基準としたクロスチェック。

- どちらかの ADC の機能チェック(ADuCM360 のみ)。ADC0 で行った測定と同じ入力チャンネルを選択して、ADC1 上で同じ測定を繰り返します。ADC0 経由でADC1の指示値をチェックすることもできます。

- ADC1 経由でデジタルまたはアナログ電源電圧をモニタします。これはバッテリ電源アプリケーションの場合や、電源電圧の低下を検出するのに有効です。

図 2. ADC 入力マルチプレクサ

複数のADC リファレンス・ソース

ADC0 とADC1 に使用できるリファレンス・オプションを表3に示します。これらのリファレンス・オプションはADCxCON レジスタのビット[13:12]で選択します。

| Bits | Bit Name | Description |

| [13:12] | ADCREF | リファレンス選択 00: INTREF-AGND. 01:EXTREF。外部バッファ・モードはADCxCFG レジスタで設定 10:EXTREF2IN(ADC1 でのみ有効)。ADCxCFG レジスタ経由で制御されるEXTREF2IN+バッファ 11: AVDD-AGND |

これらのリファレンス・ソースを使用して、例えば内部リファレンスを使用して測定を繰り返したり、アナログ電源電圧をADC リファレンス・ソースとして使うことにより、外部リファレンス・ソースの安全性をチェックすることができます。

こうした安全性チェックは、いずれかのADC 電圧リファレンス・ソースを使用したADuCM360/ADuCM361 システムの不具合検出を可能にします。

外部リファレンスEXTREF のもう1 つの機能は、レジスタのステータス・ビットによってリファレンス電圧の低下を検出することです。EXTREF に関しては、VREF+およびVREF−間におけるEXTREF のソース電圧が0.4V(代表値)未満になるか0.8V(最大値)未満になると、DETSTA レジスタのステータス・ビット(ビット4)が1 にセットされます。この機能を使用するには、DETCONレジスタのビット8 を1 にセットします。

EXTREF2IN±リファレンス・ソースでは、この機能は使用できません。

フラッシュの内容確認

ADuCM360/ADuCM361 は、フラッシュの読取り/書込み保護機能とともに、シグネチャ生成機能として、最後にプログラムされてから変更されていないフラッシュの内容を確認する機能も備えています。この機能の詳細についてはUG-367 ユーザ・ガイドに記載されています。

フラッシュ完全性シグネチャ機能

このシグネチャはフラッシュ・デバイスの完全性をチェックします。ソフトウェアは、必要に応じて、あるいは新しいコード・ブロックを実行しようとする度にシグネチャ確認コマンドを実行することができます。シグネチャは、多項式x24 +x23 + x6 + x5 + x + 1 を使用する24 ビットの巡回冗長検査(CRC)です。

シグネチャ生成コマンドはシグネチャを生成し、コード・ブロックのシグネチャをチェックします。ブロックは1 ページまたは複数ページとすることができ、シグネチャは24 ビット線形帰還シフト・レジスタ(LFSR)が生成します。ハードウェアは、あるブロックのシグネチャがブロックの最上位ページの上位4 バイトに保存されることを前提としています。これらの4 つのバイトは、シグネチャ生成時には含まれていません。

シグネチャを生成するには以下の手順に従ってください。

- FEEADR0L レジスタとFEEADR0H レジスタにブロックの開始アドレスを書き込みます。

- FEEADR1L レジスタとFEEADR1H レジスタにブロックの終了アドレスを書き込みます。

- シグネチャ生成コマンドをコマンド・レジスタに書き込みます(FEECMD レジスタ= 10)。

このコマンドを実行するとシグネチャ生成レジスタにシグネチャが書き込まれ、このシグネチャが、ブロックの最上位ページの上位4 バイトに保存されたデータと比較されます。このデータとシグネチャが一致しない場合は、ステータス・レジスタにフェイル・ステータスが返されます(FEESTA レジスタ、ビット[5:4] = 10)。

シグネチャの計算中は、フラッシュへの他のアクセスはストールします。128kB ブロックだと32,000 サイクルがストールします。

FEEADR0L レジスタ、FEEADR0H レジスタ、FEEADR1L レジスタ、およびFEEADR1H レジスタはバイト・アドレスですが、識別する必要があるのはページだけです。このハードウェアは下位9 ビットを無視します。

ユーザはユーザ・コードのCRC 多項式を最初に実行してCRC 値を生成し、それからブロックの最上位ページの上位4バイトにその値を書き込む必要があります。この操作の完了後にシグネチャ機能を呼び出すと、常にこの4 バイト値と比較し、シグネチャ・チェック機能の結果として示します。

カーネルの完全性

ハードウェアは、リセット後にカーネルの完全性を自動的にチェックします。不具合がある時は、FEESTA レジスタのビット6 がセットされて、ユーザ・コードを実行できなくなります。このビットは、シリアル・ワイヤ・インターフェースがイネーブルされている場合のみ、シリアル・ワイヤ・リードから読み取り可能です。

すべての外部ピンのESD 保護

ADuCM360/ADuCM361 の各外部ピンは、オペレータや装置取り扱いによる静電放電からデバイスを保護するために、グラウンドまたは電源ラインに対し保護回路を備えています。

このデバイスの過渡電圧に対する耐性の詳細を表4 に示します。これらはADuCM360/ADuCM361 の信頼性レポートに基づいています。

| ESD Model | Package | ESD Test Specification | RC Network | Highest Pass Level | First Fail Level | Class |

| FICDM | 48-lead LFCSP | JESD22-C101 | R = 1 Ω, C = capacitance of the package | ±1500 V | Not applicable | C6 |

| HBM | 48-lead LFCSP | ESDA/JEDEC JS-0012011 | R = 1.5 kΩ, C = 100 pF | ±2500 V | ±3000 V | 2 |

CORTEX-M3 の障害管理機能

Cortex-M3 プロセッサの障害管理システムは、バスやメモリの障害、および未知のインストラクションによる障害を検出します。

これらの障害が発生するとCortex-M3 プロセッサは現在実行中のインストラクションの実行を停止し、所定のメモリ・アドレスへ移動して、対応するユーザ定義の例外ハンドラを実行します。

この例外ハンドラ機能では、ユーザ・コードは障害が発生したシステムにアラートを発し、障害回復のために次のステップへ進むか、ADuCM360/ADuCM361 をシャットダウンすることができます。

主な例外の概要を表5 に示します。

| Number | Type | Prioriity | Description |

| 1 | Reset | -3 (highest) | あらゆるリセット |

| 2 | NMI | -2 | ADuCM360/ADuCM361 の電源モニタに接続されたマスク不能割込み |

| 3 | Hard fault | -1 | 対応する障害ハンドラがイネーブルされていない場合はすべての障害状態 |

| 4 | Memory management fault | Programmable | メモリ管理障害、不正領域へのアクセス |

| 5 | Bus fault | Programmable | プリフェッチ障害、メモリ・アクセス障害、データ・アボート、その他のアドレス/メモリ関連障害 |

| 6 | Usage fault | Programmable | 未定義のインストラクションを実行した場合、あるいは不適切な状態遷移を試みた場合と同じ |

クロックとタイマー

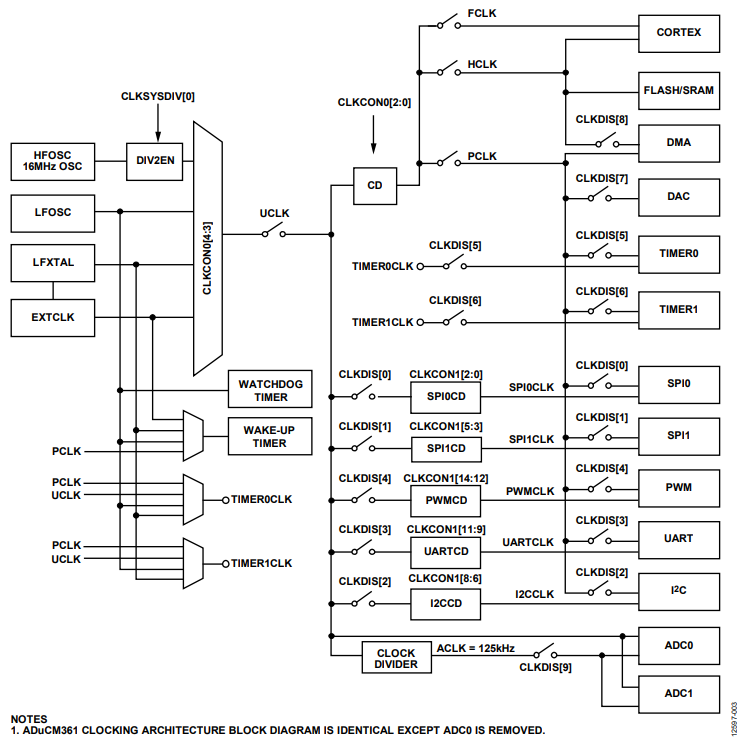

ADuCM360/ADuCM361 には2 つの内蔵発振器と外付けの水晶発振器用の回路が組み込まれています。

- LFOSC は32kHz の低消費電力内蔵発振器で、低消費電力モードで使われます。

- HFOSC は16MHz の内蔵発振器で、アクティブ・モードで使われます。

- LFXTAL は32kHz の外付け水晶発振器です。

- 周辺機能用にイネーブル/ディスエーブルできる省電力クロック・メカニズムです。

クロッキング・アーキテクチャのブロック図

ユーザは、ソフトウェア制御を使用して4 種類の異なるシステム・クロック・ソースを選択し、他のクロック・ソースや内部クロック回路のクロスチェックを行うことができます。

デフォルトでは、内部16MHz 発振器がシステム・クロック(UCLK)ソースです。

ADuCM360/ADuCM361 にはウォッチドッグ・タイマーも組み込まれています。通常、ウォッチドッグ・タイマーはユーザ・コードでイネーブルされ、定期的にリフレッシュします。ユーザ・ファームウェアが期待通りに実行されず、定められた時間内にウォッチドッグ・タイマーをリフレッシュできなかった場合は、ウォッチドッグ・ハードウェアがフル・システム・リセットを実行します。

図 3. ADuCM360 のクロッキング・アーキテクチャ・ブロック図