目的

本連載では、2022年9月の記事「ADALM2000による実習:『CD4007』を使って様々なロジック機能を実現する」を皮切りに、CMOSベースのロジック回路を取り上げています。今回は、Dラッチ(Dフリップフロップ)回路を実際に構成し、その動作を確認します。Dラッチ回路は、トランスファ・ゲートとインバータを組み合わせることによって実現できます。

背景

今回の実習でも、アナログ・パーツ・キット「ADALP2000」に含まれているICを使用してロジック機能を実現します。具体的には、CMOSベースのトランジスタ・アレイ「CD4007」、NMOSトランジスタ「ZVN2110A」、PMOSトランジスタ「ZVP2110A」を使用します。CD4007は、図1に示すように3組の相補型MOSFETで構成されています。各ペアのゲートには共通のピンが割り当てられています(3/6/10番ピン)。また、各PMOSの基板(サブストレート)はすべて正の電源に接続されています(14番ピン)。同様に、各NMOSの基板もすべてグラウンドに接続されています(7番ピン)。図1の右側には、より接続を理解しやすいよう描き直した図を示しています。左側のペアを見ると、NMOSのソース端子がNMOSの基板(7番ピン)に接続されています。一方、PMOSのソース端子はPMOSの基板(14番ピン)に接続されています。残る2つのペアは、より汎用性が高い状態になっています。右側のペアについては、NMOSのドレイン端子とPMOSのドレイン端子がいずれも12番ピンに接続されています。

前回の実習で学んだように、CD4007は多くの用途に利用できる汎用のICです。例えば、CD4007を1個使用することにより、3つのインバータ、1つのインバータと2つのトランスファ・ゲート、NANDゲート、NORゲートなどを構築することが可能です。インバータとトランスファ・ゲートを組み合わせれば、DラッチやDフリップフロップ(main-node D flip-flop)を構築することができます。

静電気放電には要注意

一般に、CMOSベースのICは静電気放電による損傷を受けやすいデバイスだと言えます。CD4007も、その例外ではありません。CD4007は、静電気放電からの保護を実現するためのダイオードを内蔵しています。それでも慎重に扱わなければ損傷してしまう可能性があります。通常、静電気に弱い電子デバイスを扱う際には、帯電防止マットやリスト・ストラップを使用します。但し、そうした適切な実験環境ではなく、自宅で作業を行うといったケースもあるでしょう。その場合、静電気に対応するためのツールまでは準備できていないかもしれません。そうした状況においては、ICに触れる前に自分自身を接地するとよいでしょう。これも、静電気を防止するための簡便な対策になります。CD4007を取り扱う前に、身体にたまった静電気を放電すれば、実験作業の際にチップを壊してしまうのを防ぐことができるでしょう。

準備するもの

- アクティブ・ラーニング・モジュール「ADALM2000」

- ソルダーレス・ブレッドボード

- CMOS アレイ:CD4007(1 個)

- NMOS トランジスタ:ZVN2110A(2 個)

- PMOS トランジスタ:ZVP2110A(2 個)

説明

今回は、図2に示す回路構成によってDラッチの機能を実現します。ご覧のように、2つのトランスファ・ゲートと3つのインバータを組み合わせています。前回の実習で紹介した回路とよく似ていることにお気づきの方もいらっしゃるでしょう。図2の回路でも、2つのトランスファ・ゲートが連携して動作することにより、Dラッチの機能が実現されます。このラッチ回路では、CLKに入力される信号がロー(ロジック・レベルの0)のときに通過フェーズとなります。すなわち、左側のトランスファ・ゲート(以下、TG1)がオンになり、右側のトランスファ・ゲート(以下、TG2)がオフになります。TG1には、2つのインバータが直列に接続されています。それらを介して、入力Dの値が出力Qに伝わります。一方、CLKに入力される信号がハイ(ロジック・レベルの1)のときにはラッチ・フェーズとなります。このフェーズでは、TG1がオフになり、TG2がオンになります。TG1がオフなので、入力Dの変化は出力Qに反映されません。一方、TG2がオンであることから、Qのそれまでのロジック・レベルが、直列接続された2つのインバータをベースとする正のフィードバック・ループ(クローズド・ループ)によって保持されます。つまり、Q出力は前の状態のままになります。図2に示したDラッチ回路をソルダーレス・ブレッドボードに実装してください(図3)。ここでは、CD4007をトランジスタM1~M6として使用します。また、ZVN2110A(NMOS)とZVP2110A(PMOS)を使用し、2つのインバータ(M7/M8の段とM9/M10の段)を構成しています。回路の電源として、ADALM2000からの5Vの固定電圧を供給します。

ハードウェアの設定

まずは、任意波形ジェネレータ(AWG)の2つの出力をDCソースとして設定してください。必要に応じてオシロスコープの各チャンネルを使用し、回路の入力と出力を観察します。5Vの電源は、回路に電力を供給するために使用します。なお、この実習では、-5Vの電源はディスエーブルの状態に設定してください。

手順

ラッチのD入力となる1番ピンと9番ピンに、AWG1の出力を接続します。ラッチのQ出力となる4番ピンと11番ピンには、オシロスコープのチャンネル2を接続してください。また、6番ピンにはAWG2を接続し、CLK入力として使用します。接続/設定が完了したら、5Vの電源を供給してください。なお、信号の表示にはソフトウェア・パッケージ「Scopy」を使用します。

AWGの制御画面を表示し、AWG2を0VDCに設定します。つまり、CLKにローの信号を印加するということです。一方、AWG1は5VDCに設定します。それにより、D入力にハイを印加します。

この状態で、オシロスコープのチャンネル2によってラッチの出力Qを観察しましょう。オシロスコープの画面には、5Vの安定したDC電圧が表示されるはずです。図4のようなスクリーンショットを取得しておいてください。

続いて、AWG1を0VDCに設定します。それにより、D入力にはローが印加されます。その状態でオシロスコープを使って出力を観察してください。この状態は、ラッチの通過フェーズに相当します。そのため、オシロスコープのチャンネル2には0VDCが表示されるはずです。次に、AWG2を5VDCに設定します。それにより、CLKにはハイが印加されます。続いてAWG1を5VDCに設定し、D入力にもハイを印加してください。

その状態でQ出力をオシロスコープで観察します。D入力はハイに変化するはずですが、それまでDの値はローだったので、出力にはローの信号が表示されるはずです。その状態でスクリーンショットを取得してください。これにより、ラッチ・フェーズの動作を確認できたことになります。

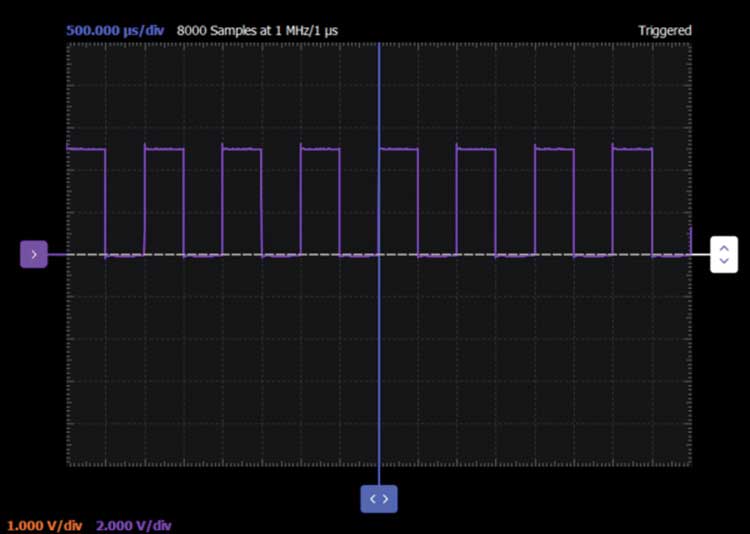

続いては、AWGの両チャンネルの設定を変更し、ピークtoピークの振幅が5Vの矩形波が出力されるようにします。周波数については、AWG1が1kHz、AWG2が2kHz(AWG1の周波数の2倍)としてください。また、AWG2の位相は0°に設定しましょう。つまり、両AWGから同期がとれた信号が出力されるようにします。

CLK入力とD入力に対するQ出力の変化をオシロスコープで観察してください。様々な波形を試してスクリーンショットを取得し、実習レポートにまとめておいてください。

続いて、AWG2の位相を90°に設定します。ここまでと同様に、CLK入力とD入力に対するQ出力の変化をオシロスコープで観察してください。AWG2の位相が0°の場合と比べてどのように変化しているでしょうか。また、なぜそのような結果になるのでしょう。様々な波形を試してスクリーンショットを取得し、実習レポートにまとめておいてください。

練習問題

入力信号と出力信号の関係を見ると、1個のDラッチによって、クロック周期の1/2の遅延が生じることがわかります。2個のDラッチを直列に接続し、逆位相のクロックを使用すると、1クロック周期の遅延を実現することができます。どのようにすればこのようなDフリップフロップ(main-node D flip-flop)を実現できるのか、具体的な回路構成を考えてみてください。

CD4007をもう1つ使用できる場合には、追加の実習としてDフリップフロップを実際に構築してみてください。

その他の回路構成

図2のDラッチ回路は、NMOSとPMOSのトランジスタを組み合わせた相補型のトランスファ・ゲートを使用することで構成しています。NMOSまたはPMOSトランジスタ単体でもトランスファ・ゲートの機能を実現できますが、ハイとローの両方のロジック・レベルを同じ強度(つまり、オン抵抗が同等の値の状態)で伝送することはできません。NMOSトランジスタを単体で使用した場合、ローの信号は強度の高い信号として伝送できますが、ハイの信号の強度は弱くなります。逆に、PMOSトランジスタを単体で使用した場合には、ハイの信号の強度は高くなり、ローの信号の強度は弱くなります。

ICの設計では、基本的に内部の回路ブロックの間で内部信号を転送するケースについて考慮するだけで済みます。NMOSまたはPMOSトランジスタ単体をトランスファ・ゲートと使用した場合でも、ハイとローの駆動強度に差が出るということは大きな問題にはなりません。その観点から重要な役割を果たすのは、ラッチが備える正のフィードバック・ループです。図2の回路では、10個のトランジスタを使用しています。実際には、トランスファ・ゲートとしてPMOS/NMOSを単体で使用することにより、トランジスタの数をわずか6個に削減できます。それだけで、簡素化されたDラッチを構成することが可能です。例えば、図8に示した回路であれば、立上がりエッジでラッチを行うことができます。一方、図9に示した回路では、立下がりエッジでラッチが行われます。

ハードウェアの設定

図8、図9の回路をブレッドボードに実装してください。それぞれ、図10、図11に示したようなボードを構成することになります。

説明

ソルダーレス・ブレッドボードに変更を加える際には、必ず5Vの電源をオフにしてください。まずは、ブレッドボードの回路を図2の状態から図8のように変更します。その上で、5Vの電源を投入してください。先ほどの例と同じように、AWG1をD入力、AWG2をCLK入力に接続します。ラッチとしての動作を観察し、入力クロックの適切なエッジでローとハイの両方の入力がラッチされることを確認してください。

ソルダーレス・ブレッドボードに変更を加える際には、必ず5Vの電源をオフにしてください。まずは、ブレッドボードの回路を図2の状態から図8のように変更します。その上で、5Vの電源を投入してください。先ほどの例と同じように、AWG1をD入力、AWG2をCLK入力に接続します。ラッチとしての動作を観察し、入力クロックの適切なエッジでローとハイの両方の入力がラッチされることを確認してください。

コンポーネントの選択肢

ここまでの例では、4個のNMOS/PMOSトランジスタ(ZVN2110AとZVP2110A)を使用してインバータのペアを構成していました。それらについては、CD4007をもう1個使用する方法で実装することもできます。あるいは、「74HC04」や「CD4049」のように、CMOSインバータを6個集積したICを使用することも可能です。

問題

Dラッチの主な用途(アプリケーション)を挙げてください。

答えはStudentZoneで確認できます。