目的

今回は、CMOS(Complementary MOS:相補型MOS)トランジスタで構成したアンプ回路を取り上げます。具体的には、高いゲインを実現する反転アンプについて検討します。

準備するもの

- アクティブ・ラーニング・モジュール「ADALM2000」

- ソルダーレス・ブレッドボード

- ジャンパ線

- 抵抗:100kΩ(3 個)、10kΩ(1 個)、4.7kΩ(1 個)

- コンデンサ:22µF(2 個)、1µF(2 個)、10pF(1 個)

- CMOSインバータ:「CD4069A」、「CD4069UB」、「CD74HCU04」、「CD4007」のうちいずれか(1 個)

背景

図1に示したのは、CMOSトランジスタで構成したインバータの回路です。ご覧のように、1個のPMOSトランジスタ(M1)と1個のNMOSトランジスタ(M2)で構成されています。多くの場合、CMOSインバータは反転素子として使われますが、ゲインの高いアンプ回路(反転アンプ)だと見なすこともできます。一般に、CMOSの製造プロセスは、NMOSとPMOSの閾値電圧VTHがほぼ等しくなるように制御されます。その結果、相補型のMOSトランジスタ回路が実現されます。CMOSインバータの場合、NMOSトランジスタとPMOSトランジスタのゲートの幅と長さの比(W/L)を調整し、両方のトランスコンダクタンスも等しくなるように設計されます。

説明

まず、図2に示すごく単純な回路を構成します。これを使って、シンプルなCMOSアンプの入出力信号を観察し、伝達関数を確認してみます。まず、ADALM2000の正の電源Vp(5V)をCMOSインバータIC「CD4007」のVDD(14番ピン)に接続し、グラウンドをGND(7番ピン)に接続します。ピン番号については図3を参照してください。また、インバータの入力(1番ピン)とオシロスコープの入力(1+)に任意波形ジェネレータ(AWG)の出力(W1)を接続します。そして、インバータの出力(2番ピン)をオシロスコープの入力(2+)に接続してください。CD4069A(UB)を使用する場合には、VSS(7番ピン)をグラウンドではなくボードの負電源Vnに接続しても構いません。同ICは、5Vより高い電源電圧にも対応するからです。

ハードウェアの設定

図4に、図2のCMOSアンプ回路を実装したブレッドボードを示しました。

AWGは、ピークtoピークの振幅が4V、オフセットが2.5V、周波数が1kHzの三角波を生成するように設定します。オシロスコープの両チャンネルは1V/divに設定してください。なお、CD4069AをVpとVnに接続している場合には、ピークtoピークの振幅を8V、オフセットを0Vに設定します。

手順

図2のアンプ回路について、出力の勾配を測定し、DCゲインを計算します。それには、出力振幅の中心(約2.5V)において、入力電圧の変化に対する出力電圧の変化の比を算出します。反転アンプであることから、算出した値は負の値になることに注意してください。

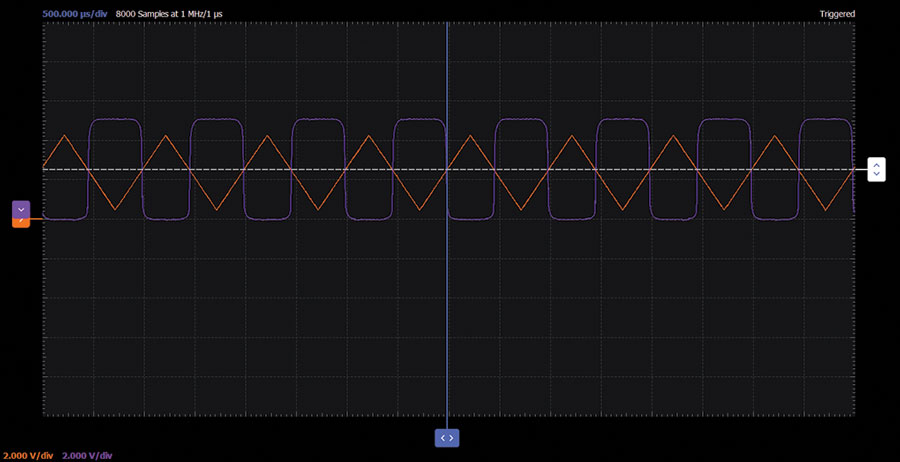

オシロスコープ機能による信号の表示にはソフトウェア・パッケージ「Scopy」を使用します。取得した信号波形の例を図5に示しました。

負帰還経路の追加

続いて、CMOSインバータの入出力に負帰還経路を追加します。つまり、単一段のアンプ回路を構成します(図6)。

ハードウェアの設定

図7に示したのが、図6の回路を実装したブレッドボードです。

AWGは、ピークtoピークの振幅が2V、オフセットが0V、周波数が1kHzの正弦波を生成するように設定します。

手順

アンプ回路の入力にAWGの出力を印加し、回路全体のゲインを10kHz~100kHzの範囲で測定します。ネットワーク・アナライザ機能を使用し、ボーデ線図を取得してください。つまり、周波数を横軸とし、回路全体のゲインと位相をプロットするということです。

ここでは、LTspice®で取得したシミュレーション結果を示しておきます(図8)。

段数を増やしてゲインを高める

次に、段数を増やすことによって更にゲインを高めてみます。具体的には、図9のような3段構成のアンプ回路を例にとります。

ハードウェアの設定

図9の回路を実装したブレッドボードを図10に示しました。

AWGは、ピークtoピークの振幅が2V、オフセットが0V、周波数が1kHzの正弦波を生成するように設定します。

手順

アンプ回路の入力にAWGの出力を印加し、10kHz~100kHzの範囲で回路全体のゲインを測定します。ネットワーク・アナライザ機能を使用し、ボーデ線図を取得してください。

図11にLTspiceによるシミュレーション結果を示しました。

その他の回路

最後に、CMOSインバータをベースとするより高度な回路を紹介します。

チョッパ・アンプ

CMOSインバータを利用すれば、チョッパ・アンプを構成することができます。ここでは、インバータを6個内蔵するCD4069A(UB)を利用します。同ICは、バッファを内蔵していない製品です。これに、クワッド・タイプのアナログ・スイッチ「CD4066」を組み合わせて、図12の回路を構成します。この回路の左下にある2個のインバータは、方形波とその相補波形を生成します。それらによって、各スイッチ(CD4066)を制御します。図中のスイッチAと同Bは、入力用の単極双投(SPDT)スイッチとして機能します。同様に、スイッチCと同Dは、出力用のSPDTスイッチとして働きます。図の中央にあるインバータは、図6の回路と同様にAC結合のアンプ回路として使用しています。

この回路を動作させると、入力信号が入力側のスイッチによって変調されます。その信号がAC入力のアンプ回路によって増幅され、出力側のスイッチによって復調されます。出力部の20kΩの抵抗と560pFのコンデンサはローパス・フィルタとして機能します。その役割は、出力信号の周波数リップルを最小限に抑えることです。

問題

- 図 6 の回路の場合、インバータの出力に現れるゲインはいくつになるでしょうか。入力(W1)に対するインバータ出力のゲインを算出してください。

- 図6の回路のゲインを決めるのは、どのコンポーネントですか。

答えはStudentZoneで確認できます。