Abstract

There are many different analog-to-digital converters available today including discrete ADCs and ADCs integrated into digital ICs such as microcontrollers, processors and FPGAs. What ADC is best for your application? Do you need the highest precision, a simple housekeeping check, or something in between? What sample rate is sufficient. This application note all of those things. It also highlights the latest state-of-the-art SAR, delta sigma, pipeline and integrated ADCs.

How important are speed, power, and accuracy of the signals that you are measuring? What are your choices? With so many different analog-to-digital converters (ADCs) available, how do you pick one?

There are stand-alone (or discrete) ADCs ranging from 8 bits up to 24 bits typically, and even some with 32-bit options. ADC cores are also integrated into microcontrollers, FPGAs, processors, or complete systems on chips (SoCs). There are successive approximation register (SAR) ADCs and sigma-delta versions.1 Pipeline ADCs are used when the highest sample rate speed is needed. Some ADCs sample down to about 10 samples per second and some well above 1Gsps. ADCs range in price from < $1 to $265 or more.2 Some of the 1,000-piece listings for pipeline ADCs are largely quite below the published "1k" price.

To help you choose the right, or the best ADC for your application, we will take a closer look at these various types and explain their optimal operating conditions.

SAR ADCs–for Midrange Speed and Snapshot Data

SAR ADCs offer a wide range of bits and sample rates, or speed. Ranging from 6 or 8 bits to as much as 20 bits, SAR ADCs typically operate between a few kilosamples per second (ksps) to as much as 10 Megasamples per second (Msps). SAR ADCs are a good choice for midrange speed applications such as motor control, vibration analysis, and system monitoring. These are not as fast as pipeline ADCs, but they are typically faster than delta-sigma ADCs (uses of both are also discussed below).

When might a customer want this? When you need to measure multiple signals simultaneously, you can simultaneous sample with multiple single SAR ADCs, or use a simultaneous-sampling ADC with multiple ADCs or multiple track-and-hold (T/H) cores inside it. This allows the system to measure the multiple analog inputs at the same instant.3, 4

SAR ADCs scale the power dissipation linearly with the sample rate. For example, a SAR ADC that dissipates 5mW at 1Msps typically dissipates just 5µW at 1ksps. Consequently, SAR ADCs are very flexible and a customer can stock one part number for multiple applications.

There is another advantage for SAR ADCs: they take a "snapshot' of the analog input signal. A SAR architecture samples (i.e., "grabs") just a single moment in time. (Later, we explain how this snapshot differs from delta-sigma ADCs that sample the analog input many times.)

Current and voltage transformers use a SAR ADC for a protection-relay application. Here, the customer measures the different current and voltage phases at the same instant. An electrical utility is a good example. With precise snapshot data, the utility knows exactly what is coming down the electrical lines and how to manage the power grid most effectively.

Sigma–Delta ADCs–for Higher Accuracy from More Bits

When you want the accuracy from more sampling bits or really need the highest effective number of bits (ENOB), sigma-delta ADCs are usually the best choice, especially for low-noise precision applications. When speed is not as critical, the oversampling and noise shaping of a sigma-delta ADC affords very high precision.

What applications might need > 20 bits of noise-free resolution? Instrumentation units and gas chromatographs or the oil and gas industries are example applications that typically want–even demand–precision from as many bits as possible. These are system applications that set the benchmark for precision analog signals, the applications where end users must be absolutely sure of their data–exactly how much sweet crude or natural gas is flowing.

As the SAR ADC market started to become saturated 5 to 10 years ago, companies such as Maxim Integrated, Analog Devices, Texas Instruments, and Linear Technology all invested in multiple sigma-delta cores. The result today is very good ADCs up to 24 or 32 bits and with sample rates between 10sps to a few Msps.

Modulator or Not?

Sigma-delta ADCs have become more difficult to classify in terms of speed and sample rates.

Traditional sigma deltas did all of the digital post-processing internally (e.g., with SINC/notch filters, decimation, and noise shaping). From there, data was sent out serially with very good ENOB. For example, if you had a 24-bit ADC, the data output included 24 bits. The first bit output was the most significant bit (MSB) and the 24th bit was the least significant bit (LSB). Your data output rate was typically the serial clock rate divided by 24. These were not the fastest, nor the most flexible ADCs.

In the last 5 to 10 years, however, sigma-delta modulators have become more popular, particularly in applications that need a good amount of speed (often around 1Msps or more). Rather than waiting until the full 24-bit output has been decimated, the sigma-delta modulator streams out the data one bit at a time and leaves the digital filtering for analysis in the processor or FPGA.

This modulator flexibility is helpful for an application such as motor control, where 12 to 16 bits isn't sufficient. Here the motor controller might not need or want to wait for the last 8 LSBs in a 24-bit data stream if the first 16 bits provide a sufficient amount of analog measurement.

In more recent years, sigma-delta modulators have been reaching up to 16 bits and 20Msps.

Choose SAR vs. Sigma Delta–the Determinant Is Speed

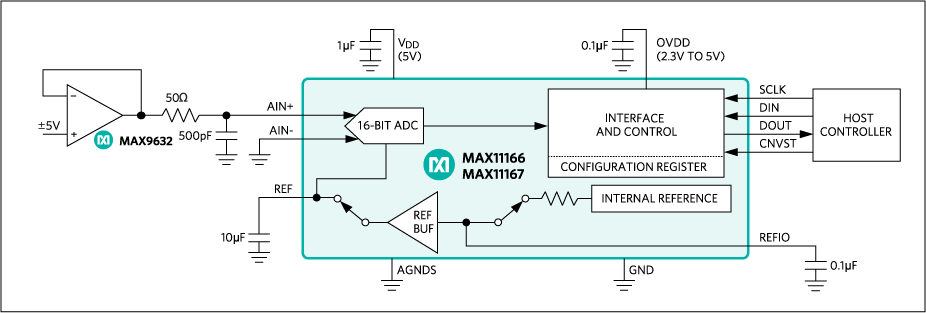

Input filters are another important consideration when choosing the right ADC for your application. Recall that the SAR architecture takes a high-speed snapshot. When an application pushes to the higher sampling rates (100ksps and above), the input filter becomes more complex. Often then, an external buffer or amplifier is needed to drive the input capacitor and settle in a short period. This means that the amplifier must have sufficient bandwidth. Figure 1 shows this example with the 16-bit, 500ksps MAX11166 SAR ADC. The higher the bits and the faster the sample rate, the shorter the time constant that the input has to settle for a correct input reading.

Figure 1, uses the MAX9632 amplifier with 55MHz gain bandwidth and is followed by a simple RC filter. This particular amplifier offers < 1nV/root-Hz noise, making it possible to get every tenth of a dB of ENOB from the system.

Figure 1. SAR ADC (MAX11166/MAX11167) input filter example shows the MAX9632 amplifier with 55MHz gain bandwidth driving the ADC input.

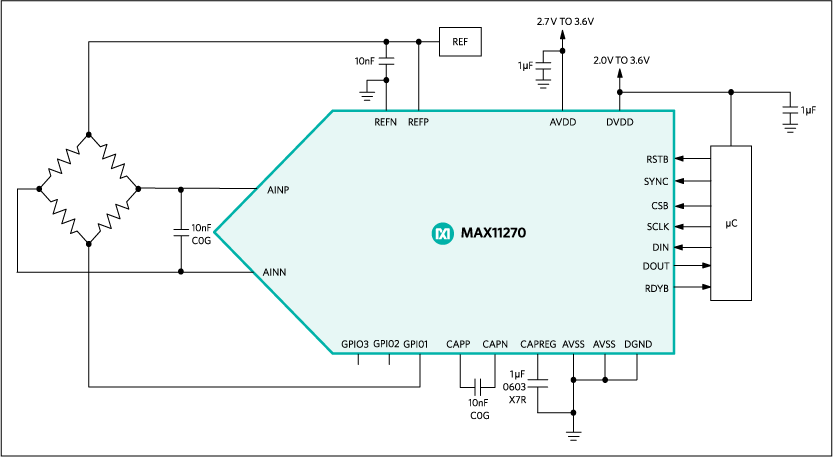

Compared to SAR ADCs, the input in a delta-sigma ADC is oversampled so many times that the anti-aliasing filter requirements usually are not as strict. Often, a simple RC filter suffices. Figure 2 is an example with the MAX11270 24-bit, 64ksps sigma-delta ADC. Here, a Wheatstone bridge example is shown with a 10nF capacitor between the differential inputs.

Figure 2. Sigma-delta ADC (MAX11270) input filter example requires a simple RC filter externally.

Pipeline ADCs–for Super-Fast Sampling

In the introduction we mentioned pipeline ADCs as important for the highest sample rates such as RF applications and software-defined radios.

Top analog companies have been heavily investing research and development (R&D) into pipeline ADCs over the last 10 to 15 years. Analog Devices has long dominated this market, but Texas Instruments and Linear Technology have come on strong in recent years. There are a few more niche players, but none have made serious inroads into the advances of these three IC manufacturers. The top two figures of merit for pipeline ADCs are speed and power. With sample rates between about 10Msps up to a few Gigasamples per second (Gsps), these ADCs serve applications like software-defined radios, radar, communications, base stations, and others that need super-fast sampling. And if blazing-fast speed is the main criterion for pipeline ADCs, then the interface to the ADC becomes even more critical.

The next big battlefield in pipeline ADCs is likely to be based around the digital interface between the ADC and processor or FPGA. Parallel digital interfaces have been the historical interface of choice because you can stream a lot of converter bits out in a short period of time. A serial LVDS interface has served in applications, such as ultrasound, that have a large number of channels and where sample rates between 50Msps and 65Msps have historically been sufficient.

JESD204B Serial Interfaces

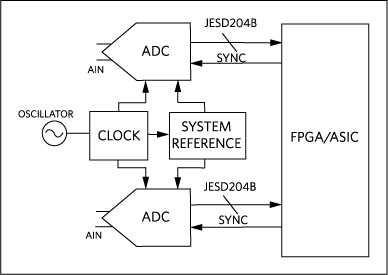

A JESD204B serial interface is a high-speed serial standard up to 12.5Gbps. This interface emerged in recent years thanks to the analog companies mentioned above and digital companies such as Xilinx, Altera, Freescale, and others. Using the JESD204B interface, the ADC makers have pushed their sample rates higher and higher, as have the FPGA and processor companies with their serial transceivers, also known as serializers/deserializers (or SerDes).

These faster data rates make it possible to get more data through in a shorter amount of time and with fewer PCB connections. Consider a multichannel application with many ADCs in parallel, a rat's nest of wiring, between the ADC and the FPGA/processor. With JESD204B serial interfaces, the number of data lines is reduced dramatically and board space is preserved. Figure 3 shows how only a single serial output pair and sync input is used, greatly reducing the number of input/output (IO) pins required in both the ADC and the FPGA/processor.

Figure 3. JESD204B serial interface greatly reduces the number of data lines between the ADC and the FPGA/processor.5

Note that plenty of articles have been written on JESD204B in recent years and more in-depth details can best be found in other articles.

Critical Concern of Power with Pipeline ADCs

Now that more ADCs can be packed in a tight space, power becomes even more of an issue. This is why the leading ADC manufacturers are always battling to reduce power. Power largely depends on bits, speed, and AC specifications such as signal-to-noise ratio (SNR) and spurious-free dynamic range (SFDR). A good rule is 1mW per 1Msps. If your ADC is close to that, you have a good starting point.

ADCs Optimized for Microcontrollers, FPGAs, Processors, and SoCs

ADCs in Microcontrollers

In years past, selecting the best ADC to embed in a microcontroller was not a simple task. ADCs integrated into micros have not typically been the highest quality. Historically, when a 12-bit ADC was embedded in a micro, it was much more likely to perform like an 8-bit ADC in terms of effective number of bits (ENOB) or linearity. Similarly, a 16-bit ADC might operate more like a 12-bit ADC. To ensure adequate ADC performance for an application, users definitely had to carefully review specifications in data sheets and then determine which were guaranteed. It was not uncommon to see only ADC typical specs or minimum and maximum specs with incomplete conditions listed.

Recently, ADC performance such as integral nonlinearity (INL), differential nonlinearity (DNL), gain error, and ENOB has improved enough to enable quality ADC readings for some micros. Not surprisingly, the number of micros with integrated ADCs has grown considerably.

Today, if the application needs 12 bits or less and only a few channels, a micro's ADC–typically a SAR or delta sigma–is likely to be the most cost-effective solution. Examples where a micro ADC is likely sufficient include housekeeping applications such as monitoring a power supply, or less accurate temperature sensing such as measuring a diode.

ADCs in FPGAs, Processors, and SoCs

FPGAs manufacturers have also begun to integrate ADCs into their systems. Xilinx, for example, offers a 12-bit, 1Msps ADC in all of their 28nm (7 Series) FPGAs and Zynq®SoCs. There are also a wide variety of processors and SoCs with integrated ADCs. 10 or 12 bits and up to 1Msps are common specifications where the ADC is included.

The board position of an ADC for an FPGA, processor, or SoC is a critical decision. Many processor systems like a programmable logic controller (PLC) have separate analog boards and digital boards. Locating the ADC on a specific board can become an issue. The CPU module typically holds the FPGA or SoC, but the analog-input signals can be on a completely separate card with a high-speed digital backplane connecting the two. You are not going to route sensitive analog across such a connection, so integrating an ADC in the FPGA, processor, SoC (or micro) is no help in this case. This is where you definitely want a good discrete ADC, with 24-bit sigma-delta ADCs as the most common choice in PLC applications.

Staying with the PLC example, isolation is another element to consider. The majority of PLC analog inputs include some form of isolation, typically digital. Many analog-input modules integrate low-cost micros (< $2 to $3, U.S.) for fast responses and quick interrupts. Now the location of the isolation dictates whether an internal ADC is feasible. If the isolation sits between the processor (or micro) and the backplane, an ADC integrated into the micro is your friend. If the micro needs to be isolated from the high-voltage input signals, then a discrete ADC and a digital isolator is the best solution.

What Is Your Best Choice?

After reviewing several ADC options, we come back to our original questions: how important are the speed, power, and accuracy of the signals you are measuring, and how do you pick one?

It depends. Though digital designers and power-supply experts tasked with picking the right ADC prefer more explicit instructions, ADCs are often complex, nuanced ICs that require investigating the data sheet and evaluation (EV) kit.

- If you have a reasonably fast signal like a vibration analysis of a motor humming along at greater than 1,000 revolutions per minute, a SAR ADC is likely the best.

- If your application is low speed (close to DC) like a slow-moving temperature signal, a sigma-delta ADC is likely the best.

- If the only need is a simple low-resolution reading for a housekeeping function, the integrated ADC in a micro, FPGA, processor, or SoC can probably do the job.

- If the application must measure the fastest analog signals in the world, then a pipeline ADC is the best choice.

While the analog companies continue to innovate, these specifications move faster in speed, lower in power, and possibly lower in price. Table 1 summarizes the typical minimum and maximum specifications for ADCs on the market today.

| ADC Architecture/Specs | Sample Rate/ Speed | Resolution/Bits | Price | Power |

| SAR | DC to 10Msps | 8 to 20 | Low to medium | Lowest per ksps |

| Sigma Delta | DC to 20Msps* | 16 to 32 | Low to medium | Low to medium |

| Pipeline | 10Msps to 5G sps | 8 to 16 | Highest | Highest |

| Integrated in µC/ Processor/FPGA/SoC | DC to 1Msps | 8 to 16 | Lowest | Low to medium |

| * Modulator output speed | ||||