AN-352: 如果使用得当,高速比较器可提供许多有用的电路功能

问:为什么高增益或开环配置中不能使用标准运算放大器作为电压比较器?

如果您能接受数十微秒的响应时间,而且您还要求低偏置电流、高精度和低失调电压,那么运算放大器可能确实比大多数标准电压比较器更佳。但是,为使反馈稳定,大多 数运算放大器具有内部相位/频率补偿,因此难以获得纳秒级响应时间。另一方面,颇受欢迎的低成本比较器LM311则具有200 ns的响应时间。

此外,运算放大器的输出并不能轻松地与标准逻辑电平相匹配。如果没有外部箝位或电平转换,用作比较器的运算放大器的摆幅将达到正负电源的数伏范围内,从而与标准TTL或CMOS逻辑电平不兼容。

我的比较器不受控制地振荡。为什么会这样?

请检查电源旁路。电源线上即使只有几英寸的PC走线,也可能会使直流电阻和电感增加到不可接受的程度。因此,输出切换时的瞬变电流可能会导致电源电压波动,并通过 地线和电源线反馈至输入端。请尽可能靠近比较器电源引脚安装低损耗电容(0.1μF陶瓷电容),它在高速切换时将起到低阻抗储能库的作用。

我已安装旁路电容,但仍然无法使高速比较器停止振荡。现在是什么问题呢?

可能是比较器接地问题。请确保接地引线尽可能短,并与低阻抗接地点相连,使通过引线电感的耦合最小。如有可能,请使用接地层,避免使用插座。振荡的另一个原因可 能是高源阻抗以及输入端的杂散电容。几千欧姆的源阻抗和数皮法的杂散电容就可能导致极难控制的振荡。保持引线最短,包括示波器探头的接地夹。为获得最佳测量结果,请使用尽可能最短的接地引线,使其电感最小(<1")。

采用缓慢移动的输入信号时,我的比较器在经过跃迁电压时似乎在"震颤"。为何无法从该器件获得单一、干净的跃迁?

此问题的原因通常在于比较器的高增益和宽带宽。任何噪声都会被放大;当信号经过跃迁区时,噪声可能会导致快速响应的放大器输出来回跳动。此外,该器件的灵敏度(即增益)在跃迁期间较高,因此反馈导致的振荡倾向会增大。如有可能,请对信号进行滤波,将伴随噪声降至最低。

然后尝试使用迟滞;像齿轮传动中的间隙一样,迟滞要求输入变化达到一定量,才能发生反向。例如, AD790发生 由高至低的跃迁之后,其内置的迟滞功能要求输入电压(正输入)提高500 μV才能产生低至高的跃迁。

如果我的比较器没有内部迟滞功能,我可以从外部添加吗?

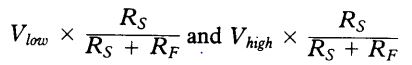

是的,可以利用外部正反馈添加。将比较器输出的一小部分反馈至正输入即可实现。图1显示了这一简单技术。从低跃迁点到高跃迁点的迟滞电压取决于反馈电阻 RF、源电阻 RS、低输出电平 Vlow 和高输出电平 Vhigh。低跃迁点和高跃迁点由以下公式确定:

图1. 对比较器应用外部迟滞。

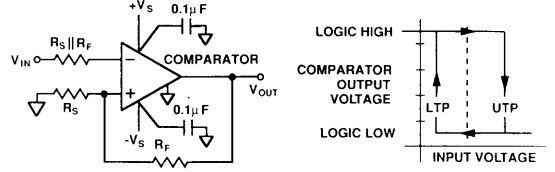

图2显示,添加外部迟滞如何使比较器的响应变得"干净"。图2a显示具有双极性输出摆幅但无迟滞的比较器响应。当三角波输入(迹线A)经过跃迁点(地)时,该器件激烈振荡(并将一部分振荡耦合至地和信号源)。图2b显示同一比较器应用5 mV外部迟滞后的响应,此时跃迁干净得多。

图2. 迟滞有助于比较器获得干净的响应。

使用外部迟滞的问题是输出电压取决于电源电压和负载。这意味着,迟滞电压会因应用不同而异。虽然这会影响分辨率,但迟滞通常只占该范围的极小一部分,而且安全余 量可以达到计算结果的两到三倍,所以并不是一个严重问题。换用几个比较器可以帮助您确立对安全余量的信心。反馈请勿使用绕线电阻,其电感会造成更大问题。

传播延迟与传播延迟消散有何区别?这两个特性中,哪一个更值得关注?

传播延迟是指从输入信号跨过跃迁点到比较器输出实际切换的时间。传播延迟消散是指传播延迟相对于过驱电平的变化。如果在自动测试系统的引脚驱动电子设备中使用比 较器,传播延迟消散将决定最大边缘分辨率。相比之下,传播延迟可以视为固定时间偏移,因此可以通过其它技术予以补偿。

我有一个+5 V系统,并且不想增加额外的电源电压。我可以利用单电源为比较器供电吗?

可以,但为了建立阈值,请使用在器件共模范围内并充分旁路的稳定基准电压源。信号电平也需以此电压源为基准。

我有时发现比较器行为异常。原因可能是什么?

请检查输入信号的共模范围。运算放大器的输入电压通常为同一电平,比较器则不同,其输入端通常会有较大的差分电压摆幅。如果输入超过器件的额定共模范围(即使在额 定信号范围内),比较器可能会错误地响应。为使比较器正常工作,请确保两个输入信号均不超过其额定共模范围。例如,AD790的差分输入范围为 ±VS ,但其共模范围则是从 −VS 至 +VS以下2 V。

能否推荐这样一个电路:它在比较器离线时能执行自稳零调整,使漂移最低?

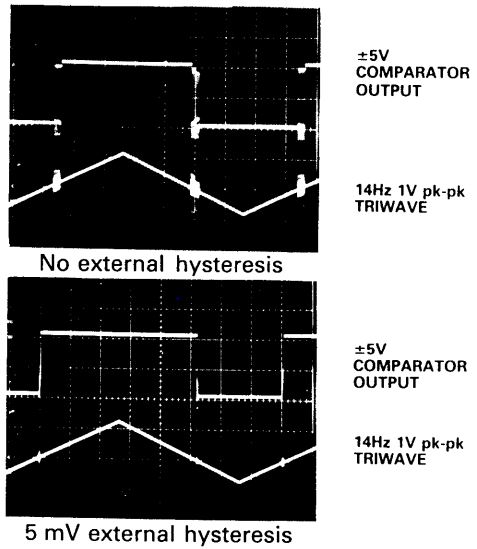

请试一下图3和图4所示的电路。在校准模式下,输入断开,比较器的正输入切换至地。比较器连在环路中,其中一对极性相反的低压源给缓冲电容充电,以响应比较器的 输出状态。

图3. 自稳零比较器在校准周期中通过积分消除失调。

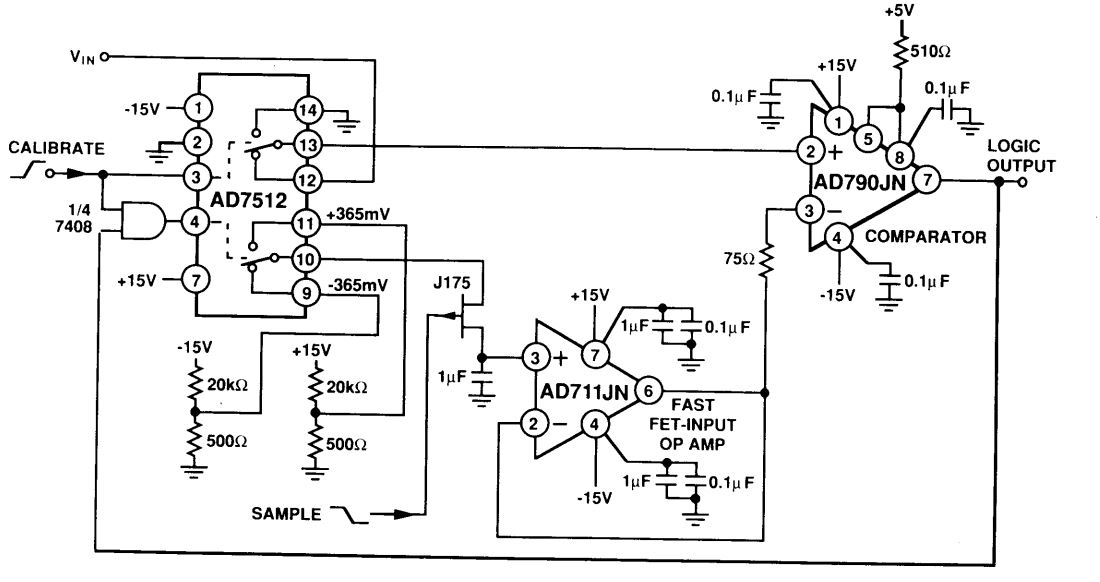

图4. 比较器输出、缓冲器输出和比较器输入。

如果比较器的负输入引脚高于地,比较器输出将为低,1 µF电容将与负电压(-365 mV)相连,并且缓冲放大器的输出电压将缓慢下降,直至低于正输入(地)加上迟 滞和任何失调,此时比较器切换。如果负输入引脚低于地,比较器输出将为高,1 µF电容将与正电压(+365 mV)相连,并且缓冲放大器的输出将缓慢上升。在最终状态下, 每次比较器切换(缓升或缓降变化超过迟滞电压),电流极性就会反向;因此,对电容电压求平均值便可消除缓冲器和比较器的失调。

校准周期结束时,JFET开关断开,电容充电到某一电压,其等于比较器和缓冲器的失调电压±迟滞电压。与此同时,校准信号变为低电平,从而禁用极性开关的反馈,并将输入信号与比较器相连。