# 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、2023年7月7日現在、アナログ・デバイセズ株式会社で確認した誤りを記 したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日: 2023年7月5日

製品名: MAX77348

対象となるデータシートのリビジョン(Rev): Rev.0

訂正箇所: Foot Note に関する記述

2ページ Note1 と Note2

【誤】

Note 1: パッケージの熱性能の測定は JESD-51 シリーズに基づきます。

Note 2: 熱パラメータは FR-4 の 4 層基板に基づきます。

### 【正】

Note 1: パッケージの熱性能の測定は JESD-51 シリーズに基づきます。熱パラメータは FR-4 の 4 層基板に基づきます。

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

電話 03(5402)8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

アナログ・デバイセズ株式会社

# 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、2023年7月7日現在、アナログ・デバイセズ株式会社で確認した誤りを記 したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日: 2023年7月5日

製品名: MAX77348

対象となるデータシートのリビジョン(Rev): Rev.0

訂正箇所: Foot Note に関する記述

5ページ Note 3∼Note 8

【正】

Note 4 と Note 6 を削除します。

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

電話 03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06(6350)6868

## MAX77348A, MAX77348B

#### 概要

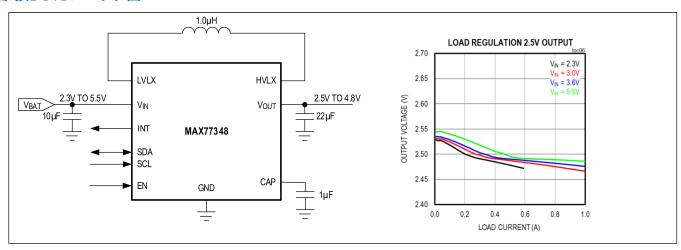

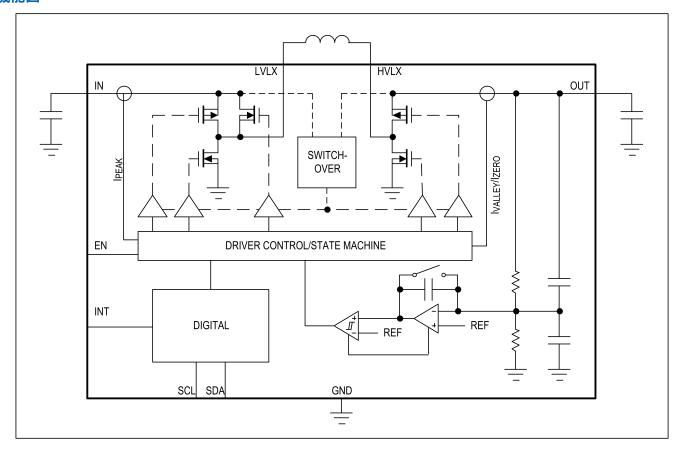

MAX77348 は超低自己消費電流の非反転昇降圧コンバータで、 最大 3.5W の出力電力に対応可能です。このデバイスでは、降圧、 昇降圧、昇圧の動作をシームレスに切り替える独自の制御アル ゴリズムを用いて、不連続性と出力電圧リップルの低調波を最 小限に抑えます。

MAX77348 は、シングル・セルのリチウムイオン・バッテリを 電源にして 3.5W 未満の出力電力を処理し高いシステム効率と精 度の高い電圧制御が求められるシステムに最適です。 MAX77348 のロー・ノイズ動作は、RF システム電力、イヤホ ン・アプリケーション、その他のポータブル・オーディオシス テムへの電源供給に最適です。

内蔵の低電圧ロックアウト(UVLO)、出力のアクティブ放電、 サーマル・シャットダウン保護により、異常な動作条件下でも 安全な動作を確保できます。

MAX77348 は設定自由度の高い PC シリアル・インターフェース を備えています。このデバイスは、1.77mm × 2.01mm の 16 バン プ 0.4mm ピッチ WLP パッケージで供給されます。

### アプリケーション

- 完全ワイヤレス・イヤホン(TWS)システム

- NB-IoT (狭帯域のモノのインターネット)

- ポータブル・オーディオ/ワイヤレス・システム

### 機能と利点

- 入力電圧範囲: 2.3V~5.5V

- 出力電圧範囲: 2.5V~4.8V

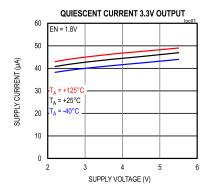

- 超低自己消費電流:3.5µA(代表値)

- ダイナミック電圧スケーリング (DVS)

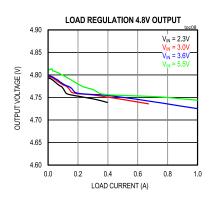

- 最適化された負荷レギュレーション性能

- パワーグッド割込み

- 出力のアクティブ放電

- 低く連続的なノイズ・プロファイル

- 動作範囲全域で不連続性を排除

- ノイズに敏感なアプリケーションでもポスト・フィルタリ ング LDO (低ドロップアウト電圧レギュレータ) 不要

- 保護機能

- 低電圧ロックアウト (UVLO)

- サーマル・シャットダウン

- 6.4ms のソフトスタート時間

- ステータス割込み付き I<sup>2</sup>C インターフェース

- プログラマブルな Vout

- ピーク電流制限レベル(IPSET1/IPSET2)

オーダー情報はデータシート末尾に記載されています。

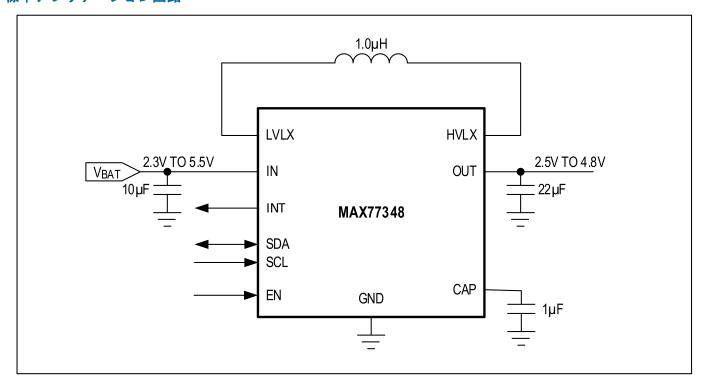

### 簡略化したブロック図

©2023 Analog Devices, Inc. All rights reserved. 商標および登録商標は各社の所有に属します。

本 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F

電話 03 (5402) 8200

大 阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F

電話 06(6350)6868

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 名古屋営業所/〒451-6038 電話 052 (569) 6300

# 超低 IQ、ロー・ノイズ 3.5W 昇降圧コンバータ

### 絶対最大定格

IN, OUT, SDA, SCL, EN, INTb, CAP $\sim$ GND ..  $-0.3V\sim$ +6V LVLX $\sim$ GND ..... $-0.3V\sim$ V<sub>IN</sub> + 0.3V HVLX $\sim$ GND ...... $-0.3V\sim$ Min. (Vout + 0.3, +6.0)V

| における連続消費電力<br>こでディレーティング) |

|---------------------------|

| 1381mW                    |

| +150°C                    |

| −40°C∼+150°C              |

| +260°C                    |

|                           |

Note 1: パッケージの熱性能の測定は JESD-51 シリーズに基づきます。

Note 2: 熱パラメータは FR-4の4層基板に基づきます。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する 規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## 推奨動作条件

| 動作ジャンクション温度 | 40°C∼+125°C |

|-------------|-------------|

| 入力電圧範囲      | 2.3V~5.5V   |

| 出力電圧範囲      | 2.5V~+4.8V  |

## 電気的特性

(特に指定のない限り、代表値は  $T_J \approx T_A = +25^{\circ}$ C、 $V_{SYS} = +3.6V$  での値。制限値は  $T_J = +25^{\circ}$ C で 100%テストされています。動作温度範囲  $(T_J = -40^{\circ}$ C~ $+125^{\circ}$ C) および対応する電源電圧範囲を超える制限値は、設計と特性評価により裏付けられています。) (Note 1)

| PARAMETER                                     | SYMBOL                             | CONE                                                                                                                                                 | DITIONS                                                     | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|------|------|-------|

| GLOBAL INPUT SUPPI                            | _Y                                 |                                                                                                                                                      |                                                             |      |      |      |       |

| Operating Voltage<br>Range                    | $V_{IN}$                           |                                                                                                                                                      |                                                             | 2.3  |      | 5.5  | V     |

| Input UVLO Rising<br>Threshold                | V <sub>UVLO_RISING</sub>           |                                                                                                                                                      |                                                             |      | 2.19 |      | V     |

| Input UVLO Falling<br>Threshold               | V <sub>UVLO_FALLING</sub>          |                                                                                                                                                      |                                                             |      | 2.10 |      | V     |

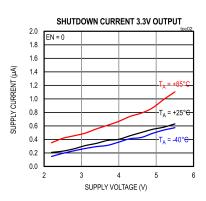

| Shutdown Supply<br>Current                    | $I_{SHDN}$                         | I <sup>2</sup> C Controlled                                                                                                                          |                                                             |      | 0.3  |      | μА    |

| Input Quiescent Current                       | $I_Q$                              | No load, $V_{OUT} = 5V$ , $V_{IN} = 3.7V$                                                                                                            | $V_{CAP}$ forced to $V_{IN}$ , $T_J$ up to 85°C             |      | 3.5  | 5.0  | 4     |

| input Quiescent Current                       | $I_{Q\_FAST}$                      | No load, $V_{OUT} = 5V$ , $V_{IN} = 3.7V$                                                                                                            | EN = High                                                   |      | 35   |      | - μΑ  |

| Maximum Output<br>Operative Power<br>(Note 3) | $P_{MAX}$                          | $\begin{aligned} & \text{Integrator enabled,} \\ & V_{\text{IN}} > 2.7 V, \\ & V_{\text{OUT}} \geq 3.2 V \end{aligned}$                              | $FETSCALE = 0, \\ L = 1\mu H, \\ C_{OUT\_EFF} = 8\mu F$     | 3.5  |      |      | W     |

|                                               |                                    | $\label{eq:local_control_control} \begin{split} & \text{Integrator enabled,} \\ & V_{\text{IN}} > 2.7 V, \\ & V_{\text{OUT}} \geq 3.2 V \end{split}$ | $FETSCALE = 1, \\ L = 2.2 \mu H, \\ C_{OUT\_EFF} = 4 \mu F$ | 1.75 |      |      |       |

| Maximum Output<br>Operative Power<br>(Note 5) | $P_{MAX}$                          | Integrator disabled,                                                                                                                                 | $FETSCALE = 0, \\ L = 1 \mu H, \\ C_{OUT\_EFF} = 8 \mu F$   | 3.2  |      |      | W     |

|                                               |                                    | $V_{\text{IN}} > 3.2V$ (Note 4), $V_{\text{OUT}} \ge 3.2V$                                                                                           | $FETSCALE = 1, \\ L = 2.2 \mu H, \\ C_{OUT\_EFF} = 4 \mu F$ | 1.75 |      |      |       |

| Output Voltage Program<br>Range               | $V_{OUT}$                          | 50mV step resolution                                                                                                                                 |                                                             | 2.5  |      | 4.8  | v     |

| Average Output Voltage<br>Accuracy            | ACC_OUT                            | $I_{OUT} = 1$ mA, $C_{OUT\_EFF} =$                                                                                                                   | 8μF                                                         | -2.4 |      | +2.4 | %     |

| Output UVLO Falling threshold                 | V <sub>OUT_UVLO</sub> _<br>FALLING |                                                                                                                                                      |                                                             |      | 1.87 |      | V     |

| Output UVLO Rising threshold                  | V <sub>OUT_UVLO_</sub><br>RISING   |                                                                                                                                                      |                                                             |      | 1.96 |      | V     |

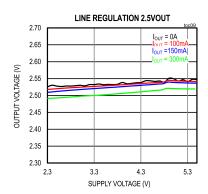

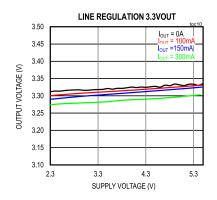

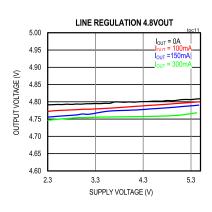

| Line Regulation Error                         | V <sub>LINE_REG</sub>              |                                                                                                                                                      |                                                             | -1.0 |      | +1.0 | %/V   |

| Load Regulation Error                         | $V_{LOAD\_REG}$                    | $\begin{array}{c} \text{Integrator enabled, V}_{\mathrm{IN}} = \\ \text{FETSCALE} = 0, P_{\mathrm{OUT}} = \end{array}$                               |                                                             | -1.0 |      | %    |       |

(特に指定のない限り、代表値は  $T_J \approx T_A = +25^{\circ}\text{C}$ 、 $V_{SYS} = +3.6\text{V}$  での値。制限値は  $T_J = +25^{\circ}\text{C}$  で 100%テストされています。動作温度範囲  $(T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C})$  および対応する電源電圧範囲を超える制限値は、設計と特性評価により裏付けられています。) (Note 1)

| PARAMETER                                            | SYMBOL                  | COND                                                                                                                            | ITIONS                                     | MIN  | TYP  | MAX  | UNITS                    |

|------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|------|------|--------------------------|

|                                                      |                         | Integrator disabled, $V_{IN}$ = $P_{OUT}$ = 1.5W, FETSCAL L = 2.2 $\mu$ H                                                       |                                            |      | -3.2 |      |                          |

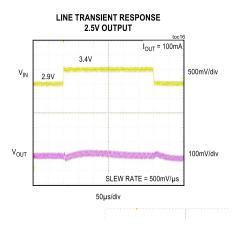

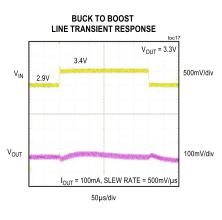

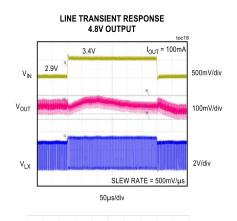

| Line Transient<br>Response                           | $V_{\text{LINE\_TRAN}}$ | $\begin{aligned} V_{OUT} &= 3.4V,  V_{IN} \text{ from } 3\\ time,  I_{LOAD} &= 750\text{mA},  IN\\ SWOFRCIN &= 0 \end{aligned}$ |                                            |      | 0    |      | mV                       |

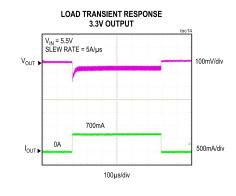

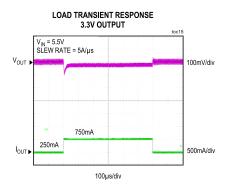

| Load Transient<br>Response                           | $V_{LOAD\_TRAN}$        | $V_{OUT} = 5V, V_{IN} = 3.7V, I$<br>INTEGEN = 1                                                                                 | $I_{LOAD} = 10 \mu A$ to $700 \text{mA}$ , |      | -150 |      | mV                       |

| Input Supply Current<br>During Start-up              | $I_{\rm IN\_STUP}$      | $V_{IN} = 3.6V, V_{OUT} = 5V, I$                                                                                                | $I_{LOAD} = 0$                             |      | 1    |      | mA/C <sub>OUT</sub> (μF) |

| Maximum Output                                       | <b>D</b>                | FETSCALE = 0                                                                                                                    |                                            | 400  | 600  |      | ***                      |

| Power During Startup (Note 3)                        | $P_{MAX\_STUP}$         | FETSCALE = 1                                                                                                                    |                                            | 200  | 300  |      | mW                       |

| Soft-start Time                                      | $t_{SS}$                | Time from $V_{OUT} = 0V$ to                                                                                                     | final value                                |      | 6.4  |      | ms                       |

| Start-up Time                                        | t <sub>STARTUP</sub>    | Time from EN = 1 to $V_{OUT}$ in regulation                                                                                     | EN = HIGH                                  |      |      | 13   | ms                       |

| Active Discharge<br>Current                          | $I_{ACTD}$              |                                                                                                                                 |                                            |      | 20   |      | mA                       |

| Passive Discharge<br>Resistance                      | $R_{PSVD}$              |                                                                                                                                 |                                            |      | 1.2  |      | kΩ                       |

| DIGITAL                                              |                         |                                                                                                                                 |                                            |      |      |      |                          |

| SDA, SCL, INTb, EN<br>Input Leakage Current          | $I_{LK}$                | $T_J = +25^{\circ}C$                                                                                                            |                                            | -1.0 |      | +1.0 | μА                       |

| SDA, SCL, EN Input<br>Logic High                     | $V_{\mathrm{IH}}$       |                                                                                                                                 |                                            | 1.4  |      |      | v                        |

| SDA, SCL, EN Input<br>Logic Low                      | $V_{\rm IL}$            |                                                                                                                                 |                                            |      |      | 0.4  | V                        |

| INTb Output Logic Low                                | $V_{OL}$                | $I_{OL} = 4mA$                                                                                                                  |                                            |      |      | 0.4  | V                        |

| SCL Clock Frequency                                  | $f_{SCL}$               |                                                                                                                                 |                                            |      |      | 680  | kHz                      |

| Bus Free Time Between<br>STOP and START<br>condition | $t_{ m BUF}$            |                                                                                                                                 |                                            | 0.75 |      |      | μs                       |

| START Condition<br>(Repeated) Hold Time              | t <sub>HD_STA</sub>     | (Note 7)                                                                                                                        |                                            | 0.35 |      |      | μs                       |

| Low Period of SCL<br>Clock                           | $t_{ m LOW}$            |                                                                                                                                 |                                            | 0.75 |      | 1.25 | μs                       |

(特に指定のない限り、代表値は  $T_J \approx T_A = +25$ °C、 $V_{SYS} = +3.6$ V での値。制限値は  $T_J = +25$ °C で 100%テストされています。動作温度範囲  $(T_J = -40$ °C~+125°C) および対応する電源電圧範囲を超える制限値は、設計と特性評価により裏付けられています。) (Note 1)

| PARAMETER                                          | SYMBOL              | CONDITIONS | MIN  | TYP | MAX  | UNITS |

|----------------------------------------------------|---------------------|------------|------|-----|------|-------|

| High Period of SCL<br>Clock                        | $T_{ m HIGH}$       |            | 0.35 |     |      | μs    |

| Setup Time for a<br>Repeated START<br>Condition    | t <sub>SU_STA</sub> |            | 0.35 |     |      | μs    |

| Data Hold Time                                     | t <sub>HD_DAT</sub> | (Note 8)   |      |     | 0.53 | μs    |

| Data Setup Time                                    | t <sub>SU_DAT</sub> |            | 100  |     |      | ns    |

| Setup Time for STOP<br>Condition                   | t <sub>SU_STO</sub> |            | 0.35 |     |      | μs    |

| Spike Pulse Width<br>Suppressed by Input<br>Filter | t <sub>SP</sub>     |            | 50   |     |      | ns    |

- Note 3:全てのデバイスは、T<sub>A</sub>=+25℃で100%出荷テストしています。動作温度範囲を超える制限値は設計により裏付けられています。

- Note 4: 入力の動作電圧範囲全域にわたる出力電力は、入力電流によって制限されます。 $V_{\rm IN}$ に対する電力の制限の変化については、TOC03 を参照してください。

- Note 5: このパラメータは出荷テストされておらず、値は特性評価のみによって生成されたものです。

- Note 6: 積分器を無効化した状態で下限 2.7V まで動作が可能ですが、安定性が確保されるのは出力電圧 1.75W までです。 1.75W を超えると、出力容量を追加しない限り、発振の可能性があります。

- Note  $7:f_{\text{SCL}}$  は最小クロック・ロー時間と立上がり/立下がり時間の和が確保されたものであることが必要です。

- Note 8:  $t_{HD\ DAT}$  が最大値となるのは、デバイスが SCL 信号のロー時間( $t_{LOW}$ )を延長しない場合だけに限る必要があります。

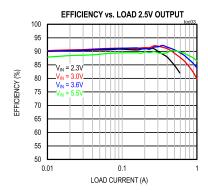

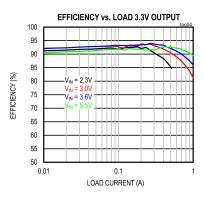

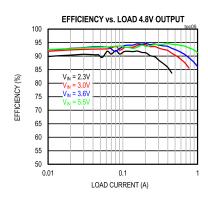

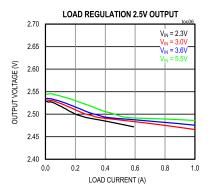

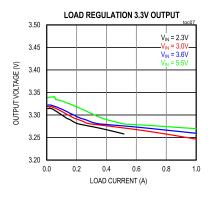

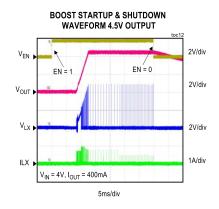

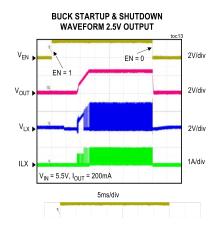

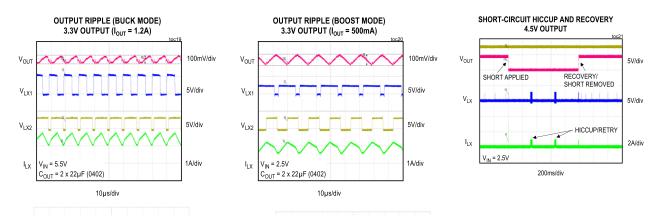

### 標準動作特性

特に指定のない限り、 $V_{IN}$  = +3.7V、 $C_{IN}$  = 22 $\mu$ F(0402 ケース・サイズ)、 $C_{OUT}$  = 2 × 22 $\mu$ F(0402 ケース・サイズを 2 個)、L = 2.2 $\mu$ H(2520 ケース・サイズ)、 $T_A$  = +25 $^{\circ}$ C。

特に指定のない限り、 $V_{IN}$  = +3.7V、 $C_{IN}$  = 22 $\mu$ F(0402 ケース・サイズ)、 $C_{OUT}$  = 2 × 22 $\mu$ F(0402 ケース・サイズを 2 個)、L = 2.2 $\mu$ H(2520 ケース・サイズ)、 $T_A$  = +25 $^{\circ}$ C。

特に指定のない限り、 $V_{IN}$  = +3.7V、 $C_{IN}$  = 22 $\mu$ F(0402 ケース・サイズ)、 $C_{OUT}$  = 2 × 22 $\mu$ F(0402 ケース・サイズを 2 個)、L = 2.2 $\mu$ H(2520 ケース・サイズ)、 $T_A$  = +25 $^{\circ}$ C。

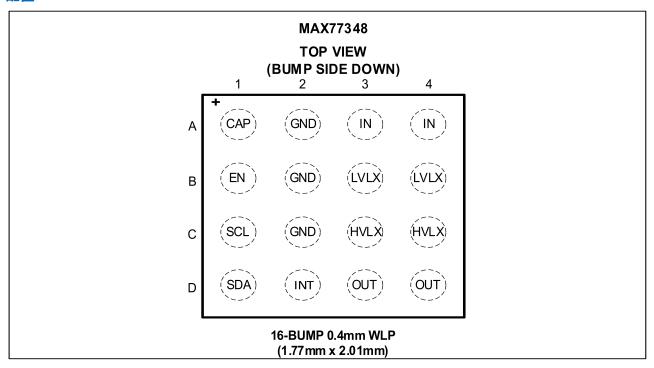

## ピン配置

## 端子説明

| ピン         | 名称   | 説明                                                                                                                                                                                                        | Туре  |  |  |  |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|

| A1         | CAP  | 内部電源用バイパス・コンデンサ接続端子。470nFの容量を GND との間に接続します。                                                                                                                                                              |       |  |  |  |

| A2, B2, C2 | GND  | グランド。                                                                                                                                                                                                     |       |  |  |  |

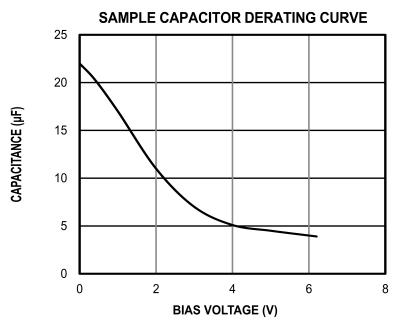

| A3, A4     | IN   | 入力電源。 $5\mu F$ を下限とし、バイアス電圧 $V_{IN}$ に対するディレーティング曲線の値に等しい実効容量で、できるだけデバイスに近い場所で GND にバイパスします。                                                                                                              | P     |  |  |  |

| B1         | EN   | チップ・イネーブル・ピン。                                                                                                                                                                                             | DI    |  |  |  |

| B3, B4     | LVLX | スイッチング・ノード。FETScale = 0 の場合は $1\mu H$ のインダクタ、FETScale = 1 の場合は $2.2\mu H$ のインダクタで HVLX に接続します。                                                                                                            | P     |  |  |  |

| C1         | SCL  | $I^2C$ シリアル・クロック入力。EN の設定に注意してください。デフォルトでディスエーブルされているバージョンの場合には、 $I^2C$ コマンドで出力をイネーブルするために、 $I^2C$ インターフェース用に外部電源を使用します。                                                                                  | DI    |  |  |  |

| C3, C4     | HVLX | スイッチング・ノード。FETScale = $0$ の場合は $1\mu H$ のインダクタ、FETScale = $1$ の場合は $2.2\mu H$ のインダクタで LVLX に接続します。                                                                                                        | Р     |  |  |  |

| D1         | SDA  | I <sup>2</sup> C シリアル・データ入力/オープンドレイン出力 EN の設定に注意してください。デフォルトでディスエーブルされているバージョンの場合には、I <sup>2</sup> C コマンドで出力をイネーブルするために、I <sup>2</sup> C インターフェース用に外部電源を使用します。                                            | DI/DO |  |  |  |

| D2         | INTb | 割込み出力。オープンドレインであり、プルアップ抵抗でシステムのロジック電源に接続します。                                                                                                                                                              | DI    |  |  |  |

| D3, D4     | OUT  | 昇降圧出力。 $FETScale = 0$ の場合は、バイアス電圧 $V_{OUT}$ に対するディレーティング曲線の値の $2$ 倍 に等しい実効容量で、できるだけデバイスに近い場所で $GND$ にバイパスします。 $FETScale = 1$ の場合は、バイアス電圧 $V_{OUT}$ に対するディレーティング曲線の値の実効容量で、できるだけデバイスに近い場所で $GND$ にバイパスします。 | Р     |  |  |  |

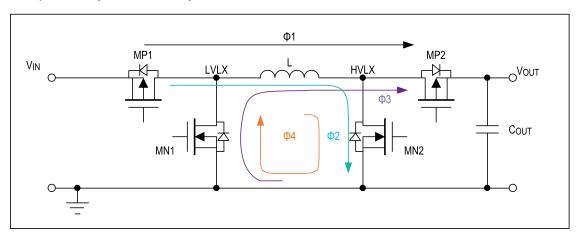

#### 機能図

### 詳細

MAX77348 は超低自己消費電流の非反転昇降圧コンバータで、3.5V で 1A の電流供給能力を備え、長い動作時間と突発的な大電流の両方が要求されるアプリケーションを対象としています。ヒステリシス付きピーク/バレー電流制御アーキテクチャにより、過渡応答が高速でセトリング・タイムが最小となり、ピーク電力が高いアプリケーションで負荷の大きな過渡変化を処理できます。このデバイスでは、降圧、昇降圧、昇圧の動作をシームレスに切り替える独自の制御アルゴリズムを用いて、不連続性と出カリップルの低調波ノイズを最小化します。2.3V と低い起動電圧のため多様な電力源に対応でき、最低動作電圧はほぼゼロであり電力源から最大限にエネルギーを引き出します。インダクタンスと容量に対する要求は低く、全体のソリューション・サイズを小さくできるので、MAX77348 はスペースの制約があるアプリケーションに最適です。このデバイスは効率が高くノイズが低いので、ワイヤレスやノイズの影響を受けやすいアプリケーションに適しており、低消費電力広域通信網(LPWAN)や光センサー・システムに用いることができます。自己消費電流が 3.5μA(代表値)と非常に低く、軽負荷時に不連続導通モード(DCM)で動作するため、平均電力が低い電池駆動のアプリケーションでの動作時間を長くすることができます。

### 起動

MAX77348 は 2.3V の最低入力電圧での起動がサポートされています。デバイスの起動後は、内蔵のブートストラップ機能により、入力から実質的に引き出すことができる電流量のみに基づく非常に低い入力電圧での動作が可能です。

### スイッチング・フェーズ

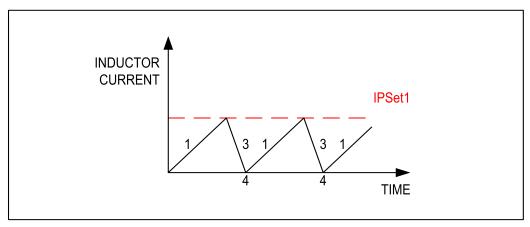

レジスタ設定と入出力電圧の関係に応じて、次に示すスイッチング・フェーズを特定の順序でたどるよう昇降圧部が動作し、出力に電荷を供給します。各フェーズでは2つのスイッチのみがオンになります。

Φ1: MP1 オン、MP2 オン。インダクタを充電。

Φ2: MP1 オン、MN2 オン。インダクタを充電。

Φ3: MN1 オン、MP2 オン。インダクタから放電。

Φ4: MN1 オン、MN2 オン。フリーホイール。

図 1. 昇降圧レギュレータとスイッチング・フェーズ

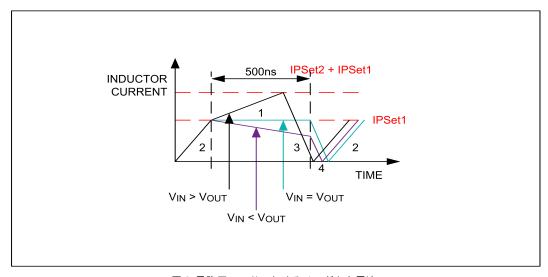

### 昇降圧モード

Mode = 0(レジスタ 0x01[2])のとき、レギュレータは昇降圧モードで動作します。インダクタは  $\Phi 2$  で IPSet1(レジスタ 0x03[3:0])まで 充電します。C = 0 に遷移します。C = 0 に電流が IPSet1 + IPSet2(レジスタ 0x03[7:4])に達するか 500ns の遅延時間が 経過するまでの間、インダクタが充電を継続します。C = 0 に入り、谷電流制限値までインダクタ電流を放電します。インダクタ電流が 谷電流交差スレッショルドに達するか 0 を切って下がると、レギュレータは次の充電サイクルまでの間 C = 0 であれば約 30ns で C = 0 であれば、C = 0 では、C = 0 であれば、C = 0 では、C = 0 では、C =

図 2. 昇降圧モードにおけるインダクタ電流

#### 降圧のみモード

$V_{\rm IN} > V_{\rm OUT}$  のときの効率を最大化するため、昇降圧レギュレータは降圧のみモードを備えています。Mode=1 のとき、レギュレータは同期整流式降圧レギュレータとして動作します。デバイスが降圧のみモードに設定されている場合、レギュレータは  $\Phi2$  に入ることはありません。インダクタの充電は常に $\Phi1$  によります。電流が PSet1 に達するか FSet1 に達するか FSet1 にでのインダクタ電流を出力に供給するパスを作ります。FSet1 になります。FSet1 にきするか FSet1 にきます。 FSet1 にきまます。 FSet1 にきます。 FSet1 にきまます。 FSet1 にきまます。 FSet1 にきます。 FSet1 にきまます。 FSet1 にきまます。 FSet1 にきまます。 FSet1 にきます。 FSe

降圧のみモードでは、昇降圧モードには存在するスイッチング損失が低減されます。 $V_{OUT}$ が  $V_{IN}$ より常に低い場合には、降圧のみモードを使用してください。

図3. 降圧のみモードにおけるインダクタ電流

### インダクタのピーク電流と谷電流の制限

昇降圧レギュレータはインダクタ電流の最大値と最小値をモニタします。IPAdptDis = 1(レジスタ 0x04[1])の場合、ピーク電流は IPAdptDis(レジスタ 0x03)の値に固定され、谷電流は 0mA に固定されます。AdptDis = 0 の場合、ピーク電流と谷電流は負荷条件に応じた変動が可能です。

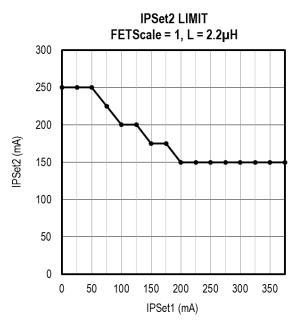

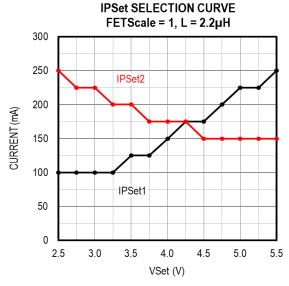

ピーク電流は CFG2 レジスタで設定されます。IPSet1 によって  $V_{IN} < V_{OUT}$  のときのピーク電流が制御され、 $\Phi 1$  のタイムアウト時間を開始します。IPSet2 は、昇降圧モードで  $V_{IN} > V_{OUT}$  の場合について、2 つめの電流制限を設定します。 $V_{IN} > V_{OUT}$  のときの全インダクタ電流の制限値は IPSet1 + IPSet2 です。インダクタ電流が IPSet1 + IPSet2 に達するか、500ns のタイムアウトが経過すると、昇降圧レギュレータは $\Phi 1$  から  $\Phi 3$  に遷移します。IPSet1 と IPSet2 の差分を最小化すると、出力リップルが低減されますが、効率の低下につながります。出力リップルを低くし、効率も最大化するよう、ピーク電流の設定には注意を払う必要があります。 ② 4 に IPSet1 に対する IPSet2 の安全動作領域を示しています。 ② 4 に示された限界を外れる値を選択すると、望ましくない挙動が発生する可能性があります。 ② 5 は、特定のVSet の値に対応して、効率と電圧リップルのバランスを取れる IPSet1 と IPSet2 の組み合わせを選択するための指針を視覚的に示しています。

起動中の突入電流を制御するために、MAX77348 は起動中には強制的に不連続導通モード(谷電流は常に 0)で動作し、IP1SS と IP2SS によるピーク電流設定をオーバーライドします。出力が最終の電圧に到達すると、連続導通モードでの動作が可能となり、IPSet1 と IPSet2 の設定が有効となります。

IPAdptDis = 0 のときの MAX77348 の挙動は更に、ゼロ電流コンパレータによって定義されます。制御ループで電流のゼロ交差が検出されると、 $\Phi$ 4 に遷移します。

図 4. FETScale = 1 (FET スケーリング設定) における IPSet1 に対する IPSet2 の下限値

図 5. FETScale = 1 (FET スケーリング設定) における IPSet1 と IPSet2 の推奨設定

ZCCmpDis=1 (レジスタ 0x01[4]) のとき、ゼロ交差コンパレータはディスエーブルされ、昇降圧部はピーク電流と谷電流の制限値のみに基づいて動作します。この構成では、谷電流の制限値がゼロ交差制限のように機能します。DCM の場合には、谷電流制限は 0mA であり、電流の真のゼロ交差での動作となります。CCM の場合には谷電流の制限は適応型電流制御によって自動的に調整され、実効的なゼロ電流のポイントが 0mA よりも大きくなる場合があります。このため MAX77348 は、インダクタの充電フェーズへの遷移前にインダクタ電流が谷電流スレッショルドに達すると、毎回短い期間 04 に入ります。00 を設定すると、ゼロ電流コンパレータおよび昇降圧部はピーク電流、谷電流、ゼロ交差電流の制限で動作します。適応型電流ループがピーク電流と谷電流を調整しますが、ゼロ交差の制限は 0mA に固定されます。00 の場合には、レギュレータは 00 などCCmpDis 00 ときと同様に機能します。一方 00 では、谷電流はゼロ交差電流よりも大きいため、インダクタ電流が谷電流スレッショルドに達すると、レギュレータは 00 をバイパスしてすぐにインダクタの充電フェーズに入ります。

電流のゼロ交差コンパレータをディスエーブルすると、昇降圧コンバータの出力リップルが抑制されます。コンパレータをイネーブルすると、ZCCmpDis=1 のときには存在する  $\Phi$ 4 ステージが CCM ではなくなるため、CCM での効率が改善します。

### 積分器制御ループの無効化

MAX77348 は、通常動作時は内蔵の積分器を制御ループで使用します。この積分器により高負荷時の負荷レギュレーションが改善しますが、過渡応答時間が長くなります。感度の高い計測(例えばフォトプレチスモグラフィ(PPG))でノイズの注入を防ぐ目的で、出力が最終のレギュレーション値に速くセトリングすることが必要なアプリケーションでは、積分器をディスエーブルし、レギュレータを比例系のみの制御ループで動作させることができます。IntegEn ビット(レジスタ 0x04[2])で積分器のイネーブルとディスエーブルができて、負荷過渡変動に対する応答速度の改善(積分器オフ)、負荷駆動能力の拡大(積分器オン)が可能です。積分器をディスエーブルしている場合には、出力の安定性が確保されるのは、2.5V以上の入力電圧に対する最大出力電力までの範囲に限られることに注意してください。これより低い入力電圧で動作させるには、出力容量を大きくします。

### 入力動作電圧

低い入力電圧で動作する際は、システムはシャットダウンに至らない限り電力源から可能な限りエネルギーを引き出します。起動後は、SwoFrcIn=0かつ  $Vour\geq 2.5V$  において、MAX77348 は、入力から実質的に引き出すことができる電流量のみに基づく非常に低い入力電圧で動作が可能です。これにより、電力供給能力は限られますが、システム中で MAX77348 を最低起動電圧よりかなり低い電圧で動作させることが可能です。

入力電圧が低い場合は、入力 p チャンネル MOSFET の  $R_{ON}$  が増加します。抵抗が必然的に増加するのを補償するため、入力 MOSFET と 並列に n チャンネル MOSFET が配置されています。この n チャンネル MOSFET は、入力電圧が高い場合のスイッチング損失を低減するため、入力電圧が  $V_{UVLO_F}$  を下回るときにのみイネーブルされます。n チャンネル・デバイスに十分なオーバードライブが与えられるよう、 $V_{OUT} \geq 2.5V$  を保つことが必要です。

### 出力動作電力などの最適化

MAX77348 は、アプリケーションの性能を最適化できるよう多数の動作モードを備えた柔軟性の高いデバイスです。負荷過渡応答時の定常電圧へのセトリング・タイムが重要なアプリケーションでは、比例制御のみの出力応答(IntegEn = 0、ディスエーブル)でのメリットが得られますが、セトリングのスピードと引き換えに定常時の負荷レギュレーション誤差は増加します。反対に、応答時間に対しての感度が高くなく、積分器がイネーブルされた場合(IntegEn = 1、イネーブル)の定常時の負荷レギュレーション誤差が小さくなることがメリットとなるアプリケーションもあります。

また、負荷容量のどの領域が効率上重要であるかにより、FETScale の設定を選択して効率を最適化することもできます。アプリケーションが主に軽負荷時の効率を最適化するべきものであれば、FETScale = 1 (イネーブル)を設定する必要があり、その逆も同じように成立します。FETScale = 1 を設定することによる軽負荷時の効率向上には、最大出力電力が低くなるトレードオフがあることに注意が必要で、設定を決める際に考慮を要します。各々の設定についての性能の比較は、標準動作特性のセクションで確認できます。

最後に、MAX77348 は内蔵のスイッチオーバー回路(SwoFrcIN で設定)を備えており、昇降圧部の内部回路がどの入力を受けてドライブされるかを決めます。自己消費電流が重要で、主な動作モードが出力への昇圧であるアプリケーションでは、このスイッチオーバーは強制的に入力(SwoFrcIN = 1)にする必要があります。これは、SwoFrcIN = 0 のときには自己消費電流が出力から流れるため、増幅率と変換の効率に従って入力電流が増加するからです。しかし、低い入力動作電圧への対応が必要な場合には、SwoFrcIN = 0 の設定にすれば、出力電圧を使用して昇降圧部のスイッチング FET を導通させ、オン抵抗を低く保つことができるため、入力電圧がはるかに低くなっても動作可能です。SwoFrcIN = 1 のときには、 $V_{IN}$ が  $V_{UVLO_F}$ (代表値 2.10V)より低くなると昇降圧部の出力が自動的にシャットダウンすることに注意してください。SwoFrcIN = 0 のときには、 $V_{IN}$ が  $V_{IN}$ が非常に低くなっても出力は継続し、出力電圧が  $V_{OUT\_UVLO_F}$ を下回るか、ユーザによりディスエーブルされた場合に限りディスエーブルされます。この動作モードでは、出力の電力供給能力は入力電圧の低下に伴って低減していきます。入力電圧が限界レベルまで低下したことを示すため、デバイスは INUVLO 状態で動作し、システムに割込みを発行します。 $V_{IN}$ が  $V_{UVLO_F}$ より低くなっており、ソースが限界状態にある可能性があることを意味します。各々の設定についての性能の比較は、標準動作特性のセクションで確認できます。

上記の設定の組み合わせには、それぞれ考慮すべきトレードオフが存在します。

#### デバイス制御

MAX77348 は、デバイスとホスト・マイクロプロセッサの間のインターフェースを設けることで、柔軟なシステム設定が可能です。レギュレータの様々なパラメータ、例えば出力電圧、インダクタのピーク電流レベル、FET のスケーリングなどが、どのようなアプリケーションに対してもリアルタイムで最適化できます。デフォルトの値が工場でプログラムされていますが、I<sup>PC</sup> レジスタによって新しい値を設定できます。I<sup>PC</sup> 制御を行うデバイスでは、EN のデフォルト設定の確認に注意が必要です。デフォルトで EN がディスエーブルされているバージョンでは、システムで I<sup>PC</sup> コマンドによって昇降圧部を起動するために、別の電源が必要となります。

レジスタの説明で、このインターフェースで提供される全ての構成設定とステータス情報について詳細を記します。MAX77348 のスレーブ・アドレスの情報は、アプリケーション情報のセクションに記載されています。

#### サーマル・シャットダウン

この IC には、ダイ温度を監視する過熱保護回路が内蔵されています。ジャンクション温度 (T<sub>1</sub>) がサーマル・シャットダウンの立上がりスレッショルド (代表値 135℃) を超過するとサーマル・シャットダウンに入ります。温度がサーマル・シャットダウンの立下がりスレッショルド (代表値 120℃) を下回ると、サーマル・シャットダウンを抜けて自動的に起動します。デバイスがサーマル・シャットダウンを抜けた後は、IC を起動させるために EN をトグルする必要はありません。

### ダイナミック電圧スケーリング(DVS)

MAX77348 の出力電圧は、デバイスがイネーブルされている間はどの時点でも、再起動することなく変更できます。この機能はダイナミック電圧スケーリング(DVS)と呼ばれています。DVS により、動作モードに応じて電圧や電力についての要求が変動する場合に、様々な電圧レールでのシステム動作が可能です。特定の動作モードで要求される最小値まで電圧を下げることにより、全体のシステム効率が向上します。出力電圧は VSet[5:0] (レジスタ 0x02[5:0]) で設定されます。

表 1. 特性とデバイス設定

| <b>以1.</b> 内位 2 7 7 7                                                         |                               | CHARACTERISTI                                                                      | CS                                          |                                                              | С        | EVICE SETTING | S        |

|-------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------|----------|---------------|----------|

| MAX.<br>OUTPUT<br>POWER<br>(V <sub>IN</sub> , V <sub>OUT</sub> ≥<br>3.2V) (W) | QUIESCENT<br>CURRENT          | OPTIMIZED FOR: STEADY- STATE LOAD REGULATION ERROR OR LOAD TRANSIENT SETTLING TIME | EFFICIENCY<br>OPTIMIZED<br>CURRENT<br>RANGE | INPUT<br>OPERATING<br>VOLTAGE <<br>V <sub>UVLO_FALLING</sub> | FETSCALE | INTEGEN       | SWOFRCIN |

| 3.2                                                                           | INCREASED<br>IN BOOST<br>MODE | SETTLING<br>TIME                                                                   | HIGH                                        | YES                                                          | 0        | 0             | 0        |

| 3.2                                                                           | LOWEST                        | SETTLING<br>TIME                                                                   | HIGH                                        | NO                                                           | 0        | 0             | 1        |

| 3.5                                                                           | INCREASED<br>IN BOOST<br>MODE | LOAD<br>REGULATION                                                                 | HIGH                                        | YES                                                          | 0        | 1             | 0        |

| 3.5                                                                           | LOWEST                        | LOAD<br>REGULATION                                                                 | HIGH                                        | NO                                                           | 0        | 1             | 1        |

| 1.75                                                                          | INCREASED<br>IN BOOST<br>MODE | SETTLING<br>TIME                                                                   | LOW/MEDIUM                                  | YES                                                          | 1        | 0             | 0        |

| 1.75                                                                          | LOWEST                        | SETTLING<br>TIME                                                                   | LOW/MEDIUM                                  | NO                                                           | 1        | 0             | 1        |

| 1.75                                                                          | INCREASED<br>IN BOOST<br>MODE | LOAD<br>REGULATION                                                                 | LOW/MEDIUM                                  | YES                                                          | 1        | 1             | 0        |

| 1.75                                                                          | LOWEST                        | LOAD<br>REGULATION                                                                 | LOW/MEDIUM                                  | NO                                                           | 1        | 1             | 1        |

### アプリケーション情報

### 入力コンデンサと出力コンデンサ

MAX77348 はケース・サイズの小さいセラミック・コンデンサを使用できるように設計されています。したがって、0603 および 0402 (インペリアル) のコンデンサの急峻な電圧ディレーティングを許容できるよう、このデバイスの入力容量条件と出力容量条件は小さい値に抑えられています。 図 6 のディレーティング曲線の例に、IN と OUT の最小容量の要求条件を示しています。安定性と低ノイズを確保するため、IN に置く容量は、 $5\mu$ F を下限とし、図 6 での想定される最小の  $V_{\rm IN}$ に対する値のものとします。OUT に置く容量は、FETScale = 1 の場合は図 6 での想定される最大の  $V_{\rm OUT}$  に対する値、FETScale = 0 の場合はその 2 倍の値とします。

図 6. 入出力容量についてのコンデンサのディレーティング

### インダクタの選択

MAX77348のインダクタは、アプリケーションに対して最適化できるよう選択します。FET スケーリングが有効な場合(FETScale = 1)には  $2.2 \mu H$ 、FET スケーリングが無効な場合(FETScale = 0)には  $1 \mu H$  のインダクタ値が要求されます。インダクタの値のほか、物理サイズ、DC抵抗(DCR)、最大平均電流、飽和電流が、考慮すべき主な条件です。最大平均インダクタ電流は、次式で計算されます。

$$I_{L\_MAX} = \frac{V_{OUT\_MAX} \times I_{OUT\_MAX}}{\eta \times V_{IN\_MIN}}$$

ここで、

V<sub>OUT MAX</sub> = 最大想定動作電圧、

IOUT MAX = 最大想定出力電流、

V<sub>IN MIN</sub> = 最小想定動作入力電圧、

η=最小入力電圧および最大出力電力における最も厳しい条件の想定効率です(効率の見積もりについては標準動作特性を参照)。

上記で計算される平均インダクタ電流によって、インダクタの温度上昇を見込んだ上で必要とされる最大平均電流が規定されています。 必要なインダクタ飽和電流を決定するには、ピーク電流を計算します。

このコンバータのピーク電流は、次のように計算できます。

### IL PEAK = IL MAX + (1.1 x IPSet1)

ここで、IPSet1 はレジスタ 0x03 で指定されるピーク電流設定です。インダクタの選択において、高い効率を得るために重要な条件の1つに、インダクタの DCR があります。効率を最大化するためには、要求されるパッケージ・サイズで可能な限り低い DCR のインダクタを選択します。もう1つ考慮すべき条件は磁気損失です。一般的に磁気損失は、物理サイズの大きなインダクタや飽和電流定格の高いインダクタでは低くなります。多くの場合、フェライト・インダクタは AC 特性が十分でなく、特に非連続導通モード(DCM)ではこの傾向が強いため、使用は避けてください。

## 標準アプリケーション回路

## I<sup>2</sup>C インターフェース

MAX77348 にはホスト・コントローラとのデータ通信用に I<sup>2</sup>C 互換インターフェース (SCL および SDA) が備わっています。MAX77348 は 0kHz~680kHzの I<sup>2</sup>C 周波数をサポートしています。SCL と SDA は、プルアップ抵抗で正電源に接続することが必要です。

### スレーブ・アドレス

MAX77348 は工場出荷設定により、3 つの異なる 7 ビット・スレーブ・アドレスを指定できます。0b1101000(0x68)と読出し/書込みビット、0b1101100(0x6C)と読出し/書込みビット、0b1101110(0x6E)と読出し/書込みビットです。このアドレスは、START 条件に続けて MAX77348 に送信される情報の最初のバイトです。

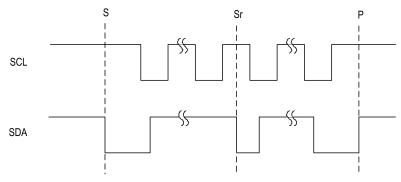

#### START、STOP、反復 START の条件

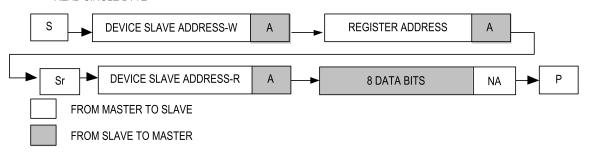

$I^2$ C を使用して MAX77348 に書き込む場合、マスタは START 条件(S)に続けて MAX77348 の  $I^2$ C 書込みアドレスを送信します。このアドレスに続けて、マスタはプログラムするレジスタのレジスタ・アドレスを送信します。そして STOP 条件(P)を発行してバスの制御を停止し通信を終了するか、反復 START 条件(Sr)を発行して別の  $I^2$ C スレーブとの通信を開始します。図 7 を参照してください。

図 7. I<sup>2</sup>C の START、STOP、反復 START の条件

#### ビット転送

SCL クロック・サイクルの立上がりエッジごとに、1 データ・ビットが転送されます。SDA 上のデータは、SCL クロック・パルスがハイの期間中は安定した状態でなければなりません。SCL がハイで安定している期間に SDA が変化すると、制御信号とみなされます(START、STOP、反復 START の条件のセクションを参照)。バスがアクティブでないとき、SDA と SCL は共にハイのままです。

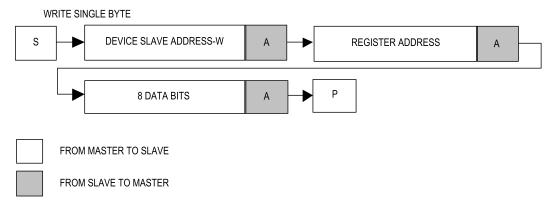

#### 1パイト書込み

この動作では、マスタは1つのアドレスと2つのデータ・バイトをスレーブ・デバイスに送信します(図8)。以下の手続きは、1バイト書込みの動作を示すものです。

- マスタは START 条件を送信します。

- マスタは7ビットのスレーブ・アドレスに続けて書込みビット(ロー・レベル)を送信します。

- 指定アドレスのスレーブが、データ・ラインに ACK をアサートします。

- マスタは8ビットのレジスタ・アドレスを送信します。

- スレーブは、このアドレスが有効であればデータ・ラインに ACK をアサートします (無効であれば NACK)。

- マスタは8つのデータ・ビットを送信します。

- スレーブがデータ・ラインに ACK をアサートします。

- マスタは STOP 条件を生成します。

図 8. バイト書込みシーケンス

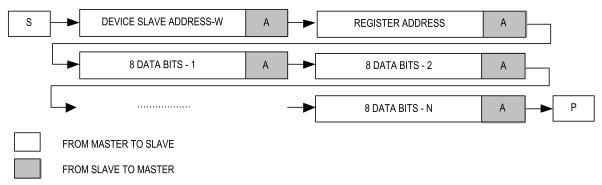

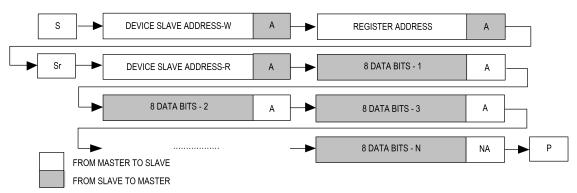

#### バースト書込み

この動作では、マスタは 1 つのアドレスと複数のデータ・バイトをスレーブ・デバイスに送信します(図 9)。スレーブ・デバイスは、各データ・バイトが送出されるごとに自動的にレジスタ・アドレスをインクリメントしますが、アクセスされたレジスタが 0x00 の場合には、レジスタ・アドレスは変化しません。以下の手続きは、バースト書込みの動作を示すものです。

- マスタは START 条件を送信します。

- マスタは7ビットのスレーブ・アドレスに続けて書込みビット (ロー・レベル) を送信します。

- 指定アドレスのスレーブが、データ・ラインに ACK をアサートします。

- マスタは8ビットのレジスタ・アドレスを送信します。

- スレーブは、このアドレスが有効であればデータ・ラインに ACK をアサートします (無効であれば NACK)。

- ▼スタは8つのデータ・ビットを送信します。

- スレーブがデータ・ラインに ACK をアサートします。

- 6と7をN-1回繰り返します。

- マスタは STOP 条件を生成します。

### **BURST WRITE**

図 9. バースト書込みシーケンス

### 1バイト読出し

この動作では、マスタは1つのアドレスと2つのデータ・バイトをスレーブ・デバイスに送信し、スレーブ・デバイスから1つのデータ・バイトを受信します(図 10)。以下の手続きは、1 バイト読出しの動作を示すものです。

- マスタは START 条件を送信します。

- マスタは7ビットのスレーブ・アドレスに続けて書込みビット (ロー・レベル) を送信します。

- 指定アドレスのスレーブが、データ・ラインに ACK をアサートします。

- マスタは8ビットのレジスタ・アドレスを送信します。

- スレーブは、このアドレスが有効であればデータ・ラインに ACK をアサートします (無効であれば NACK)。

- マスタは反復 START 条件を送信します。

- マスタは7ビットのスレーブ・アドレスに続けて読出しビット(ハイ・レベル)を送信します。

- 指定アドレスのスレーブが、データ・ラインに ACK をアサートします。

- スレーブは8つのデータ・ビットを送信します。

- マスタがデータ・ラインに NACK をアサートします。

- マスタは STOP 条件を生成します。

#### **READ SINGLE BYTE**

図 10.1 バイト読出しシーケンス

#### バースト読出し

この動作では、マスタは 1 つのアドレスと 2 つのデータ・バイトをスレーブ・デバイスに送信し、スレーブ・デバイスから複数のデータ・バイトを受信します(図 11)。以下の手続きは、バースト・バイト読出しの動作を示すものです。

- マスタは START 条件を送信します。

- マスタは7ビットのスレーブ・アドレスに続けて書込みビット(ロー・レベル)を送信します。

- 指定アドレスのスレーブが、データ・ラインに ACK をアサートします。

- ▼スタは8ビットのレジスタ・アドレスを送信します。

- スレーブは、このアドレスが有効であればデータ・ラインに ACK をアサートします(無効であれば NACK)。

- マスタは反復 START 条件を送信します。

- マスタは7ビットのスレーブ・アドレスに続けて読出しビット (ハイ・レベル) を送信します。

- スレーブがデータ・ラインに ACK をアサートします。

- スレーブは8つのデータ・ビットを送信します。

- マスタがデータ・ラインに ACK をアサートします。

- 9と10をN-2回繰り返します。

- スレーブが最後の8つのデータ・ビットを送信します。

- マスタがデータ・ラインに NACK をアサートします。

- マスタは STOP 条件を生成します。

#### **BURST READ**

図 11. バースト読出しシーケンス

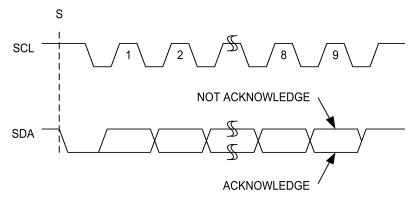

#### アクノレッジ・ビット

データ転送は、アクノレッジ・ビット(ACK)もしくはノット・アクノレッジ・ビット(NACK)でアクノレッジされます。マスタと MAX77348 の両方が ACK ビットを生成します。ACK を生成するためには、9番目のクロック・パルスの立上がりエッジより前に SDA を ローに引き下げて、9番目のクロック・パルスのハイ期間の間ローに保持します(図 12)。NACK を生成するためには、9番目のクロック・パルスの立上がりエッジより前に SDA をハイの状態とし、9番目のクロック・パルスのハイ期間の間ハイのままにします。NACK ビットをモニタすることによりデータ転送が成功しなかったことを検出できます。

図 12. アクノレッジ・ビット

### クロック・ストレッチング

一般的に、PC バスのクロック信号生成はマスタ・デバイスが担当します。PC 仕様では、速度の遅いスレーブ・デバイスがクロック・ラインをローに保つことによってクロック信号を変化させることを許容しています。スレーブ・デバイスがクロック・ラインをローに保つ動作は、クロック・ストレッチングと呼ばれます。MAX77348 は、クロック・ラインをローに保つクロック・ストレッチング動作はいかなる形でも使用しません。

### ジェネラル・コール・アドレス

MAX77348 は I<sup>2</sup>C の仕様である「ジェネラル・コール・アドレス」には対応していません。MAX77348 が「ジェネラル・コール・アドレス (00000000b)」を認識しても、アクノレッジ(A)を発行しません。

## レジスタ・マップ

#### **MAX77348**

| ADDRESS              | NAME             | MSB          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |          |              |              |                     | LSB            |

|----------------------|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|--------------|--------------|---------------------|----------------|

| Global Configuration |                  |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |          |              |              |                     |                |

| 0x00                 | CHIPID[7:0]      |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | BUCK_    | I[7:0]       |              |                     |                |

| 0x01                 | CFG0[7:0]        | EN           | RAMPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FAST      | ZCCMPDIS | LOWEMI       | MODE         | ACTDSC              | PSVDSC         |

| 0x02                 | CFG1[7:0]        | FHIGH        | HSH[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |          | VSET[5       | 5:0]         |                     |                |

| 0x03                 | CFG2[7:0]        |              | IPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SET2[3:0] |          |              | IPSET        | 1[3:0]              |                |

| 0x04                 | CFG3[7:0]        | RESERV<br>ED | PASTHRM<br>ODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SWOFRCIN  | RESERVED | RESERVE<br>D | INTEGEN      | IPADPT<br>DIS       | FETSCALE       |

| 0x05                 | STATUS[7:0]      | RESERV<br>ED | RESERVE<br>D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RESERVED  | RESERVED | RESERVE<br>D | RESERVE<br>D | OUTGO<br>OD         | INUVLO         |

| 0x06                 | INT[7:0]         | RESERV<br>ED | RESERVE<br>D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RESERVED  | RESERVED | RESERVE<br>D | RESERVE<br>D | OUTGO<br>ODINT      | INUVLOINT      |

| 0x07                 | INTMSK[7:0]      | RESERV<br>ED | RESERVE<br>D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RESERVED  | RESERVED | RESERVE<br>D | RESERVE<br>D | OUTGO<br>ODINT<br>M | INUVLOINT<br>M |

| 0x50                 | LOCKMSK[7:0]     | RESERV<br>ED | The service of the se |           |          |              |              |                     | BBLCK          |

| 0x51                 | LOCKUNLOCK [7:0] | PASSWD[7:0]  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |          |              |              |                     |                |

## レジスタの詳細

## CHIPID (0x0)

| BIT         | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------|---|-------------|---|---|---|---|---|---|--|--|

| Field       |   | BUCK_I[7:0] |   |   |   |   |   |   |  |  |

| Reset       |   | 0xCustom    |   |   |   |   |   |   |  |  |

| Access Type |   | Read Only   |   |   |   |   |   |   |  |  |

| ビットフィールド | ビット | 説明                               | デコード                                                        |

|----------|-----|----------------------------------|-------------------------------------------------------------|

| BUCK_I   | 7:0 | ChipID[7:0]は使用中のデバイスのバージョンを示します。 | Option A = $0x10$<br>Option B = $0x11$<br>Option C = $0x12$ |

### CFG0 (0x1)

| BIT         | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Field       | EN          | RAMPEN      | FAST        | ZCCMPDIS    | LOWEMI      | MODE        | ACTDSC      | PSVDSC      |

| Reset       | 0bCustom    | 0b1         | 0bCustom    | 0b1         | 0b0         | 0b0         | 0b0         | 0bCustom    |

| Access Type | Write, Read |

| ビットフィールド | ビット | 説明                                                                 | デコード                                                                                                                                                                                                        |

|----------|-----|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN       | 7   | 出力イネーブル。                                                           | 0x0 = Disable output<br>0x1 = Enable output<br>Reset value:<br>Option A, B = 0b1<br>Option C = 0b0                                                                                                          |

| RAMPEN   | 6   | ランプ・イネーブル。                                                         | $0x0 = Output \ voltage \ setting \ transition \ is$ performed without intermediate steps $0x1 = Output \ voltage \ setting \ increases \ are$ performed with a digital ramp of $50mV$ every $50\mu s$      |

| FAST     | 5   | 昇降圧プレトリガ・モード設定。<br>負荷過渡応答時の出力レギュレーション改善のため、<br>昇降圧部の自己消費電流を増加させます。 | $0x0 = Normal-Low\ Quiescent\ Current$ $Operation$ $0x1 = Fast\ response\ mode\ enabled-Quiescent$ $Current\ increased\ to\ 35\mu A\ (typ)$ $Reset\ Value:$ $Option\ A = 1$ $Option\ B = 0$ $Option\ C = 0$ |

# 超低 IQ、ロー・ノイズ 3.5W 昇降圧コンバータ

| ビットフィールド | ビット | 説明                                                                         | デコード                                                                                                                                             |

|----------|-----|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ZCCMPDIS | 4   | ゼロ交差コンパレータ・ディスエーブル。内部でラッチされ、EN=0のときにのみ変更可能です。                              | 0x0 = Enabled<br>0x1 = Disabled                                                                                                                  |

| LOWEMI   | 3   | 低EMIモード。<br>HVLX/LVLXの立上がり/立下がり時間を増加させる<br>ことにより、効率と引き換えにEMIを低減します。        | 0x0 = Normal Operation<br>0x1 = Increase rise/fall time on HVLX/LVLX<br>by three times                                                           |

| MODE     | 2   | 昇降圧動作モード。<br>レギュレータの動作モードを、昇降圧、降圧のみのいずれかで設定します。内部でラッチされ、EN = 0のときのみ変更可能です。 | 0x0 = Buck-Boost Mode<br>0x1 = Buck-Only Mode                                                                                                    |

| ACTDSC   | 1   | アクティブ放電制御。                                                                 | 0x0 = Buck-Boost not actively discharged<br>0x1 = Buck-Boost actively discharged on<br>shutdown                                                  |

| PSVDSC   | 0   | パッシブ放電制御。                                                                  | 0x0 = Buck-Boost not passively discharged 0x1 = Buck-Boost passively discharged on shutdown  Reset Value: Option A = 0 Option B = 1 Option C = 1 |

## CFG1 (0x2)

| BIT         | 7      | 6       | 5         | 4 | 3     | 2      | 1 | 0 |  |

|-------------|--------|---------|-----------|---|-------|--------|---|---|--|

| Field       | FHIGH  | SH[1:0] | VSET[5:0] |   |       |        |   |   |  |

| Reset       | 0b     | 11      | 0xCustom  |   |       |        |   |   |  |

| Access Type | Write, | Read    |           |   | Write | , Read |   |   |  |

| ビットフィールド | ビット | 説明                                                                                                                                                                                                                                                                                  | デコード                                                                                                                                                       |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FHIGHSH  | 7:6 | $f_{\text{HIGH}}$ のスレッショルド。<br>スイッチング周波数のスレッショルド $f_{\text{HIGH}}$ を選択します。昇降圧部のスイッチング周波数が $f_{\text{HIGH}}$ の上昇時スレッショルドを超えると、全てのブロックがオン( $I_{\text{Q}}$ が高い)になり、この状態は周波数が $f_{\text{HIGH}}$ の下降時スレッショルドに達するまで続きます。 $f_{\text{HIGH}}$ の交差時には $V_{\text{OUT}}$ に小さいグリッチが発生する可能性があります。 | 0x0 = 25kHz Rising/6.125kHz falling<br>0x1 = 35kHz Rising/8.25kHz falling<br>0x2 = 50kHz Rising/12.5kHz falling<br>0x3 = 100kHz Rising/25kHz falling       |

| VSET     | 5:0 | 出力電圧の設定。<br>2.5V~5.5Vの範囲で50mV刻みの線形スケールです。                                                                                                                                                                                                                                           | 0x00 = 2.50V<br>$0x01 - 0x2E = 2.50V + (VSET \times 0.05)V$<br>0x2F - 0x3F = 4.8V<br>Reset Value:<br>Option A = 0x28<br>Option B = 0x2A<br>Option C = 0x2A |

## CFG2 (0x3)

| BIT         | 7 | 6     | 5      | 4 | 3           | 2     | 1      | 0 |  |

|-------------|---|-------|--------|---|-------------|-------|--------|---|--|

| Field       |   | IPSET | 2[3:0] |   | IPSET1[3:0] |       |        |   |  |

| Reset       |   | 0xCu  | istom  |   | 0x8         |       |        |   |  |

| Access Type |   | Write | , Read |   |             | Write | , Read |   |  |

| ビットフィールド | ビット | 説明                                                                                                                                                                                                    | デコード                                                                                                                                                                                                                                                           |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPSET2   | 7:4 | 公称最大ピーク電流設定。<br>ピーク電流設定の詳細については、昇降圧モードのセクションを参照してください。FETSCALE = $0$ のとき、 $0$ mA(最小 $t_{ON}$ )~ $750$ mAの線形スケールで $50$ mA刻みです。FETSCALE = $1$ のときは、 $0$ mA(最小 $t_{ON}$ )~ $375$ mAの線形スケールで $25$ mA刻みです。 | $For \ FETSCALE = 0, \\ 0x0 = 0mA \ (minimum \ t_{ON}) \\ 0x1 - 0xF = (IPSET2 \times 50)mA \\ For \ FETSCALE = 1, \\ 0x0 = 0mA \ (minimum \ t_{ON}) \\ 0x1 - 0xF = (IPSET2 \times 25)mA \\ Reset \ Value: \\ Option \ A, \ C = A \\ Option \ B = 6$            |

| IPSET1   | 3:0 | 公称最大ピーク電流設定。<br>ピーク電流設定の詳細については、昇降圧モードのセクションを参照してください。FETSCALE = $0$ のとき、 $0$ mA(最小 $t_{ON}$ ) $\sim$ 750mAの線形スケールで50mA刻みです。FETSCALE = $1$ のときは、 $0$ mA(最小 $t_{ON}$ ) $\sim$ 375mAの線形スケールで25mA刻みです。   | $\begin{aligned} & For  FETSCALE = 0, \\ & 0x0 = 0mA  (minimum  t_{ON}) \\ & 0x1 - 0xE = (IPSET2 \times 50)mA \\ & 0xF = 750mA \\ & For  FETSCALE = 1, \\ & 0x0 = 0mA  (minimum  t_{ON}) \\ & 0x1 - 0xE = (IPSET2 \times 25)mA \\ & 0xF = 375mA \end{aligned}$ |

### CFG3 (0x4)

| BIT         | 7           | 6              | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------|-------------|----------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Field       | RESERVED    | PASTHR<br>MODE | SWOFRCIN    | RESERVED    | RESERVED    | INTEGEN     | IPADPTDIS   | FETSCALE    |

| Reset       | 0b1         | 0b0            | 0b1         | 0b0         | 0b0         | 0b1         | 0ь0         | 0bCustom    |

| Access Type | Write, Read | Write, Read    | Write, Read | Write, Read | Write, Read | Write, Read | Write, Read | Write, Read |

# 超低 IQ、ロー・ノイズ 3.5W 昇降圧コンバータ

| ビットフィールド   | ビット | 説明                                                                                                                                                                                                   | デコード                                                                                                                                                                                                                                                                                                     |

|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESERVED   | 7   | 予備。                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                          |

| PASTHRMODE | 6   | パス・スルー・モード。<br>レギュレータをバイパスし、 $V_{OUT}$ と $V_{IN}$ を直結します。<br>EN=0のときにのみイネーブルできます。                                                                                                                    | 0x0 = Pass Through Mode disabled<br>0x1 = Pass Through Mode enabled; Enable<br>only when EN = 0                                                                                                                                                                                                          |

| SWOFRCIN   | 5   | 強制スイッチオーバー。<br>デバイスの内部回路への電力供給方法を制御します。                                                                                                                                                              | $\begin{split} 0x0 &= \text{Switch-over supply forced to } V_{\text{OUT}} \\ \text{when } V_{\text{OUT}} &> V_{\text{OUT\_UVLO\_R}} \\ 0x1 &= \text{Switch-over supply forced to } V_{\text{IN}}. \end{split}$                                                                                           |

| RESERVED   | 4   | 予備。0を返します。                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                          |

| RESERVED   | 3   | 予備。0を返します。                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                          |

| INTEGEN    | 2   | 積分器イネーブル。<br>積分器をディスエーブルすると、負荷レギュレーション誤差と引き換えに、負荷過渡応答時のセトリング時間を改善できます。内部でラッチされ、EN = 0のときにのみ変更可能です。                                                                                                   | 0x0 = Integrator disabled $0x1 = $ Integrator enabled                                                                                                                                                                                                                                                    |