#### **MAX16193**

### 精度0.3%のデュアルチャンネル監視回路

#### 概要

MAX16193は、システムの電源レールの低電圧フォルトおよび過電圧フォルトをモニタする、超高精度のデュアルチャンネル・ウィンドウ・ディテクタ監視回路です。入力チャンネル1 (IN1)は、低いコア電圧レールを0.6V~0.9Vのスレッショルド範囲、±0.3%の精度でモニタし、入力チャンネル2 (IN2)は、比較的高いシステム・レールを0.9V~3.3Vのスレッショルド範囲、±0.3%の精度でモニタします。工場で±2%~±5%の範囲で調整された様々な低電圧/過電圧スレッショルドを使用して、多様な電源電圧や許容誤差に対応できます。

MAX16193は、産業用には8ピンの小型 (2mm x 3mm) 標準TDFN チップオンリード・パッケージで提供され、車載用には側面濡れ性パッケージで提供されます。動作可能温度範囲は、-40°C~ +125°Cです。

### アプリケーション

- ADAS (先進運転支援システム)

- プログラマブル・ロジック・コントローラ (PLC)

- FPGAベースのシステム

- 医療機器

- 複数電圧ASIC

- サーバー

- ストレージ機器

#### 機能と利点

● IN1のスレッショルド精度:±0.3%

● IN2のスレッショルド精度:±0.3%

● IN1のスレッショルド範囲: 0.6V~0.9V

● IN2のスレッショルド範囲: 0.9V~3.3V

● UV/OVモニタリング範囲: ±2%~±5%

● オープンドレイン/プッシュプルのリセット出力オプション

● システム・レベルで機能安全を確保

車載用:

• 8ピンTDFN、2mm x 3mm側面濡れ性フランク

AEC-Q100に適合

● 産業用:

・8ピンTDFN、2mm x 3mmパッケージ

● 温度範囲:-40°C~+125°C

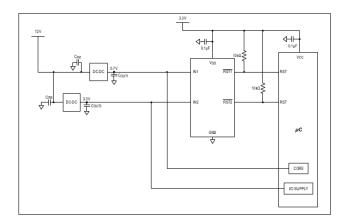

#### 標準アプリケーション回路

オーダー情報はデータシート末尾に記載されています。

## 精度0.3%のデュアルチャンネル監視回路

### 絶対最大定格

| $V_{DD}\sim GND$                                                            | 0.3V~+70V                |

|-----------------------------------------------------------------------------|--------------------------|

| IN1、IN2~GND                                                                 | 0.3V∼+6V                 |

| $\overline{\text{RST1}}$ 、 $\overline{\text{RST2}}$ (オープンドレイン出力) $\sim$ GND | 0.3V∼+6V                 |

| RST1、RST1 (プッシュプル出力) ~GND                                                   | $-0.3V \sim VDD + 0.3V$  |

| 入出力連続電流                                                                     | ±20mA                    |

| 連続消費電力 (TDFN) ((T823Y+3C、T823+3C)                                           | $T_A = +70^{\circ}C_{s}$ |

| +70℃以上では16.7mW/℃でディレーティング).                                                 | 1333.3mW                 |

| 動作温度範囲           | 40°C~+125°C |

|------------------|-------------|

| ジャンクション温度        | +150°C      |

| はんだ処理温度(リフロー)    | +260°C      |

| 保存温度範囲           | 65°C~+150°C |

| リード温度(はんだ処理、10s) | +300°C      |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様 の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信 頼性に影響を与えます。

## パッケージ情報

| Package Code                                           | T823Y+3C         | T823+3C        |  |  |

|--------------------------------------------------------|------------------|----------------|--|--|

| Outline Number                                         | <u>21-100417</u> | <u>21-0174</u> |  |  |

| Land Pattern Number                                    | <u>90-0091</u>   | <u>90-0091</u> |  |  |

| Thermal Resistance, Four Layer Board:                  |                  |                |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 60°C/W           | 60°C/W         |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 11°C/W           | 11°C/W         |  |  |

最新のパッケージ外形情報およびランド・パターン (フットプリント) については、パッケージ一覧を参照してください。パッケージ・コードの「+」、「#」、「-」は、RoHSステータスのみを示しています。パッケージ図面には異なるサフィックスが表示される場合がありますが、図面はRoHSステータスに関係なくパッケージに固有のものです。

パッケージの熱抵抗は、JEDEC仕様JESD51-7に記載の方法により、4層基板を用いて求めたものです。パッケージの熱に関する考慮事項の詳細については、ICパッケージの熱特性評価を参照してください。

## 電気的特性

(特に指定のない限り、 $V_{DD}=1.7V\sim5.5V$ 、 $T_A=T_J=-40^{\circ}C\sim+125^{\circ}C$ 。特に指定のない限り、代表値は通常条件下で $V_{DD}=3.3V$ 、 $V_{INI}=0.9V$ 、 $V_{IN2}=3.280V$ 、 $T_A=+25^{\circ}C$ での値です。)

| PARAMETER                           | SYMBOL                      | CONDITIONS                                              | MIN TYP |      | MAX  | UNITS |

|-------------------------------------|-----------------------------|---------------------------------------------------------|---------|------|------|-------|

| POWER SUPPLY                        |                             |                                                         |         |      |      |       |

| Operating Voltage<br>Range          | V <sub>DD</sub>             | Output guaranteed to be at known state 1.7 5.           |         | 5.5  | V    |       |

| Minimum Supply<br>Voltage           | V <sub>DD</sub>             | RST1 and RST2 are guaranteed to be at a known logic 1.1 |         |      | V    |       |

| Supply Current                      | I <sub>DD</sub>             | RST1 and RST2 not asserted                              |         | 50   | 100  | μA    |

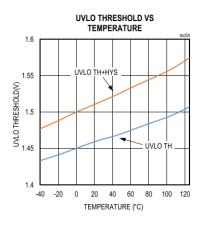

| Undervoltage Lockout<br>Threshold   | V <sub>UVLO</sub>           | V <sub>DD</sub> rising                                  | 1.30    | 1.50 | 1.68 | V     |

| Undervoltage Lockout<br>Hysteresis  | V <sub>UVLO_HYS</sub>       | V <sub>DD</sub> falling                                 |         | 47   |      | mV    |

| INPUT VOLTAGE (IN1 A                | INPUT VOLTAGE (IN1 AND IN2) |                                                         |         |      |      |       |

| IN1 Input Voltage<br>Range (Note 1) | V <sub>IN1</sub> NOM        |                                                         | 0.6     |      | 0.9  | V     |

| IN2 Input Voltage<br>Range (Note 1) | V <sub>IN2_NOM</sub>        |                                                         | 0.9     |      | 3.3  | V     |

# 精度0.3%のデュアルチャンネル監視回路

(特に指定のない限り、 $V_{DD}=1.7V\sim5.5V$ 、 $T_A=T_J=-40^{\circ}C\sim+125^{\circ}C$ 。特に指定のない限り、代表値は通常条件下で $V_{DD}=3.3V$ 、 $V_{INI}=0.9V$ 、 $V_{IN2}=3.280V$ 、 $T_A=+25^{\circ}C$ での値です。)

| PARAMETER                                                   | SYMBOL               | CONDITIONS                                                                                                      | MIN                      | TYP  | MAX  | UNITS                       |

|-------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------|------|------|-----------------------------|

| Undervoltage/Overvolta<br>ge Threshold<br>Programming Range | TOL                  | Reset occurs when V <sub>IN</sub> falls outside of V <sub>IN_NOM</sub> x (1±TOL) ±2                             |                          |      | ±5   | % of<br>V <sub>IN_NOM</sub> |

| INPUT THRESHOLD ACC                                         | CURACY               |                                                                                                                 |                          |      |      | -                           |

| IN1/IN2 Overvoltage<br>Threshold Accuracy                   | V <sub>OVTH_</sub> A | V <sub>IN1</sub> /V <sub>IN2</sub> rising, V <sub>OVTH</sub> = V <sub>IN_NOM x</sub> (1+TOL%)                   | -0.3 +0                  |      |      | %                           |

| IN1/IN2 Undervoltage<br>Threshold Accuracy                  | V <sub>UVTH_</sub> A | V <sub>IN1</sub> / V <sub>IN2</sub> falling, V <sub>UVTH</sub> = V <sub>IN_NOM x</sub><br>(1 - TOL%)            | -0.3                     |      | +0.3 | %                           |

| Undervoltage/Overvolta<br>ge Hysteresis                     | V <sub>HYS</sub>     |                                                                                                                 |                          | 0.15 |      | %V <sub>TH</sub>            |

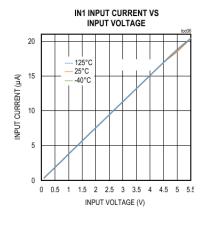

| In most Commont                                             | I <sub>IN1</sub>     | V <sub>IN1</sub> = V <sub>IN1_NOM</sub>                                                                         |                          | 3    | 6    | μA                          |

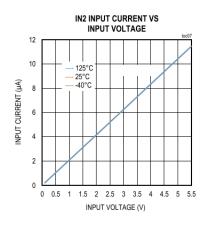

| Input Current                                               | I <sub>IN2</sub>     | $V_{IN2} = V_{IN2\_NOM}$                                                                                        |                          | 6    | 12   | μA                          |

| RESET OUTPUT (RST1                                          | AND RST2)            |                                                                                                                 |                          |      |      |                             |

| Reset Timeout Period<br>Accuracy                            | t <sub>RP</sub>      | From time V <sub>IN</sub> _ enters<br>overvoltage/undervoltage threshold-<br>window to time RST_ goes high      | -20                      |      | +20  | %                           |

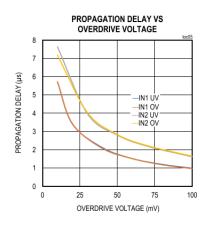

| IN1-to-RST1<br>Propagation Delay                            | t <sub>D</sub>       | (V <sub>UVTH</sub> + 1%) to (V <sub>UVTH</sub> - 1%)<br>or (V <sub>OVTH</sub> - 1%) to (V <sub>OVTH</sub> + 1%) |                          | 5    |      | μs                          |

| IN2-to-RST2<br>Propagation Delay                            | t <sub>D</sub>       | (V <sub>UVTH</sub> + 1%) to (V <sub>UVTH</sub> - 1%)<br>or (V <sub>OVTH</sub> - 1%) to (V <sub>OVTH</sub> + 1%) |                          | 5    |      | μs                          |

| OUTPUT VOLTAGE                                              |                      |                                                                                                                 |                          |      |      |                             |

|                                                             |                      | V <sub>DD</sub> ≥ 4.25V, I <sub>SINK</sub> = 1mA                                                                |                          |      | 0.1  |                             |

| Output Voltage Low                                          | $V_{OL}$             | V <sub>DD</sub> = 2.5V, I <sub>SINK</sub> = 250μA                                                               |                          |      | 0.1  | V                           |

|                                                             |                      | V <sub>DD</sub> = 1.2V, I <sub>SINK</sub> = 25μA                                                                |                          |      | 0.1  |                             |

| Output Voltage High                                         | Vou                  | V <sub>DD</sub> = 1.70V, I <sub>SOURCE</sub> = 200μA                                                            | 0.8 x<br>V <sub>DD</sub> |      |      | V                           |

| (Push-Pull)                                                 | VOH                  | V <sub>DD</sub> ≥ 4.5V, I <sub>SOURCE</sub> = 800μA                                                             | 0.8 x<br>V <sub>DD</sub> |      |      |                             |

Note 1: IN1およびIN2の入力電圧は、工場において、低電圧スレッショルドと過電圧スレッショルドの中間点に設定可能です。

Note 2: 限界値は、 $T_A = +25^{\circ}$ Cで100%テストされています。動作温度範囲および対応する電源電圧範囲にわたる限界値は、設計と特性評価によって裏付けられています。

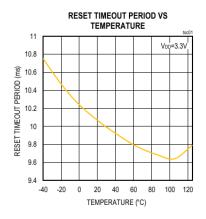

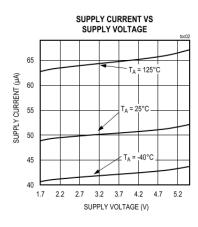

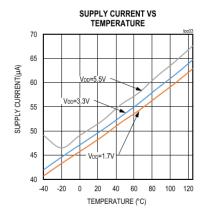

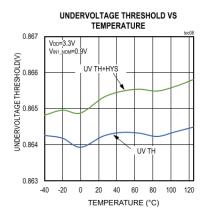

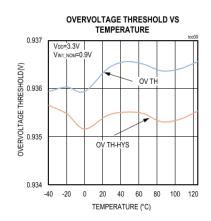

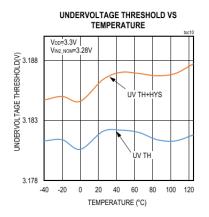

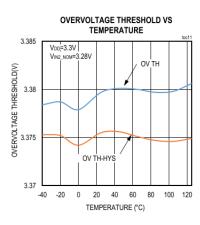

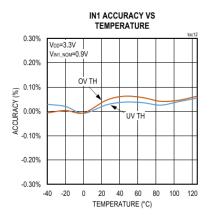

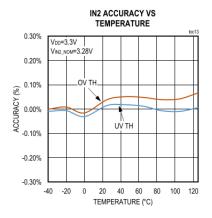

# 標準動作特性

(特に指定のない限り、 $V_{DD} = 1.70V \sim 5.5V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ )

# 精度0.3%のデュアルチャンネル監視回路

(特に指定のない限り、VDD = 1.70V~5.5V、TA = TMIN~TMAX)

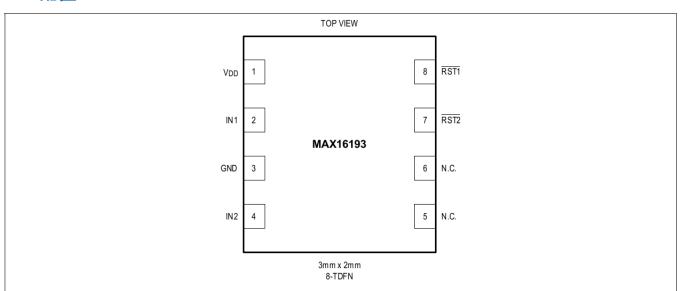

# ピン配置

# 端子説明

| 端子   | 名称       | 機能                                                                                                                                                                                                       |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | $V_{DD}$ | 電源入力。V <sub>DD</sub> は0.1μFのコンデンサを使用してグランドにバイパスします。                                                                                                                                                      |

| 2    | IN1      | モニタリング入力1。IN1は、公称入力スレッショルドを基準として電源レールの低電圧/過電圧フォルトをモニタします。IN1は0.6V~0.9Vの電源範囲をモニタします。VIN1が低電圧/過電圧スレッショルド・ウィンドウの範囲外になると、RST1がアサートされ、VIN1が低電圧/過電圧スレッショルド・ウィンドウの範囲内に収まった後リセット・タイムアウト時間が経過するまで、アサートされたままになります。 |

| 3    | GND      | グランド                                                                                                                                                                                                     |

| 4    | IN2      | モニタリング入力2。IN2は、公称入力スレッショルドを基準として電源レールの低電圧/過電圧フォルトをモニタします。IN2は0.9V~3.3Vの電源範囲をモニタします。VIN2が低電圧スレッショルドと過電圧スレッショルドの間のウィンドウから外れると、RST2がアサートされ、VIN2がこのウィンドウの範囲内に収まった後リセット・タイムアウト時間が経過するまで、アサートされたままになります。       |

| 5, 6 | N.C.     | 接続なし                                                                                                                                                                                                     |

| 7    | RST1     | アクティブローのオープンドレインまたはプッシュプル・リセット出力2。オープンドレイン・バージョンでは、 $RST2$ に10k $\Omega$ のプルアップ抵抗を接続します。                                                                                                                 |

| 8    | RST2     | アクティブローのオープンドレインまたはプッシュプル・リセット出力1。オープンドレイン・バージョンでは、 $\overline{RST1}$ に10k $\Omega$ のプルアップ抵抗を接続します。                                                                                                      |

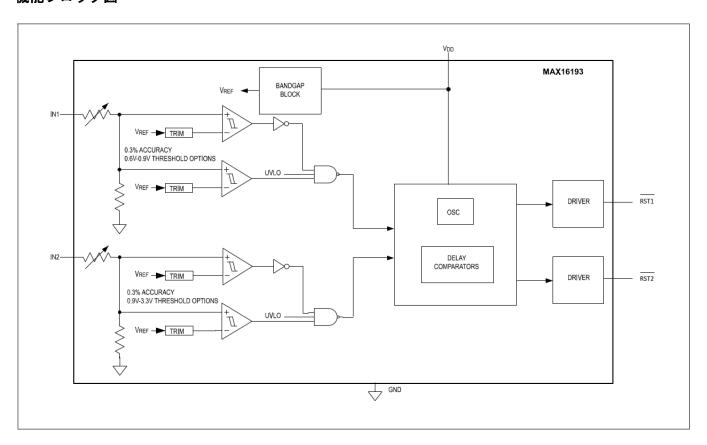

## 機能図

## 機能ブロック図

### 詳細

MAX16193は、デュアルチャンネル、精度0.3%のウィンドウ・ディテクタ監視回路で、システム内の2つの電源電圧をモニタします。 MAX16193では、公称入力電圧レベルを工場で調整済みで、低電圧および過電圧スレッショルド間のウィンドウを工場にて±2%~±5%の範囲で調整済みです。オーダー情報の表に記載のないスレッショルドについては、アナログ・デバイセズにお問い合わせください。

#### リセット・タイムアウト時間

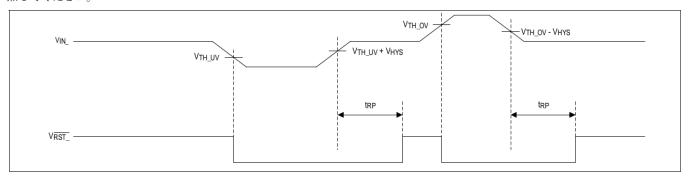

アクティブローのオープンドレイン・リセット出力RSTI およびRST2 は、それぞれの入力電圧が工場調整済みの低電圧と過電圧のウィンドウから外れた場合に、ローにアサートされます。対応するリセット出力は、設定されたウィンドウ・スレッショルド内に入力電圧が収まってからリセット・ライムアウト時間が経過した後に、デアサートされます。パワーアップ時は、VDDがUVLOを超えた後リセット・タイムアウト時間の間、リセットがアサートされたままになります。リセット出力は、工場で設定されたオープンドレインまたはプッシュプルのオプションで使用できます。オープンドレイン構成のリセット出力には、プルアップ抵抗が必要です。詳細については、図1を参照してください。

図1. リセット出力のタイミング図

## アプリケーション情報

#### 入力スレッショルドとヒステリシスの設定

MAX16193は、システム電源電圧の低電圧/過電圧ウィンドウのスレッショルドをモニタします。システム電源の許容誤差条件に応じて、低電圧/過電圧スレッショルドは、選択された公称入力スレッショルド電圧を基準に±2%~±5%の範囲で工場にて調整できます。低電圧/過電圧スレッショルド・レベルを±0.3%のスレッショルド精度で定めるための、詳細な計算方法を以下に示します。

$V_{IN NOM} = 0.9V$

$TOL = \pm 3\%$

$V_{UVTH} = V_{IN\_NOM} (1 - 3\% = 0.9V \times (1 - 0.03) = 0.873V$

$V_{OVTH} = V_{IN\_NOM} (1 + 3\%) = 0.9 V x (1 + 0.03) = 0.927 V$

ここで、 $V_{\text{IN\_NOM}}$ は選択された公称入力スレッショルド電圧、TOLは入力の許容誤差、 $V_{\text{UVTH}}$ は低電圧スレッショルド電圧、 $V_{\text{OVTH}}$ は過電圧スレッショルド電圧です。

MAX16193は、動作温度範囲および電源電圧範囲にわたり、±0.3%の精度で電源電圧をモニタします。精度の範囲は以下のとおりです。

$V_{UVTH\_A} = V_{IN\_NOM} (1 - 3\% \pm 0.3\%)$

$V_{OVTH\_A} = V_{IN\_NOM} (1 + 3\% \pm 0.3\%)$

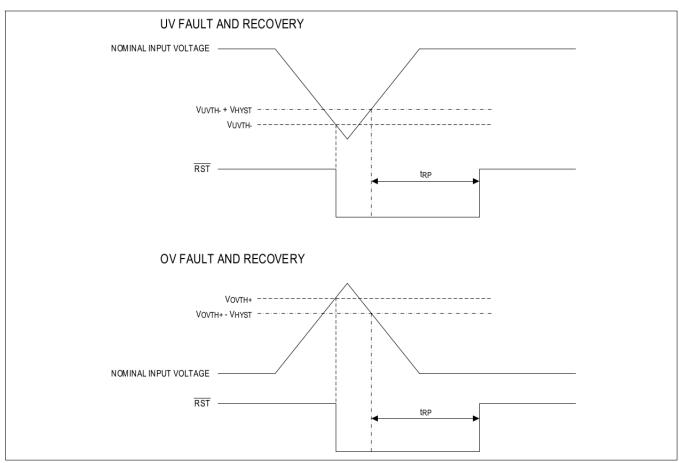

VuvrH\_Aは低電圧スレッショルドの精度範囲、VovrH\_Aは過電圧スレッショルドの精度範囲です。詳細については図2を参照してください。

図2. 低電圧/過電圧スレッショルド精度

ヒステリシスは、電圧モニタにノイズ耐性を付加し、モニタ対象の電圧がスレッショルドのトリップ電圧付近になった場合に繰り返しトリガが生じることによる発振を防止します。

スレッショルド・ヒステリシスは次式を使って計算します。

$V_{\text{IN\_NOM}} = 0.9 V$

ヒステリシス = 0.15%

$V_{HYST} = 0.9V \times 0.15\% = 0.00135V$

図3. 低電圧/過電圧スレッショルドのヒステリシス

### 電源のバイパス/ノイズ耐性

MAX16193は1.7V~5.5Vの電源で動作します。 $0.1\mu$ Fのコンデンサをできるだけデバイスの近くに配置して、 $V_{DD}$ をグランドにバイパスします。更にコンデンサを追加することで、過渡耐圧を向上させることができます。

### 選択ガイド表

| PART NUMBER        | IN1/IN2<br>THRESHOLD<br>VOLTAGE | IN1/IN2<br>TOLERANCE | IN1/IN2<br>ACCURACY | IN1/IN2<br>HYSTERESIS | RESET<br>OUTPUT | RESET<br>TIMEOUT |

|--------------------|---------------------------------|----------------------|---------------------|-----------------------|-----------------|------------------|

| MAX16193ATA00/VY+T | 0.9V/3.280V                     | 4%/3%                | 0.3%/0.3%           | 0.15%/0.15%           | Open Drain      | 10ms             |

| MAX16193BATA00+T   | 0.9V/3.280V                     | 4%/3%                | 0.3%/0.3%           | 0.15%/0.15%           | Open Drain      | 10ms             |

| MAX16193CATA00+T   | 0.9V/3.280V                     | 4%/3%                | 0.3%/0.3%           | 0.15%/0.15%           | Push-Pull       | 10ms             |

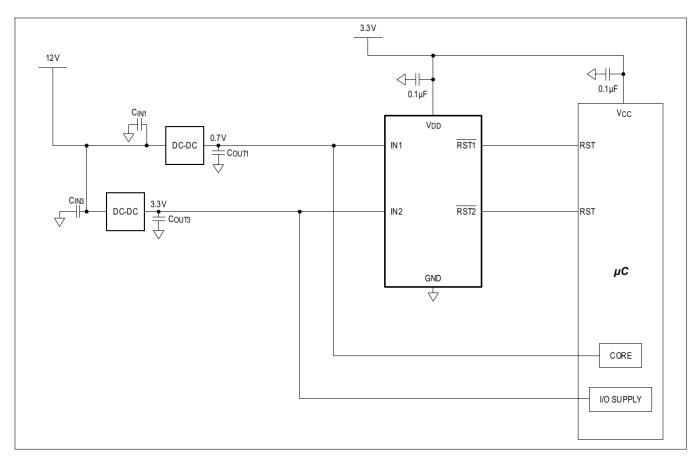

# 標準アプリケーション回路

プッシュプル・リセット出力のMAX16193Cは、 $\overline{RST}_{\_}$ ピンにプルアップ抵抗を接続する必要はありません。

# オーダー情報

| PART NUMBER        | TEMP RANGE      | PIN-PACKAGE       |

|--------------------|-----------------|-------------------|

| MAX16193ATA00/VY+T | -40°C to +125°C | 8 TDFN (T823Y+3C) |

| MAX16193BATA00+T   | -40°C to +125°C | 8 TDFN (T823+3C)  |

| MAX16193CATA00+T   | -40°C to +125°C | 8 TDFN (T823+3C)  |

+は鉛 (Pb) フリー/ROHS準拠のパッケージであることを示します。

T=テープ&リール

/V = 車載用認定製品。

Y=側面濡れ性パッケージ。

## チップ情報

プロセス:BiCMOS

## 改訂履歴

| 版数 | 改訂日   | 説明                                                                            | 改訂ページ |

|----|-------|-------------------------------------------------------------------------------|-------|

| 0  | 03/22 | 市場投入のためのリリース                                                                  | _     |

| 1  | 09/23 | 概要、アプリケーション、機能と利点、絶対最大定格、パッケージ情報の表、電気的特性、標準動作特性、選択ガイド表、標準アプリケーション回路、オーダー情報を更新 | 1~10  |